为什么需要复位电路

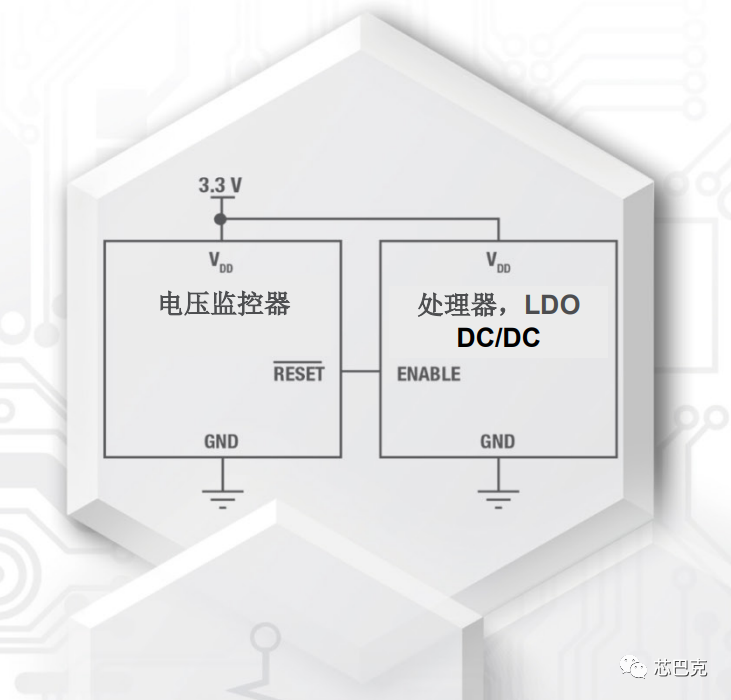

数字电路只有0和1两种状态,在电路刚上电或电路工作不稳定时,数字电路的输出是不稳定的,这时需要给电路一个激励,使电路进入一个预先设定好的状态。复位电路的作用就是监控电路,并在需要的时候发出这样的激励。

常见的复位电路设计中的问题可分为以下几类:未提供复位信号、复位时序不正确、复位信号驱动能力不足。

未提供复位信号

一般复杂高速电路会提供总复位电路,但有时电路中某些模块的复位并不是由系统的总复位提供。这种情况之下,需要在系统完成总复位后,再使能特定的复位信号,以实现特定模块的复位。

例如,某单板选用POWERPC电路模块作为CPU子系统,在系统复位完成后,通过软件测试CPU所挂的DDR2 SDRAM DIMM条,发现无法完成读写操作。

tips:DIMM条,SIMM条名词解释:Dual-Inline-Memory-Modules,即双列直插式存储模块。SIMM(single in-line memory module,单边接触内存模组),就是主板上常见的内存条。

经分析系统原理图发现 DDR2 SDRAM DIMM条的复位信号与GPIO29相连,而代码中并不包括对GPIO29的配置。而与SRAM、SDRAM、DDR SDRAM、DDR2 SDRAM不同,DIMM上有多个DDR存储器,需要时钟驱动器,而此时钟驱动器需要使能信号,这个使能信号由DIMM复位信号充当,故当将gpio29的配置功能加入后,CPU即可正常读写存储器。

在复杂的高速电路设计中,尤其是涉及主控板和业务板的设计中,通常要求带电插拔业务板,这个事件将由一个中断信号通知主控板,主板查询到业务板插入后,需要发出一个复位信号单独对此业务板进行复位,而不影响其他业务板和主控板的工作,故此复位信号不能用系统复位信号,而应该由cpu控制器的GPIO驱动输出。所以除了系统复位信号,还应提供各功能模块的专用复位信号。

复位时序不正确

复位时序问题产生的原因有两个:发送方和接收方

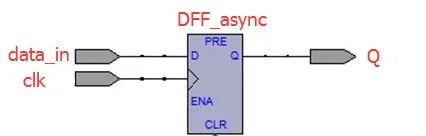

发送方的问题主要出在没有在正确的时间输出正确的波形。设计可编程逻辑的设计,器件选型完成后,应该制定单板总体复位框图,并对框图进行仔细审核。

接收方的问题考虑复位信号到达接收端有没有出现波形失真。主要衡量发送方和接收方的波形差别,由于波形的差别,可能导致复位时序出错。考虑两个环节:一是在传输路径上有没有经过驱动或转换器件,这些器件带来的延时是多少;二是传输路径上的容性是否太大以至于改变了信号边沿的斜率。

复位信号驱动能力不足

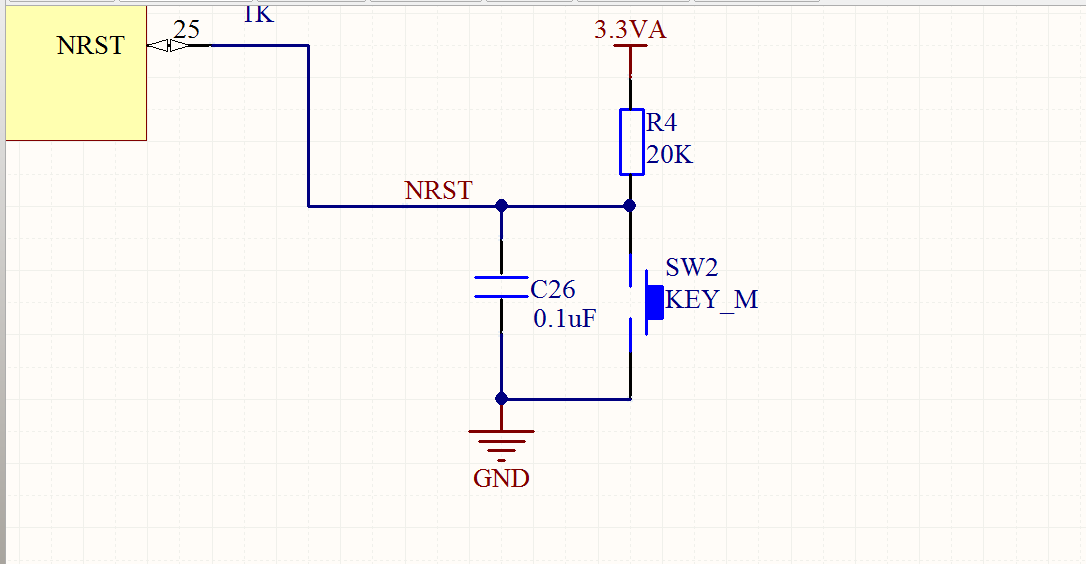

当复位信号在PCB上走线过长,或接收端容性过大,这些因素都可能导致复位信号驱动能力不足,具体表现为信号边沿过缓,不能满足某些芯片对复位信号边沿速率的要求。

-

复位电路

+关注

关注

13文章

322浏览量

44599

原文标题:高速电路中的复位设计

文章出处:【微信号:murata-eetrend,微信公众号:murata-eetrend】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

ARM单片机的复位电路设计

51单片机几种实用的复位电路设计

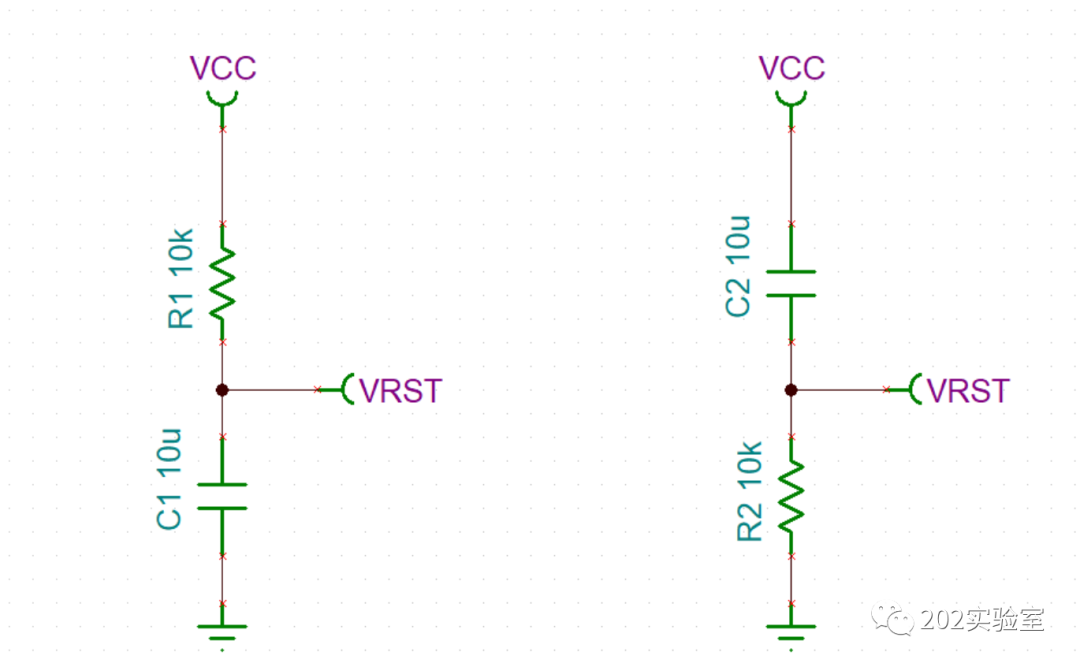

STM32复位电路用复位芯片和阻容复位电路区别

复位电路静电整改案例分享(一)——交换机复位电路

深度了解复位电路设计

深度了解复位电路设计

评论