何为信号完整性:信号完整性(Signal Integrity,简称SI)是指在信号线上的信号质量。差的信号完整性不是由某一单一因素导致的,而是板级设计中多种因素共同引起的。当电路中信号能以要求的时序、持续时间和电压幅度到达接收端时,该电路就有很好的信号完整性。当信号不能正常响应时,就出现了信号完整性问题。

信号完整性包含:

1、波形完整性(Waveform integrity)

2、时序完整性(Timing integrity)

3、电源完整性(Power integrity)

信号完整性分析的目的就是用最小的成本,最快的时间使产品达到波形完整性、时序完整性、电源完整性的要求。

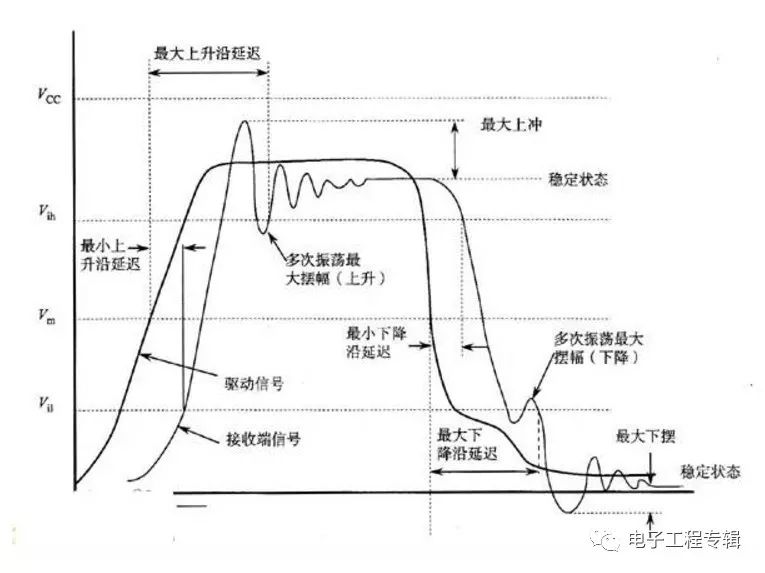

我们知道:电源不稳定、电源的干扰、信号间的串扰、信号传输过程中的反射,这些都会让信号产生畸变,看下面这张图,你就会知道理想的信号,经过:反射、串扰、抖动,最后变成什么鬼。

如果你的示波器测试上这样的信号,你一定会问,为什么会这样,怎么去解决。

首先我们说一下反射:

反射--初始波

当驱动器发射一个信号进入传输线时,信号的幅值取决于电压、缓冲器的内阻和传输线的阻抗。驱动器端看到的初始电压决定于内阻和线阻抗的分压。

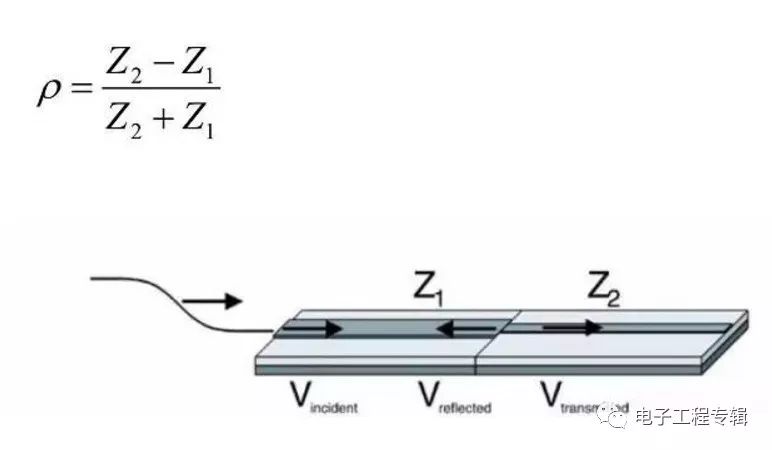

反射系数,其中-1≤ρ≤1

当ρ=0时无反射发生

当ρ=1(Z 2 =∞,开路)时发生全正反射

当ρ=-1(Z 2 =0,短路)时发生全负反射

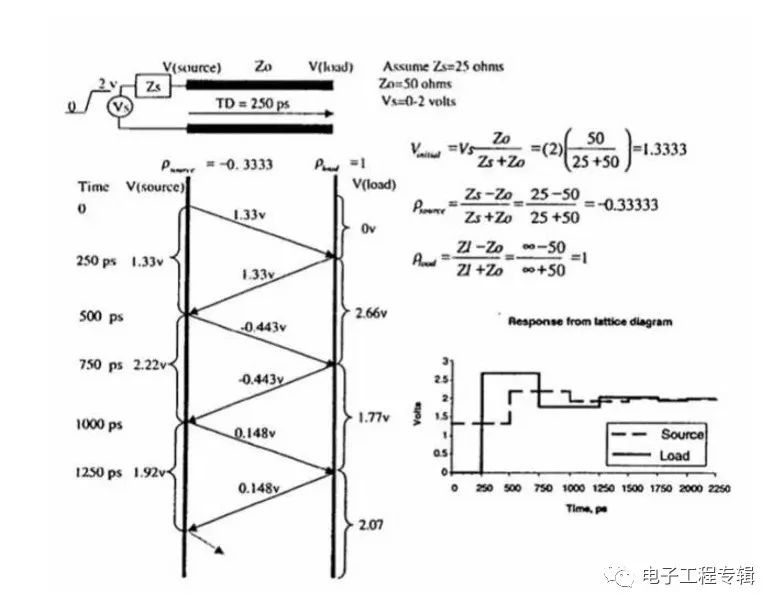

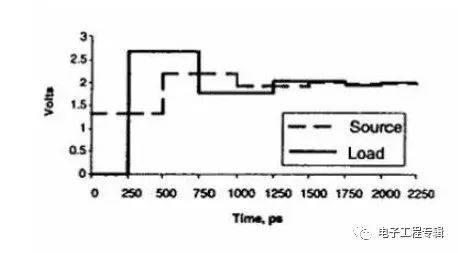

初始电压,是源电压Vs(2V)经过Zs(25欧姆)和传输线阻抗(50欧姆)分压。

Vinitial=1.33V

后续的反射率按照反射系数公式进行计算

源端的反射率,是根据源端阻抗(25欧姆)和传输线阻抗(50欧姆)根据反射系数公式计算为-0.33;

终端的反射率,是根据终端阻抗(无穷大)和传输线阻抗(50欧姆)根据反射系数公式计算为1;

我们按照每次反射的幅度和延时,在最初的脉冲波形上进行叠加就得到了这个波形,这也就是为什么,阻抗不匹配造成信号完整性不好的原因。

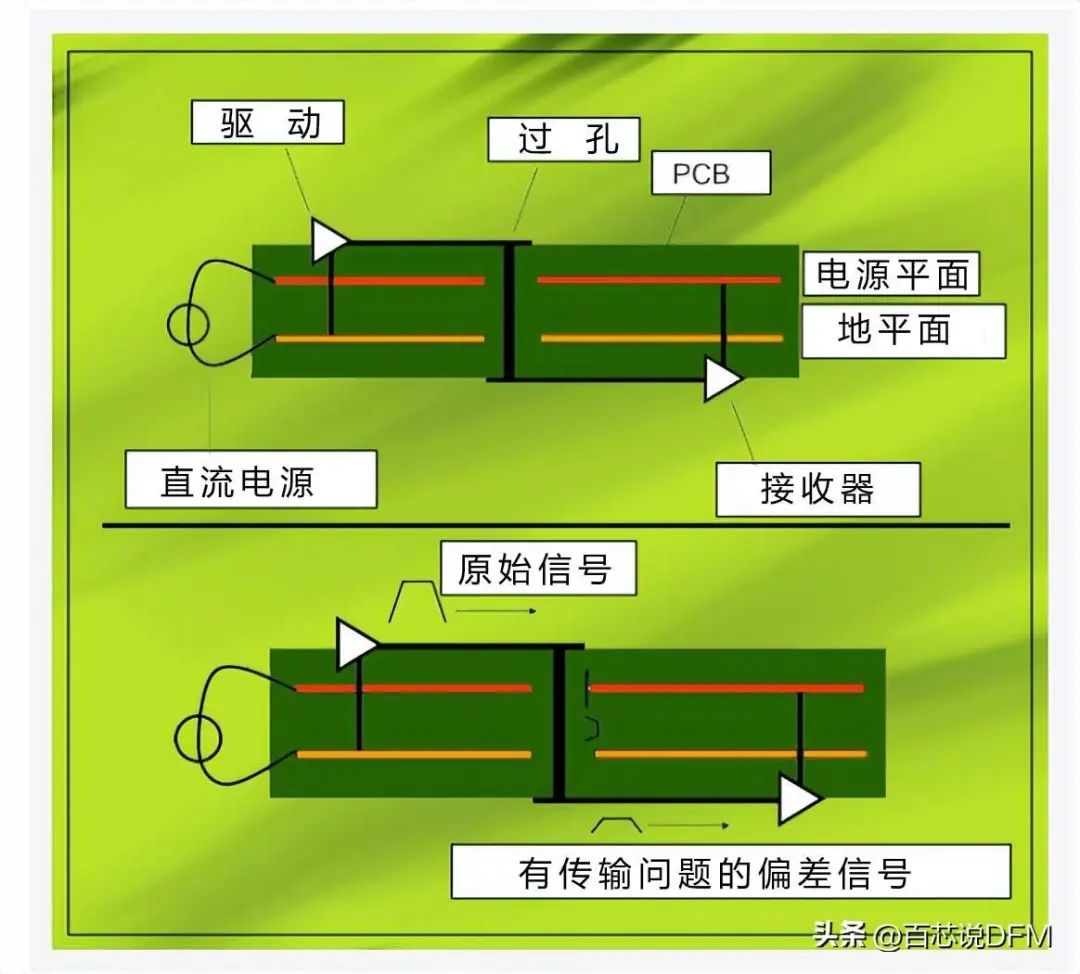

由于连接的存在、器件管脚、走线宽度变化、走线拐弯、过孔会使得阻抗不得不变化。所以反射也就不可避免。

电压后者电流有变化,自然就会往外辐射电磁波

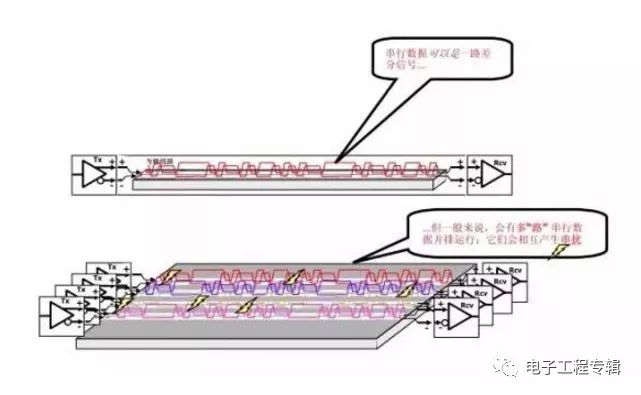

串扰是指当信号在传输线上传播时,因电磁耦合对相邻的传输线产生的不期望的电压噪声。

串扰是由电磁耦合引起的,耦合分为容性耦合和感性耦合两种。

容性耦合是由于干扰源(Aggressor)上的电压变化在被干扰对象(Victim)上引起感应电流从而导致的电磁干扰;

而感性耦合则是由于干扰源上的电流变化产生的磁场在被干扰对象上引起感应电压从而导致的电磁干扰。因此,信号通过一导体时会在相邻的导体上引起两类不同的噪声信号:容性耦合信号和感性耦合信号。

感性耦合:

容性耦合:

-

信号完整性

+关注

关注

68文章

1405浏览量

95460 -

反射

+关注

关注

0文章

67浏览量

15862 -

串扰

+关注

关注

4文章

189浏览量

26943

原文标题:串扰和反射能让信号多不完整?

文章出处:【微信号:eet-china,微信公众号:电子工程专辑】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

信号完整性的定义、干扰因素及解决方法详解

信号完整性的定义、干扰因素及解决方法详解

评论