刚好在知乎上看到这个问题如何用FPGA加速卷积神经网络CNN,恰巧我的硕士毕业设计做的就是在FPGA上实现CNN的架构,在此和大家分享。

先说一下背景,这个项目的目标硬件是Xilinx的PYNQ。该开发板加载了Linux Ubuntu操作系统,可以在CPU上运行现有的Python CNN架构如Caffe和Theano。本设计旨在用PYNQ加载的ZYNQ FPGA对于CNN核心计算进行硬件加速,以达到对于大规模信息流进行大吞吐量CNN处理。

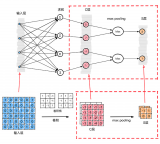

该设计结构可以分为CPU端(前端)和FPGA端(后端)两部分。前端使用的是Python,用来与其他软件项目进行交互。前端将数据以数据流的形式由DDR传输到FPGA kernel。后端的FPGA硬件设计使用的是Synchronous Dataflow Paradigm。在这个结构之下,数据流以AXI-Stream的协议穿梭于每一个CNN层。每一个层都使用并行结构加上高性能流水线,使整体吞吐量效率达到一个非常可观的水平。

上图为实现LeNet-5的硬件结构示意图。对于LeNet-5,该设计达到了1.88GOP/S的吞吐量,与PYNQ上的DUAL CORE ARM CPU相比加速约32倍。目前该架构可运行LeNet和CIFAR10,有教程。

这个项目结构比较简单,适合FPGA初学者作为研究起点使用。感兴趣的话,可以以这个架构为基础设计几个CNN的应用,或者在它的基础上进行优化和再创造。

-

FPGA

+关注

关注

1629文章

21729浏览量

603037 -

神经网络

+关注

关注

42文章

4771浏览量

100720

发布评论请先 登录

相关推荐

【PYNQ-Z2申请】基于PYNQ的卷积神经网络加速

卷积神经网络如何使用

卷积神经网络简介:什么是机器学习?

卷积神经网络CNN图解

简单快捷地用小型Xiliinx FPGA加速卷积神经网络CNN

简单快捷地用小型Xiliinx FPGA加速卷积神经网络CNN

评论