其实工作了这么久后,真的发现现在的工程师太依赖软件库了,做一个成熟的项目可以,稍微新一点,没做过的,没现成的代码的项目,就不敢接了。一来是风险控制,二来还是威廉希尔官方网站 太菜!

其实威廉希尔官方网站 很简单,超级简单,大学做实验时候,在开发板,做什么红外报警,32位密码锁,还有无绳电话等,拉一套学长的代码,调试一下,烧到板子,就OK了。用带我的张老师的话说“加个壳,你们就可以注册个商标创业开公司了。”

以前觉得威廉希尔官方网站 NB,销售LJ。现在回头一看,销售才是王道啊,威廉希尔官方网站 什么的,拉个虎皮就能出产品了,慢慢升级质量也会上去。只要有销路,土豪做朋友。

吐槽完了,还是出点干货吧。现在的COMS sensor 完全不顾人眼最适的800W像素,1200W,1300W不停向上搞。那么问题来了:这么高像素的IC,要达到30帧/S,这传输速率要多给力啊,所以,mipi传输协议打败了串口,并口的传输方式,成为现在的新宠。

下面就介绍一下mipi协议及一些常规故障排除。不要问我为什么懂,毕竟COMS芯片FAE的工作不是白做的,现在呆过的第一家公司已经上市了,祝福啊。对于在上市前夕离开开公司的事情,我真是一点不后悔啊。%>_<%

MIPI ——Mobile industry process interface多家移动开发或者应用商共同筹划接口标准联盟节约成本,加快产品开发速度内容丰富,显示、照相机、电源管理、射频、存储接口等等

CIS(cmos image sensor)中仅用到了mipi协议中的csi-2(camera serial interface二代,标识生成要求)和D-phy(物理层,输出通道要求)

Camera端做transmitter,平台端做receiver简而言之 mipi的作用就是:1.数据并行转换成串行;2.功能复用,节约传输线;3.相对提高传输品质和速度;4.增加传输距离;5.适用新的平台需求;

为什么mipi那么NB,下面对比一下就照了。

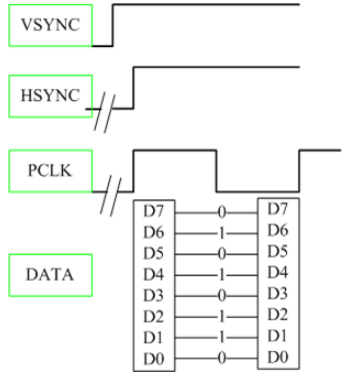

并口需要Vsync:帧同步信号Hsync:行同步信号和8条数据线,但这10根线,mipi只需要5根。所以,我行,我来!

Clock和 data中体现差分即低位先出,故如此表示,差分信号P高N低表1,P低N高表0.现在对mipi大概有点小小的概念了。再给你看看她的照片,保证你喜欢。MIPI 输出长什么样?

当当当当~~

帧头标识、帧尾标识(分别由vsync上升下降沿生成)行头标识、行尾标识(分别由hsync上升下降沿生成)有效数据长包。包含行标识,所以可以省略line_sync短包相对于并口传输,即是将vsync、hsync与数据共通道复用传输。

总之一句话,能用软件解决的一定不要动硬件,能动手的一定不要动嘴。人生哲理。什么?不要看PS过的照片!好吧,下面发个素颜照。

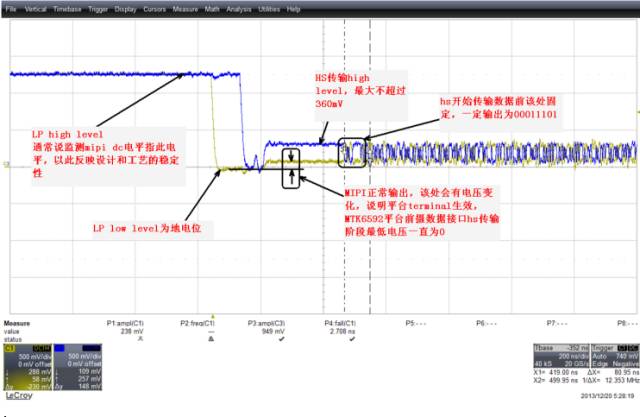

是不是美如画。而mipi的信号符合其通信协议,规定其起始电压在1.1~1.3V,等等,如下图(我比较懒,不服来辩)。这是其电气要求。

然后软件方面,如下图:

字节(byte)为基本传输单元,每个byte中有8位(bit)Sync dyte:用来同步数据开始,告知接下来为有效数据DATA TYPE:该包传输的是什么格式的数据YUV422(1E)/RAW8(2A)/RAW10(2B)WC(16bits)= PAYLOAD中的byte数量(即输出窗口的1行中有多少个字节,也即列数。注意raw10为列数的1.25倍,raw12为列数的1.5倍)ECC:校验datatype和wc是否出错Payload=image dataCSC:PAYLOAD数据传输校验*由于插入了许多数据标识,所以会影响hb或者vb的最小值MIPI DPHY 终端概念

mipi的信号线是一对差分线,理论上可以高电平传一个数据,低电平也传一个,速度又快,功耗又小。很多时候,平台端的mipi时序和Sensor端如果不匹配,就会出问题。硬件问题的话,就亮信号!

Term未连接情况信号时这样滴。正常的是这样滴:

Sensor输出在设计时已经考虑,应用时主要是FPC或者PCB走线影响通常要求:差分对内两线等长,尽量少折线,方向一致;差分对间地线走地,减小串扰;线上过孔最少;至少一侧有铺地;线长最长不超过20cm;尽量远离天线;目的:阻抗匹配、阻抗连续,减少信号损失,获得较高的信号完整性;减少信号间耦合,保证信号完整性;减少与其他射频信号的相互作用,保证各信号的质量;Settle count主要是hs_prepare+hs_zero时间与其匹配;通常设定T_settle count为T_(hs_prepare+hs_zero)/2;是平台设定参数,通常不改默认值,与pclk频率有关;

不匹配会引起的问题:卡顿;不出图;不规则滚屏、拍照分屏

调节方法:增大或者减小T_hs_prepare、hs_zero,参数最小值为1,有时需要调的很不可思议才可行,这是需要配成manual模式。

DDR采样,即在时钟的上升和下降沿均采集数据,保证高速传输又可以有效降低时钟频率,要求时钟和数据相位为正交关系。实际中因为负载差异,会限制时钟的建立速度,同时数据的不规律输出(不是确定的输出序列),所以对setup或者hold时间要求不同。可能造成误码,引起麻点,严重时会丢行。

数据传输速率,单位为bps(bit per second)

mipi_data=pclk_tot*10(raw10)=pclk_tot*8 (raw8)

pclk_tot=数字输出并行时钟pclk * 数字通道数Mmipi N通道,每通道数据率=mipi_data/NMipi时钟速度=每通道数据率/2= mipi_data/4

-

嵌入式开发

+关注

关注

18文章

1028浏览量

47566 -

MIPI

+关注

关注

11文章

310浏览量

48615

原文标题:嵌入式开发之mipi协议学习

文章出处:【微信号:qrsworld,微信公众号:嵌入式单片机】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

焊接机器人常见故障及排查

BGA封装常见故障及解决方法

航空插头常见故障的解决方法及拆卸技巧

mipi传输协议常见故障排查及解决

mipi传输协议常见故障排查及解决

评论