前言

前段时间某客户反馈,在使用STM32H7的FMC时,如果使能了D-CACHE就运行不正常。数据没有写到FMC外部的存储器里,FMC接口也没有波形。而不使能D-CACHE是工作则是正常的。

其实对于这个问题,如果了解STM32H7的架构的话,就很容易理解了。下面我们就来看一看到底是什么原因让客户觉得使能DCACHE后FMC就工作不正常了。

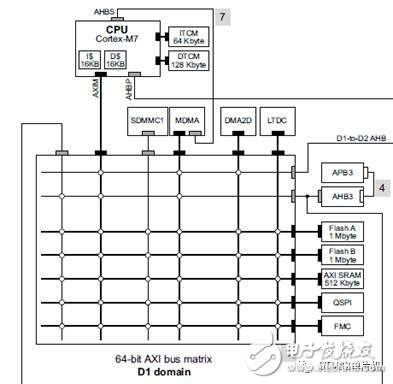

STM32H7的架构

下面是STM32H7架构图中和FMC相关的部分。从图中可以看到,STM32H7是基于Cortex-M7内核,在内部的Cortex-M7内核里带有一个16KB的D-CACHE和一个16KB的I-CACHE。内核通过AXIM总线连接到64位的AXI总线矩阵,再经过这个总线矩阵连接到FMC接口实现对外部存储器的访问。这里,当D-CACHE使能的时候,对FMC接口上的存储器的操作会用到内核的缓存(CACHE)的。

使能了CACHE的好处就是可以提高内核访问存储器的速度。为什么使用缓存能提高速度呢?是因为在操作可以被缓存的存储器的时候,内核不是每次都去直接操作这些存储器,而是从缓存里读取数据,或者将数据先写到缓存里。看到这里,是不是觉得和前面客户说的现象有点联系了。

Cache的操作

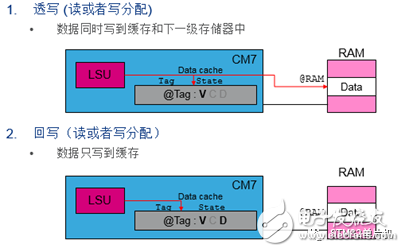

简单的说缓存工作时有两种方式:回写和透写。

回写【write back】就是数据平时只写到缓存【cache】,必要时才同步到下一级存储器中。

透写【write through】就是数据每次都同时写到缓存和下一级存储器中。这种方式可以解决数据不一致的问题,但同时也会消耗更多的总线访问时间。

缓存的操作方式,在启用缓存后有一个默认的设置 。也就是下面这张表:

请参考AN4839了解更多的关于Cache的使用说明。

问题分析及解决

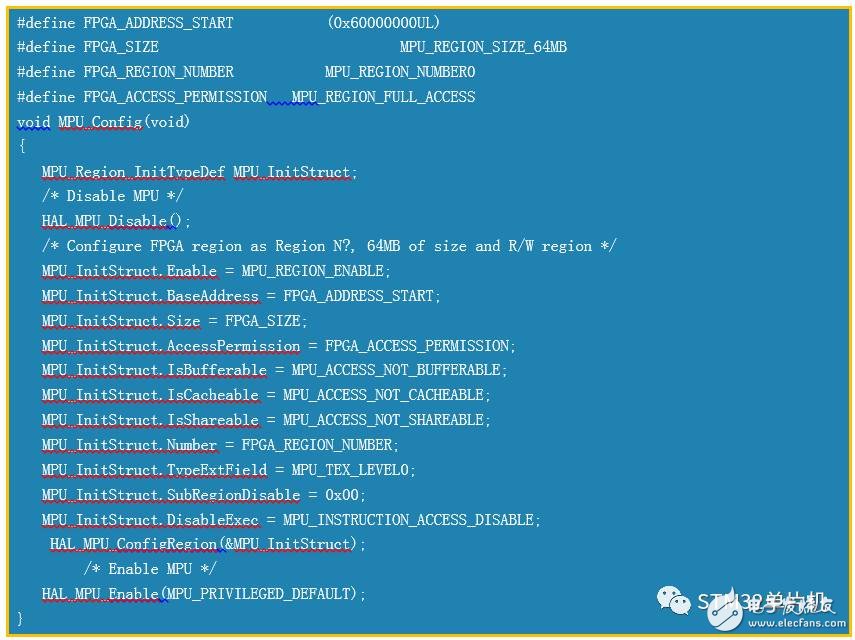

客户是通过FMC的NOR存储控制器外接一个FPGA。映射的地址范围是0x60000000~0x7FFFFFFF。从上图可以看到,它默认的缓存操作方式是WBWA(回写写分配)。也就是说,当打开DCACHE后,所有对该地址范围的操作都会先到缓存。这也解释了为什么客户发现数据没有真正写到外部存储器中。客户的数据需要实时写到FPGA中进行计算。所以对这个应用场景,回写的设置就不合适了。

对于客户的这个应用,可以通过MPU来进行配置,将0x60000000~0x7FFFFFFF范围地址的CACHE设置为透写的方式,这样数据就会实时的写到FPGA中去了。所以,针对这种情况,我们可以通过MPU合理配置来解决。

通过MPU,可以配置不同存储器空间的访问权限和Cache策略。HAL库里面提供了对应的函数和例程,参照例程用下面这段代码就可以解决客户的问题了。数据每次都是直接写到FPGA中,而不是缓存到内核的DCACHE中。

总结

D-CACHE的使用可以帮我们提高程序运行的性能,但也会带来缓存和二级存储器数据不一致和缓冲不击中带来的程序执行的时间不确定的情况,需要客户根据实际的应用来进行选择。对于实时性要求高的数据,可以像前面一样使用MPU配置成透写的方式,或者将数据放到DTCM RAM中。另外,在本文中只用MPU配置了FMC映射的部分存储区域。在实际使用中,应该对所有用到的存储空间(比如Flash, SRAM区)的属性根据实际情况进行合理配置,以免引起其它的问题。详情请参考AN4838.

-

D-CACHE

+关注

关注

0文章

1浏览量

1047

原文标题:使能D-CACHE时FMC外设运行不正常的案例

文章出处:【微信号:STM32_STM8_MCU,微信公众号:STM32单片机】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

stm32H747在M4内核使用AXI SRAM不正常的原因?

启用D-Cache的TouchGFX 4.16.1发生硬故障如何处理

自架电子邮件系统收发不正常的几种原因

STemWin_Library_V1.1.1 中 STM324x9IEVAL 的 RTOS 工程显示不正常的问题

交流接触器吸合不正常的原因有哪些

激光切割机复位不正常带来的危害和四大原因

STM32上电复位不正常 手动复位正常的原因资料下载

关于STM32串口烧录后程序正常运行,但是掉电或复位后程序不正常运行的可能解决方法。

stm32案例分享之使D-CACHE时FMC外设运行不正常原因

stm32案例分享之使D-CACHE时FMC外设运行不正常原因

评论