在数字电路设计中,时钟信号扮演着至关重要的角色。理想的时钟信号是一串无限连续的脉冲序列,除了电平要求外,其边沿应非常陡峭,有些系统还要求时钟具有50%的占空比。从电磁兼容性(EMC)的角度来看,理想的时钟信号是一个辐射源,会产生很强的EMC干扰。

在交换机系统中,周期性地重复传输固定码(例如54H码)实际上也会产生EMC干扰,并对相邻信号线产生严重干扰。因此,对时钟信号进行单独讨论是因为在数字系统中,整个系统的工作都以时钟信号为参考,时钟信号的质量直接关系到系统的工作质量。然而,当时钟信号从时钟源出发、经过驱动、线路传输,最后到达负载端时,很难保持其在时钟源时的模样。

在负载端看到的时钟信号可能会发生上升、下降沿的改变,也可能发生占空比的变化,还可能有到达不同负载的时间发生改变(相位变化)的问题等。

为了确保时钟到达不同负载的相位相同,仅采用专用时钟驱动器件是不够的,还需要考虑匹配、线长、负载等因素。以下是一些可以采取的措施来控制:

注意驱动器的传输延迟:选择合适的驱动器可以减少传输延迟对时钟信号的影响。

在时钟的传输路径上使用相同的驱动器:这样可以确保各个路径上的驱动器具有相似的性能和特性。

平衡各路径的线路延迟:通过调整线路长度或使用延迟补偿威廉希尔官方网站 来平衡各个路径上的线路延迟。

使用相同的线路匹配方法:确保各个路径上的线路匹配方法一致,以减少反射和信号失真。

平衡各路径的负载:有时可能需要在负载处增加电容来达到平衡负载的目的。

-

驱动

+关注

关注

12文章

1839浏览量

85267 -

数字电路

+关注

关注

193文章

1605浏览量

80592 -

时钟信号

+关注

关注

4文章

448浏览量

28542

发布评论请先 登录

相关推荐

使用时钟信号驱动FF的CE引脚并启用FIFO的线路

为什么写入闪存会扰乱时钟频率?

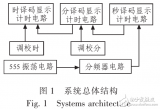

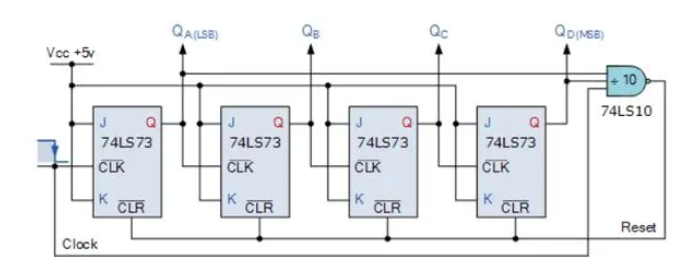

数字钟实验电路的设计与仿真

基于FPGA的数字集成时钟电路设计方案详解

基于Multisim10软件的数字钟电路的设计与仿真

如何设计一个多路彩灯控制器详细设计报告资料免费下载

FPGA设计的7项原则介绍

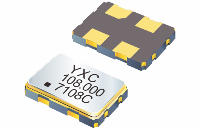

FPGA中的晶振大小多少比较合适?为什么会用到两个晶振?

什么是同步逻辑和异步逻辑?同步电路与异步电路有何区别?

YXC可编程晶振,频点100MHz,封装5032,应用于AI服务器

了解反馈振荡器,看这篇文章就够了

时钟信号的驱动是什么

时钟信号的驱动是什么

评论