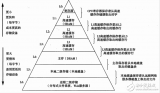

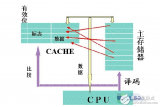

高速缓冲存储器(Cache)的工作原理,是基于计算机程序和数据访问的局部性原理,即程序在执行过程中,对数据的访问往往呈现出时间和空间的局部性。具体来说,就是程序在某一时间段内,会集中访问某一小块内存区域;同时,在访问了某个存储位置的数据后,不久后可能会再次访问该位置或其附近位置的数据。基于这一原理,高速缓冲存储器通过存储CPU近期可能访问的数据和指令,来减少对内存的访问次数,从而提高CPU的运行效率。

一、高速缓冲存储器的基本组成

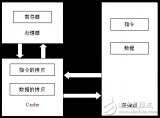

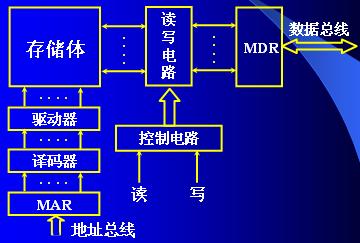

高速缓冲存储器通常由高速存储器、联想存储器、替换逻辑电路和相应的控制线路组成。这些组件协同工作,实现了对CPU访问请求的快速响应和数据的高效存储。

- 高速存储器 :这是Cache的主体部分,采用SRAM威廉希尔官方网站 ,具有高速存取的特点。高速存储器被划分为多个行和列的存储单元组,以存储CPU可能访问的数据和指令。

- 联想存储器 :用于地址联想,其存储单元与高速存储器具有相同的行数和列数。当主存储器中的某个数据块被调入高速存储器时,联想存储器会记录该数据块在主存储器中的位置信息,以便后续快速定位。

- 替换逻辑电路 :当高速存储器中没有足够的空间存储新的数据块时,替换逻辑电路会根据一定的替换算法(如LRU、FIFO、RAND等),选择并淘汰某个旧的数据块,以腾出空间存放新调入的数据块。

- 控制线路 :负责协调高速缓冲存储器与其他计算机部件(如CPU、内存)之间的数据交换和指令执行。

二、高速缓冲存储器的工作原理

当CPU需要访问某个地址的数据时,高速缓冲存储器的工作流程大致如下:

- 地址解析 :CPU发出访问请求,并提供要访问的内存地址。高速缓冲存储器首先对该地址进行解析,将其划分为行号、列号和组内地址三个字段。

- 查找高速存储器 :根据解析后的地址信息,高速缓冲存储器在高速存储器中查找相应的数据块。如果找到(即命中),则直接从高速存储器中读取数据并返回给CPU;如果未找到(即未命中),则需要进行下一步操作。

- 访问内存 :当高速存储器中未命中时,高速缓冲存储器会向内存发出访问请求,从内存中读取所需的数据块,并将其存入高速存储器中相应的位置。同时,联想存储器也会记录该数据块在主存储器中的位置信息。

- 数据返回 :从内存中读取的数据块被存入高速存储器后,高速缓冲存储器会将其返回给CPU,以满足CPU的访问请求。

- 替换操作 (如需要):如果高速存储器中没有足够的空间存储新的数据块,替换逻辑电路会根据替换算法选择并淘汰某个旧的数据块,以腾出空间存放新调入的数据块。

三、高速缓冲存储器的优势与挑战

优势:

- 提高CPU访问速度 :通过存储CPU近期可能访问的数据和指令,高速缓冲存储器显著减少了CPU对内存的访问次数,从而提高了CPU的运行效率。

- 缓解内存带宽压力 :由于CPU可以直接从高速缓冲存储器中读取数据和指令,因此减少了对内存带宽的需求,缓解了内存带宽的压力。

- 降低能耗 :由于减少了CPU对内存的访问次数,因此也降低了系统的整体能耗。

挑战:

- 容量与速度的平衡 :高速缓冲存储器的容量相对较小,但其速度却远高于内存。如何在保证速度的同时尽可能提高容量,是高速缓冲存储器设计中的一个重要挑战。

- 替换算法的优化 :替换算法的选择对高速缓冲存储器的性能有着重要影响。如何设计出更加高效、准确的替换算法,以提高高速缓冲存储器的命中率和整体性能,是一个持续的研究课题。

- 一致性问题 :在写操作中,如何保持高速缓冲存储器与内存之间数据的一致性,是高速缓冲存储器设计中需要解决的一个重要问题。这通常涉及到复杂的同步和协调机制。

四、结论

高速缓冲存储器作为计算机体系结构中的一个重要组成部分,其工作原理基于程序和数据访问的局部性原理。通过存储CPU近期可能访问的数据和指令,高速缓冲存储器显著提高了CPU的运行效率,并缓解了内存带宽的压力。然而,高速缓冲存储器的设计也面临着容量与速度的平衡、替换算法的优化以及一致性问题等挑战。随着计算机威廉希尔官方网站 的不断发展,高速缓冲存储器的性能将会进一步提升,为计算机提供更加高效、稳定和可靠的数据处理能力。

-

计算机

+关注

关注

19文章

7492浏览量

87902 -

内存

+关注

关注

8文章

3023浏览量

74029 -

高速缓冲存储器

+关注

关注

0文章

11浏览量

7513

发布评论请先 登录

相关推荐

中央处理器与高速缓冲存储器之间的联系

高速缓冲存储器部件结构及原理解析

高速缓冲存储器的分类及概述

高速缓冲存储器的作用解析

高速缓冲存储器的特点解说

高速缓冲存储器的作用是什么_有什么特点

高速缓冲存储器基础知识详细介绍

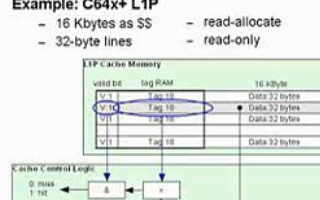

介绍 TMS320C64x 多极高速缓冲存储器

高速缓冲存储器的基本组成和工作原理

高速缓冲存储器的基本组成和工作原理

评论