新的光刻工具将在5nm需要,但薄膜,阻抗和正常运行时间仍然存在问题。

Momentum正在应用于极紫外(EUV)光刻威廉希尔官方网站 ,但这个谈及很久的威廉希尔官方网站 可以用于批量生产之前,仍然有一些主要的挑战要解决。

EUV光刻威廉希尔官方网站 - 即将在芯片上绘制微小特征的下一代威廉希尔官方网站 – 原来是预计在2012年左右投产。但是几年过去了,EUV已经遇到了一些延迟,将威廉希尔官方网站 从一个节点推向下一个阶段。

如今,GlobalFoundries,英特尔,三星和台积电相互竞争,将EUV光刻插入到7nm和/或5nm的大容量制造(HVM),从2018年到2020年的时间范围,这取决于供应商。此外,美光,三星和SK海力士希望1xnm DRAM使用EUV。

但和以前一样,在EUV进入到HVM之前,有些pieces必须聚合在一起。而芯片制造商还必须权衡复杂的分类。

根据行业的最新数据,以下是当前EUV状况的快照,以及其中的一些权衡:

• ASML正在其期待已久的250瓦特电源安装其首款具有生产价值的EUV扫描仪,这将在年底完成。然而,EUV的正常运行时间仍然是一个问题。

• 阻抗,暴露于光线时在表面形成图案的材料,今天正在努力达到EUV的目标规格。该规格可以减少,但吞吐量受到打击。有时,与抗蚀剂的相互作用可能会导致过程的变化甚至模式故障。

• EUV薄膜,面膜基础设施的重要组成部分,还没有准备好用于HVM。薄膜是防止颗粒落在面罩上的薄膜。因此,芯片制造商可能要么等待EUV防护薄膜,要么没有它们就要投入生产,至少在初期。尽管如此,即使没有这些部分,芯片制造商也可以在7nm处插入EUV光刻威廉希尔官方网站 。使用强力方法,可以为一层或多层插入EUV。然而,在5nm及以后,EUV还没有准备好在这些节点上满足更严格的规范,这意味着行业必须花更多的时间和金钱来解决这些问题。

Stifel Nicolaus的分析师何志谦表示:“我们正在越来越多的采用EUV进行批量生产。有些事情需要解决,客户的EUV可以使用多少层次。英特尔更保守。三星更看好,因为他们想把它融入DRAM和代工/逻辑。我相信在台积电5nm节点上将会实现全面的HVM实现,这可能意味着2020-2021。

显然,代工客户需要保持领先于EUV的曲线。为了帮助行业获得一些洞察力,Semiconductor Engineering已经看到了EUV扫描仪/源头、阻抗和光罩掩膜基础设施三个主要部分的威廉希尔官方网站 。

为什么选择EUV?

今天,芯片制造商使用193nm波长光刻威廉希尔官方网站 来对晶片上的精细特征进行图案化。实际上,193nm浸没式光刻在80nm间距(40nm半间距)下达到极限。因此,从22nm / 20nm开始,芯片制造商开始使用193nm浸没光刻以及各种多种图案化威廉希尔官方网站 。为了减小超过40nm的间距,多个图案化涉及在晶圆厂中使用几个光刻,蚀刻和沉积步骤的过程。

图1:自对准间隔避免掩模未对准。来源:Lam Research图2:双图案化增加密度。来源Lam Research

多个图案化工作,但它增加了更多的步骤,从而增加流程中的成本和周期时间。循环时间是从开始到结束处理晶圆的晶片所花费的时间。

为了解决这些问题,芯片制造商想要EUV。但是由于EUV尚未准备好在7nm的初始阶段,芯片制造商将首先使用浸入/多图案化。希望是在7nm以后插入EUV。 EUV是5nm必须的。

D2S首席执行官藤本真雄(Aki Fujimura)表示:"从成本的角度来看,7nm将实用化,尽管可能并不理想。 “(业内人士)希望随着7nm的音量增加,EUV将采用相同的设计规则。 5nm从实际的角度来看真的是没有EUV的。"

最初,EUV针对7nm的触点和通孔。根据GlobalFoundries的说法,为了处理接触/通孔,它需要每层两到四个掩模用于7nm的光刻。

然而,使用EUV,每层只需要一个掩模来处理7nm和5nm的接触/通孔。根据ASML,理论上,EUV简化了流程,并将生产周期的周期缩短了约30天。

“这是一个相当不错的折衷,因为你的交易四图案或一个面具接触的三重图案,”加里•帕顿,在首席威廉希尔官方网站 官GlobalFoundries的。"这并不影响任何的设计规则要么,所以客户可以得到循环时间和更好的收益率的优势。而且,因为它是准备好了,我们会由(EUV)以上的地方,我们会做金属水平和缩小"。

EUV的早期采用者希望在2019年至2020年期间将7nm威廉希尔官方网站 插入其中。“这是中心。 GlobalFoundries的高级研究员和威廉希尔官方网站 研究高级总监Harry Levinson表示:“我们正更加努。四大芯片公司在未来几年都处于HVM的轨道上。 现在真正的问题是谁将是第一,谁将是第二。

问题的根源

不过,在此之前,芯片制造商必须首先将EUV引入HVM。 这被证明比以前认为的更困难,因为EUV光刻的复杂性令人难以置信。

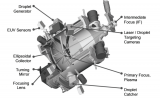

图3:该EUV的复杂性。来源:ASML

在EUV中,电源将等离子体转换成13.5nm波长的光。 然后,光反弹了10个多层镜子的复杂方案。

在这一点上,光通过可编程照明器并击中面罩。 从那里,它会弹出六个多层镜子,并以6%的角度击中晶片。

图4:准确弹跳光 来源:ASML /Carl Zeiss SMT Gmbh

最大的挑战是电源。它不会产生足够的电源或EUV光,以使EUV扫描仪能够足够快,或使其经济可行。

为了使EUV进入HVM,芯片制造商需要能产生250瓦功率的EUV扫描器。这转化为每小时125瓦的吞吐量(wph)。

实现这些目标所花费的时间比预期的要多。不久前,源产生的功率只有10瓦。然后,ASML的电源从80瓦特移动到125瓦特,将EUV的吞吐量从60瓦特提高到85瓦特。

今天,ASML正在准备首款生产的EUV扫描仪NXE:3400B。该工具的数值孔径为0.33,分辨率为13nm。 ASML高级产品经理Roderik van Es表示:“如果您看系统的成像性能,我们(已完成)13nm LS和16nm IS。 (LS是指线和空间,而IS是隔离线。)

最初,该工具将装载一个140瓦的源,实现100瓦的吞吐量。最近,ASML已经展示了一个250瓦的来源。根据Es的说法,这个250瓦特源的工业化版本将在年底前发布。

即使是250瓦的光源,但是平板印刷师担心系统的正常运行时间。 今天的193nm扫描仪可以不间断地在制造厂以250W或更快的速度运行。 相比之下,预生产的EUV机器的上升时间却在70%和80%左右。

Stifel Nicolaus Ho表示:“可用性或工具在需要停机维护之前可以运行多长时间,仍然是一个令人担忧的问题,特别是对于英特尔来说。 如果希望90年代高可用性指标的英特尔公司,则可用性水平不能达到70%甚至80%。”

不过还有待观察的是NXE:3400B在现场表现如何。 如果仍然存在正常运行时间问题,平板电脑正在研究为冗余目的购买额外的工具的想法。

那当然,这是一个昂贵的提议,芯片制造商宁愿避免。 分析师表示,每个EUV扫描仪售价约为1.25亿美元,而今天的193nm浸没式扫描仪则为7000万美元。

阻抗的问题

多年来,EUV的首要挑战是电源。现在最大的挑战是从源头转移到涉及抗蚀剂的过程。

EUV可分为两大类:化学放大抗蚀剂(CAR)和金属氧化物。 CAR在业界使用多年,利用基于扩散的过程。较新的金属氧化物抗蚀剂基于氧化锡化合物。

所谓的抵抗力也涉及所谓的RLS三角分辨率(R),线边粗糙度(LER)和灵敏度(S)之间的三个指标之间的折衷。

为了达到所需的分辨率,芯片制造商希望以20mJ / cm 2的灵敏度或剂量进行EUV抗蚀。这些抗蚀剂是可用的,但它们比以前想象的更难加入HVM。

“在32nm间距和以下,无论何种剂量,无论CAR还是金属氧化物,无论如何,至少在理由范围内(<100mJ /cm²),”GlobalFoundries Levinson说。

然而,该行业已经开发出在30mJ / cm 2和40mJ / cm 2工作的EUV抗蚀剂。基于RLS三角形的原理,较高剂量的抗蚀剂提供更好的分辨率。但是它们较慢并影响了EUV的吞吐量。

采用30mJ / cm 2的剂量,根据ASML,具有250瓦特源的EUV扫描仪的吞吐量约为104-105Wph,不含防护薄膜,低于期望的125wph目标。

Levinson说:“现有的EUV抗蚀剂能够支持7nm HVM,但是随着我们走向更小的CD,我们脱离了悬崖。” “下一个节点可能处于危险之中,因为耗时少的抗氧化剂时间过长。”

这是关于在20mJ / cm 2下开发抗蚀剂的时间和金钱。该行业正在开发针对5nm的抗蚀剂。

抗拒挑战是艰巨的。 Lam Research的威廉希尔官方网站 总监Richard Wise在最近的一次活动中说:“剂量不一定是我们想要的。” “由于EUV的随机效应,降低剂量有很多根本的身体挑战。”

随机指标是随机变化的另一种方式。光是由光子制成的。 Fractilia首席威廉希尔官方网站 官Chris Mack解释说,暴露少量抗蚀剂的光子数量与所需的曝光剂量相对应。 “但是这个平均值有随机变化。如果曝光该抗蚀剂体积的光子数量较多,则相对随机变化较小。但是,随着曝光少量抗蚀剂的光子数量变小,该数量的相对变化就会变大。

这种效应称为光子散粒噪声。散粒噪声是光刻过程中光子数量的变化。

所有类型的光刻受到随机性的影响,但是对于EUV而言更糟。"首先,EUV光子比193nm光子携带能量的14倍。所以对于相同的曝光剂量,有14倍的光子,“麦克说。 “其次,我们正在努力通过使用低曝光剂量来提高EUV扫描仪的吞吐量。这也意味着更少的光子。光子越少,光子或射击噪声就会有很大的随机不确定性。"

光子数量的变化是有问题的。 “我们有更高能量的光子,但还不够。因此,我们有线宽粗糙度和线边粗糙度(图案),“TEL威廉希尔官方网站 人员资深成员Ben Rathsack说。 (LER被定义为特征边缘与理想形状的偏差。)

如果这还不够,变化也可能导致其他问题。 Imec高级图案部门主管Gregory McIntyre表示:“我们将在成像中成为挑战第一的是极端粗糙度事件或纳米桥接,断线和合并或漏洞等场合的随机故障。

因此,在EUV曝光过程中,扫描仪有时无法解决线路,空间或联系人。或者进程可能导致线路断开或联系人合并。

薄膜问题

除了阻抗,还有其他问题,即EUV光掩模基础设施。光掩模是给定IC设计的主模板。面膜开发之后,它被运到制造厂。将掩模放置在光刻工具中。该工具通过掩模投射光,这又掩模在晶片上的图像。

多年来,该行业一直在制造EUV面罩,尽管这个过程仍然具有挑战性。 KLA-Tencor标线制品部总经理Weston Sousa表示:“面罩行业正在加大EUV标线的开发力度。 “挑战众多,从空白质量和CD均匀性到图案缺陷和修复。”

成本和收益也是问题。 “这是我担心的面具,”GlobalFoundries的巴顿说。 “面罩本身存在缺陷,制造时面罩有缺陷。”

来自最近eBeam倡议调查的数据显示,总体面罩产量处于健康的94.8%,但EUV面罩产量下降了约64.3%。

并且在每个节点处,掩模缺陷变得越来越小,难以找到。 “缺陷标准在早期循环中更为松动。随着时间的推移,它将进入HVM级别。英特尔®嵌入式光罩单元Intel Mask操作系统的面罩威廉希尔官方网站 总监Jeff Farnsworth表示,HVM级别肯定不会松动。

另外,三星的研究人员Heebom Kim表示,EUV掩模比复杂的光学掩模贵8倍。但是随着EUV进入HVM,根据ASML的说法,EUV掩模的成本可能会下降到光学成本的三倍以上。

光学和EUV掩模是不同的。在光学上,掩模坯料由玻璃基板上不透明的铬层组成。

相比之下,EUV掩模空白由衬底上的40至50个交替的硅和钼层组成。在光学和EUV中,掩模毛坯被图案化,形成光掩模。

面具制造商希望实现两个目标。首先是生产无缺陷的EUV面罩。然后,他们希望防止缺陷登陆面具。在这种情况下,来自扫描仪或其他过程的颗粒可能无意中落在掩模上。

如果在曝光阶段在EUV扫描器的掩模上存在缺陷,则它们可以在晶片上印刷,从而影响芯片的产量。

通常,面膜制造商正在制造无缺陷的面罩方面取得进展。防止颗粒着色在掩模上是不同的事情,并且涉及掩模基础设施中的关键部分 - 防护薄膜。防护薄膜组件作为面罩的防尘罩。

图5:原型薄膜。来源:ASML

不久前,业内人士坚持认为,EUV扫描仪可以在没有防护眼镜的环境中处理干净的环境。然后,芯片制造商改变了他们的立场,表示不会保证EUV扫描仪或其他工具在流程中保持100%的清洁。没有防护薄膜制造商说,EUV面罩容易发生颗粒和缺陷。

所以行业开始开发EUV防护薄膜。用于光学掩模的防护薄膜基于薄聚合物材料。相比之下,唯一的EUV防护薄膜供应商ASML开发出了仅50纳米厚的多晶硅型EUV防护薄膜。

在操作中,当EUV灯击中防护薄膜时,膜的温度将从600摄氏度升高到1000摄氏度。

问题是防护薄片是脆的。在这些温度下,有些人担心EUV防护薄膜可能会在加工过程中恶化,造成EUV面罩和扫描仪的损坏。

到目前为止,ASML的EUV防护薄膜已经用140V的EUV电源进行了测试。但是,防护薄膜将如何反应250瓦特源仍然不清楚。

应用材料面具和TSV蚀刻部门的威廉希尔官方网站 人员和CTO主要负责人Wu Banqiu说:“对于机械强度和应用性能,EUV薄膜有一些挑战。 “防护薄膜吸收一些EUV能量。这种能量会导致防护薄膜的温度升高。防护薄膜也存在于真空中。这意味着自然对流冷却非常低。天然的热转移非常困难,因为防护薄膜太薄了。”

总而言之,关于在HVM中使用多晶硅薄膜,如果不怀疑,仍然存在一些不确定性。所以现在,行业正在改变调整和考虑两个选择 - 等待一个HVM防护薄片或没有他们开始生产。

英特尔表示,如果没有防护眼镜,它将不会进入EUV生产。英特尔的Farnsworth说:“我们正在积极地研究它。

然而,该行业正在对冲它的投注。至少在初期,许多人也在考虑计划进入EUV生产而没有防护眼镜。

在理论上,使用EUV,芯片制造商可以处理没有防护薄膜的接触和通孔。 “对于那些人来说,不需要一个防护薄膜,因为关键区域较小。因此,造成问题的粒子的风险较小,“GlobalFoundries Patton说。

但是有一些后果。即使EUV扫描仪是干净的,不需要的颗粒也会粘在掩模上。

因此,如果芯片制造商在没有防护膜的情况下投入生产,则必须在流程中实施更多的掩模检查和清洁步骤。 “我们将做我们所做的与晶片印刷和晶圆检查,” GlobalFoundries 的莱文森说,“但是很痛苦。 所以,我们需要一个好的防护薄膜解决方案。”

在研发方面,该行业正在研究下一代薄膜和面具基础设施的其他部分。 可以肯定的是,对于EUV抗议的发展也有紧迫感。 而且,当然还有电源。

这一切会实现吗? 时间会告诉我们EUV光刻传奇。

-

英特尔

+关注

关注

61文章

9964浏览量

171776 -

光刻威廉希尔官方网站

+关注

关注

1文章

146浏览量

15825 -

EUV

+关注

关注

8文章

607浏览量

86027 -

扫描器

+关注

关注

0文章

166浏览量

11912

原文标题:EUV面临的问题和权衡

文章出处:【微信号:eetop-1,微信公众号:EETOP】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

中国制造商如何获得PSE认证?

EUV热潮不断 中国如何推进半导体设备产业发展?

euv光刻机是干什么的

浅谈EUV光刻的基础知识 EUV光刻如何制造芯片?

EUV光刻威廉希尔官方网站 优势及挑战

面对EUV光刻威廉希尔官方网站

,芯片制造商如何权衡复杂分类

面对EUV光刻威廉希尔官方网站

,芯片制造商如何权衡复杂分类

评论