在FPGA的世界里,设计软件在整个系统开发过程中发挥着至关重要的作用,它通过先进的功能使端到端编程变得更加容易,从而在充分利用器件功能的同时实现设计的灵活性。

然而,由于基于FPGA的片上系统(SoC)设计是一项多学科的工作,需要硬件架构、嵌入式软件、系统集成等方面的专业知识,因此非FPGA设计人员或首次使用FPGA的用户往往需要很高的学习成本。

莱迪思Propel是一款基于图形用户界面(GUI)的先进设计环境,旨在通过提供一整套图形和命令行工具来创建、分析、编译和调试基于FPGA系统的硬件设计和软件设计,从而应对以上挑战。

最新版本的莱迪思Propel(2024.1)进一步简化了开发周期,改善了软硬件设计人员的体验。请继续阅读,了解最新更新如何帮助您在几分钟内构建基于FPGA的处理器系统。

为开发者赋能的重要工具

最新的莱迪思Propel提供了一个用户友好的环境,具有拖放IP实例化和“构建即正确”的设计方法,大大增强了易用性。这有助于设计人员快速高效地构建复杂的系统,通过引脚间自动连接、向导式配置和参数化来简化设计流程,快速集成处理器和外设IP。

Propel还通过图形和命令行工具提高灵活性,满足各种技能水平的设计人员的需要。它允许脚本级编辑,以实现细粒度控制和更新现有设计。它还集成了丰富的资源,其强大的IP服务器定期更新,帮助开发人员在快速在基于莱迪思FPGA的设计上实现新的IP。

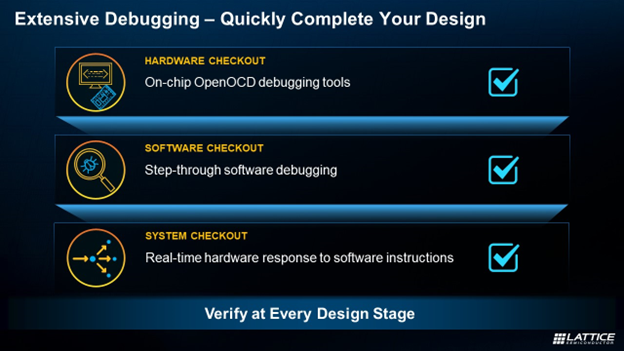

最后,该工具的软件开发工具包(SDK)提供了一个无缝的软件开发环境,集成了行业标准的集成开发环境(IDE)和工具链、软件/硬件调试功能、软件库和用于Propel定义系统的电路板支持包(BSP)。

这些功能共同构成了一个高效的设计环境,可大大减少嵌入式设计人员的开发时间和复杂性,使他们能够专注于FPGA处理器系统的创新和优化。

在硬件和软件环境中提供全方位价值

Propel的最新版本为硬件和软件设计者带来了很多价值。它为IP合作伙伴和客户提供了一个完全脚本化的IP发布和使用流程,为那些包含混合语言设计块的设计自动生成仿真脚本,从而实现系统验证的灵活性。

对于嵌入式软件设计人员,Propel可用于分析其C/C++代码的性能,并在系统模型上调试代码,而无需电路板。QuickEMUlator(QEMU)的加入增加了软件工程师团队的可扩展性,因为每位工程师都可以在QEMU模型上运行自己的软件代码,而无需多个电路板。

Propel全新价值增强功能和特性包括:

★ QuestaSim莱迪思版:在调试功能和提高设计效率方面迈出了一大步。与包含ModelSim的前一版本相比,QuestaSim性能更强,采用了更先进的仿真威廉希尔官方网站 ,仿真速度更快,支持多语言开发。该流程是半自动的,Propel为用户处理了大部分设置工作,用户可以轻松上手。

★设计创建增强功能(Builder中的SoC和SDK中的C/C++):Propel帮助设计人员在设计流程中快人一步,为各种应用需求提供多种不同的模板。其新的模板创建流程让用户更方便辨别哪些模板更容易创建。设计人员可以通过创建跨职能团队共享的自定义C++项目模板来提高工作效率。

★使用事务控制语言(TCL)实现设计自动化:设计人员可使用Propel自动生成TCL构建脚本,用于从零开始重建设计。这样,倾向使用预先编写脚本的仅使用控制台的用户就能轻松上手,并继续使用PropelBuilder进行开发。

★优化设计规则检查(DRC):PropelBuilder的DRC引擎在此版本中也得到了增强,支持几种新的设计规则检查类型。现在它支持几种新的增强型DRC,用户能以新的方式开发项目,并在设计流程中更早地发现问题,从而提高易用性。

★颜色定制功能:Propel Builder中的颜色定制功能大大增强,图形用户界面中的几乎所有内容都可以进行颜色定制。组件外观、组件名称、组件端口、原理图背景、图形用户界面背景和控制台文本都支持更多颜色定制。

★支持高速集成电路硬件描述语言(VHDL):设计人员可以开发和导入自己的VHDL代码,这些代码可以直接集成到PropelBuilder的SoC设计中。与Verilog类似,Propel 2024.1增强了对VHDL的支持。用VHDL和Verilog编写的RTL代码可转换为胶合逻辑组件,用于系统集成。

简化FPGA设计流程和仿真

Propel现支持QEMU虚拟平台,嵌入式设计人员能够使用Propel和莱迪思的嵌入式设计流程,而无需实际的器件。该流程为用户处理所有必要的工具链和配置设置,帮助他们轻松仿真自己的虚拟RISC-V设计。QEMU是一个多功能虚拟平台,可为用户带来诸多好处,尤其是在软件开发和测试领域。

FreeRTOS升级:Propel SDK还支持多个新的应用模板,用户能够更轻松地使用各种新的设计流程。在这个版本中,我们带来了两个新的基于FreeRTOS(实时操作系统)的模板,提供了详细和简化示例,演示它如何在用户的RISC-V系统中运行。此外,我们还支持一个新的时序分析模板,向用户演示如何使用gprof生成性能数据。

凭借莱迪思Propel的强大功能,FPGA开发人员可以在其应用和系统开发中快速、高效地探索全新可能。无论您是经验丰富的工程师还是刚刚入门,Propel直观的界面和全面的功能将助您快速取得设计成功,从简单的应用到复杂的嵌入式控制和数据处理系统。

-

处理器

+关注

关注

68文章

19265浏览量

229683 -

FPGA

+关注

关注

1629文章

21729浏览量

603049 -

莱迪思

+关注

关注

2文章

229浏览量

39112 -

Propel

+关注

关注

0文章

3浏览量

230

原文标题:利用莱迪思Propel赋能基于FPGA的处理器设计

文章出处:【微信号:Latticesemi,微信公众号:Latticesemi】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

使用莱迪思Automate解决方案集合实现具有预测性维护功能的电机控制

简单了解莱迪思Propel的强大功能

简单了解莱迪思Propel的强大功能

评论