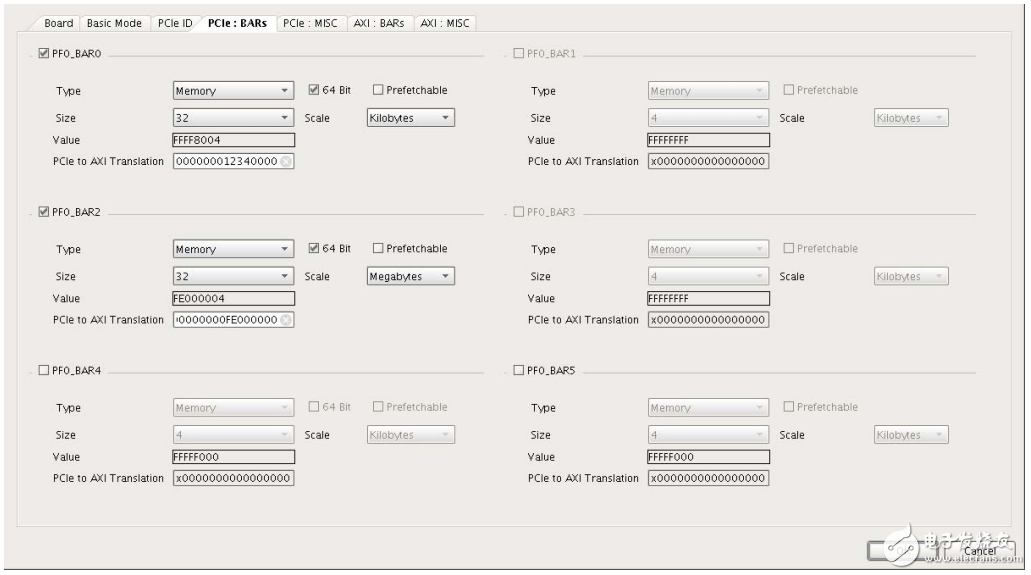

UltraScale系列芯片包含PCIe的Gen3 Integrated Block IP核在内的多种不同功能的IP核都会有一页设置为PCIe:BARs,设置IP核的Base address register 的相关参数,如图1所示:

图1 PCIe:BARs 配置图

一般来说在FPGA中使用PCIe核都是Endpoint mode,我们的PC主机端是Rootpoint mode,一般会有一个Root Complex的混合管理器,来管理接入PCIe总线的端点设备。对于PC机来说,当PC机识别该PCIe设备后便会识别到BAR n相对应的基地址和地址空间(不过该基地址是PC机的Root Complex主动分配的,还是PCIe设备内部固定的还有疑问)。设别基本配置信息后,PC机便可以对PCIe的内存空间进行读写操作了。

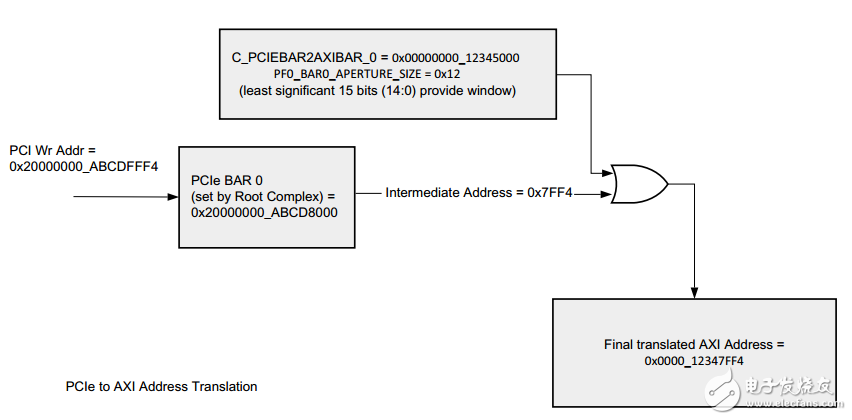

而PCIe IP核本身能够引出AXI总线接口,该AXI接口是memory map 型的,所以就肯定存在自己的地址空间,本文所提的PCIe to AXI Translation便是PCIe的地址空间到AXI的地址空间的转换。

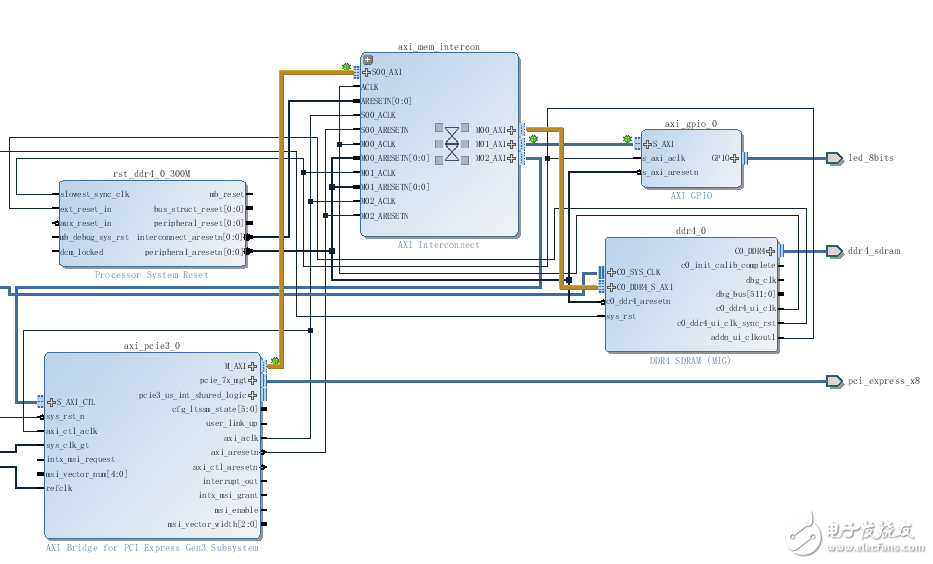

这里就图1中的BAR0来说明下PCIe to AXI Translation的转换过程。BAR0的配置为:64bit数据位宽、32kilobytes地址范围、PCIe to AXI Translation为0x0000000012340000。此时的PCIe IP核的BAR0是拓展连接到外部的AXI总线的,该总线连接到另外一个DDR4 MIG IP核,如图2所示。图中重点标注的AXI总线便是PCIe核引出的AXI总线。

图2 PCIe核拓展AXI接口

假设PC机设别到的PCIe BAR0的基地址为0x0000000000000000,在FPGA内部DDR4的AXI基地址为0x0000000012340000。现在PC机想要往FPGA内部的DDR4地址空间的0x000000001234000F地址写入数据,那么PC机应该对PICe内存空间的0x000000000000000F写入数据,然后由PCIe to AXI Translation的关系,便会把0x000000000000000F转换到0x000000001234000F上实现对AXI总线的操作,进而实现对DDR4的写入操作。图3可以看出具体的转换操作。

图3 PCIe to AXI Translation 转换图

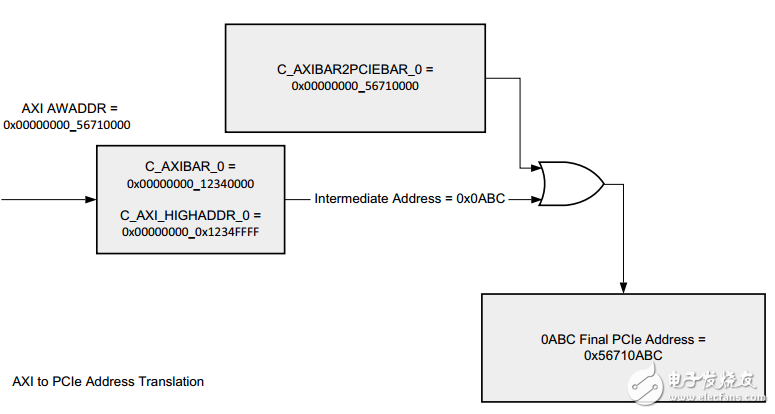

既然有PCIe to AXI Translation,那相应的也有AXI to PCIe Translation了,图4是AXI to PCIe Translation的转换图,不过这种操作应用不多,原理也跟PCIe to AXI Translation差不多,这就不再赘述了。

图4 AXI to PCIe Translation 转换图

-

PCIe

+关注

关注

15文章

1238浏览量

82635 -

AXI

+关注

关注

1文章

127浏览量

16630

发布评论请先 登录

相关推荐

一文详解PCIe内存空间到AXI内存空间的转换

一文详解PCIe内存空间到AXI内存空间的转换

评论