微处理器作为计算机系统的核心部件,其内部结构复杂而精密,集成了众多关键组件以实现高效的数据处理和控制功能。

一、微处理器的基本组成

微处理器的基本组成通常包括运算器、控制器、寄存器组以及内部总线等关键部分。这些部分相互协作,共同完成指令的执行和数据的处理。

1. 运算器

运算器是微处理器的核心部分,负责执行各种算术运算和逻辑运算。它主要由算术逻辑单元(ALU)和寄存器组成。

- 算术逻辑单元(ALU) :ALU是微处理器的计算中心,能够执行加、减、乘、除等基本算术运算,以及与、或、非、异或等逻辑运算。ALU的设计直接影响微处理器的计算能力和效率。

- 寄存器 :寄存器用于临时存储ALU的计算结果和其他运算数据。这些寄存器包括累加器、状态寄存器、程序计数器等,它们在运算过程中起着至关重要的作用。

2. 控制器

控制器是微处理器的指挥中心,负责指令的取指、译码和执行。它主要由指令寄存器、指令译码器和控制逻辑组成。

- 指令寄存器 :用于存储从内存中读取的指令,以便后续进行译码和执行。

- 指令译码器 :将指令寄存器中的指令译码为微处理器可以执行的命令,即控制信号。

- 控制逻辑 :根据译码结果产生一系列的控制信号,用于控制运算器、寄存器组以及其他部件的工作。

3. 寄存器组

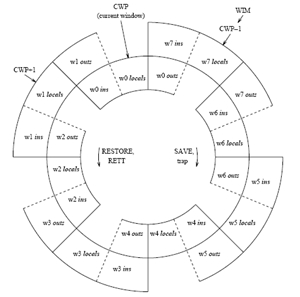

寄存器组是微处理器中用于存储数据的重要部分,它由多个寄存器组成,包括通用寄存器和专用寄存器。

- 通用寄存器 :如累加器、变址寄存器等,用于存储运算过程中需要频繁访问的数据。

- 专用寄存器 :如程序计数器(PC)、状态寄存器等,具有特定的用途和功能。程序计数器用于指示下一条要执行的指令的地址;状态寄存器用于记录微处理器的运行状态和条件码等信息。

4. 内部总线

内部总线是微处理器内部各部分之间的数据传输通道,包括数据总线、地址总线和控制总线。它们共同构成了微处理器的内部通信网络。

- 数据总线 :用于传输数据信号,其宽度决定了微处理器内部数据传输的位数。

- 地址总线 :用于传输地址信号,指定数据存储或访问的位置。

- 控制总线 :用于传输控制信号,如读写信号、中断信号等,用于协调微处理器内部各部件的工作。

二、微处理器的内部结构设计

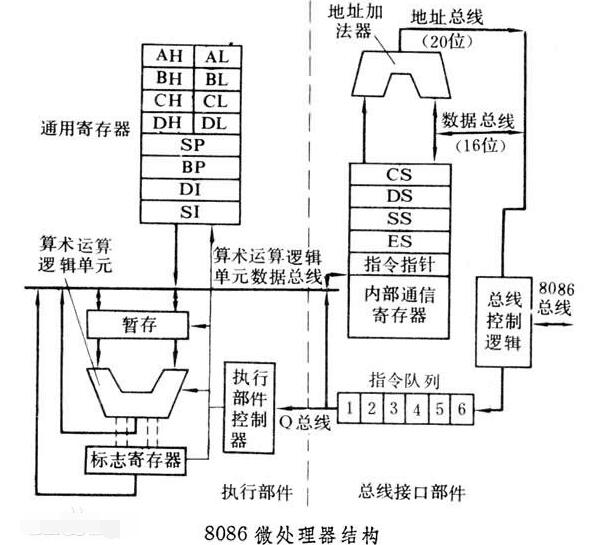

微处理器的内部结构设计通常根据其具体架构和用途而有所不同。以经典的x86架构为例,其内部结构设计可以分为执行部件(EU)和总线接口部件(BIU)两大部分。

1. 执行部件(EU)

执行部件是微处理器中负责执行指令的核心部分,它主要由运算器、寄存器组和部分控制逻辑组成。

- 运算器 :如前所述,负责执行各种算术运算和逻辑运算。

- 寄存器组 :包括通用寄存器和专用寄存器,用于存储数据和指令执行过程中的中间结果。

- 控制逻辑 :与控制器中的控制逻辑相似,但更侧重于执行部件内部的控制和协调。

2. 总线接口部件(BIU)

总线接口部件是微处理器与外部存储器、I/O接口等部件进行通信的桥梁,它主要负责指令的取指和数据的传输。

- 指令队列 :用于暂存从内存中取出的指令流,以便后续执行。

- 地址寄存器 :用于寄存CPU要向外部发出的地址信息。

- 数据缓冲器 :起到CPU内、外传输数据的缓冲作用,确保数据传输的稳定性和可靠性。

- 总线控制逻辑 :负责控制数据总线、地址总线和控制总线的操作,实现CPU与外部部件之间的通信。

三、微处理器的运行机制

微处理器的运行机制主要包括取指、译码、执行和回写四个阶段。

- 取指阶段 :CPU通过地址总线向内存发出地址信号,通过控制总线发出读指令信号,从内存中取出一条指令并存储到指令寄存器中。

- 译码阶段 :指令译码器对指令寄存器中的指令进行译码,产生相应的控制信号。

- 执行阶段 :控制逻辑根据译码结果控制运算器执行相应的运算或操作,同时寄存器组参与运算过程中的数据存储和传输。

- 回写阶段 :将运算结果或中间结果存储回寄存器组或内存中,为下一条指令的执行做准备。

四、微处理器的性能优化

微处理器的性能优化是半导体威廉希尔官方网站 和计算机科学领域持续关注的热点。随着应用需求的不断增长,对处理器性能的要求也越来越高。以下将从几个方面继续探讨微处理器性能优化的威廉希尔官方网站 和方法。

1. 指令集优化

指令集是微处理器执行操作的基础,优化指令集可以显著提升处理器的性能。现代微处理器通常采用复杂指令集(CISC)或精简指令集(RISC)架构,并通过增加新的指令、改进现有指令的执行效率等方式来优化指令集。

- CISC与RISC的融合 :现代处理器往往融合了CISC和RISC的特点,采用CISC的外部指令集和RISC的内部执行方式,以提高指令的执行效率和灵活性。

- SIMD(单指令多数据)指令 :通过一条指令同时处理多个数据,可以显著提高多媒体和图形处理等领域的性能。

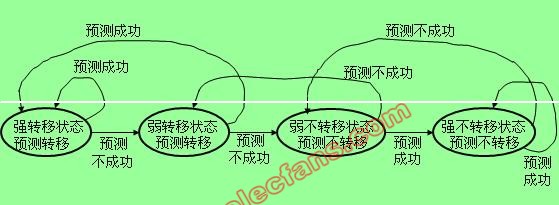

- 分支预测 :为了减少分支指令带来的执行延迟,现代处理器采用了分支预测威廉希尔官方网站 ,提前预测分支的走向并预取相关指令,以提高执行效率。

2. 缓存威廉希尔官方网站

缓存是微处理器中用于存储临时数据的关键部件,它能够显著减少处理器对内存的访问次数,提高数据访问速度。缓存威廉希尔官方网站 的优化主要包括以下几个方面:

- 多级缓存 :现代处理器通常采用多级缓存结构(如L1、L2、L3缓存),以提高缓存命中率和降低访问延迟。

- 智能缓存策略 :如LRU(最近最少使用)替换算法、伪LRU算法等,用于管理缓存中的数据,确保常用数据能够被快速访问。

- 预取威廉希尔官方网站 :通过分析程序的行为和访问模式,预测未来可能需要的数据,并提前将其从内存中加载到缓存中,以减少缓存未命中的次数。

3. 并行处理威廉希尔官方网站

随着多核处理器的普及,并行处理威廉希尔官方网站 成为提高处理器性能的重要手段。并行处理威廉希尔官方网站 主要包括以下几种形式:

- 多线程 :通过在同一处理器上同时运行多个线程,实现任务级别的并行处理。现代操作系统和编程语言提供了丰富的线程管理工具和库,使得多线程编程变得更加容易。

- 多核处理器 :每个核心都可以独立执行指令和数据处理任务,从而实现指令级别的并行处理。多核处理器通过共享缓存和内部总线等资源,实现了高效的数据共享和通信。

- 向量处理 :通过SIMD指令集,实现单条指令对多个数据元素的并行处理,特别适用于多媒体、科学计算等领域。

4. 动态电压与频率调整(DVFS)

动态电压与频率调整威廉希尔官方网站 是一种根据处理器负载情况动态调整其工作电压和频率的方法。在处理器负载较低时,降低其工作电压和频率可以显著降低功耗和发热量;在处理器负载较高时,提高其工作电压和频率可以确保足够的处理性能。DVFS威廉希尔官方网站 通过平衡功耗和性能之间的关系,实现了能耗的优化。

5. 制造工艺与封装威廉希尔官方网站

制造工艺和封装威廉希尔官方网站 的改进也是提高微处理器性能的重要手段。随着半导体制造工艺的不断进步,处理器的晶体管密度不断提高,功耗和发热量逐渐降低,同时性能也得到提升。封装威廉希尔官方网站 的改进则使得处理器能够更好地与其他部件集成和通信,提高了系统的整体性能和可靠性。

五、未来展望

随着人工智能、物联网等新兴威廉希尔官方网站 的快速发展,对微处理器性能的要求将越来越高。未来微处理器的发展将更加注重以下几个方面:

- 能效比提升 :在保持高性能的同时,进一步降低功耗和发热量,提高能效比。

- 异构计算 :结合CPU、GPU、FPGA等多种计算单元的优势,实现更加灵活和高效的计算模式。

- 安全性增强 :加强处理器的安全防护能力,防止恶意攻击和数据泄露。

- 定制化设计 :根据特定应用场景的需求进行定制化设计,提高处理器的针对性和性能表现。

总之,微处理器的内部结构复杂而精密,其性能优化涉及多个方面和层次。通过不断的威廉希尔官方网站 创新和改进,微处理器将继续在各个领域发挥重要作用,推动科技进步和社会发展。

-

寄存器

+关注

关注

31文章

5336浏览量

120261 -

微处理器

+关注

关注

11文章

2259浏览量

82413 -

计算机系统

+关注

关注

0文章

282浏览量

24107

发布评论请先 登录

相关推荐

80X86微处理器

奔腾(Pentium)微处理器介绍

SPARC微处理器综合介绍

基于FPGA实现VLIW微处理器

PS501的内部结构图

处理器系列之X86微处理器体系结构

微处理器内部结构介绍

微处理器内部结构介绍

评论