D触发器(Data Flip-Flop)是一种常见的数字逻辑电路元件,用于存储一位二进制数据。D触发器可以是电平触发的,也可以是边沿触发的,具体取决于其设计和应用场景。

一、D触发器的工作原理

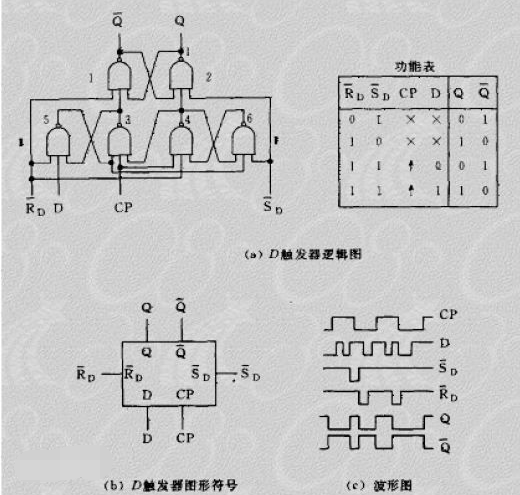

D触发器是一种具有两个稳定状态的双稳态电路,其基本结构包括两个交叉耦合的反相器或门电路。D触发器的输入端为数据输入端(D),输出端为Q和Q'(Q的反相)。D触发器的工作原理如下:

- 当D触发器的时钟信号(CLK)为低电平时,无论D端输入何种信号,Q端和Q'端的状态都不会改变,保持在上一个状态。

- 当CLK信号由低电平跳变为高电平时,D触发器的状态将根据D端的输入信号进行更新。如果D端输入为高电平,则Q端输出高电平,Q'端输出低电平;如果D端输入为低电平,则Q端输出低电平,Q'端输出高电平。

- 当CLK信号由高电平跳变回低电平时,D触发器的状态保持不变,即Q端和Q'端的输出状态与CLK信号跳变前的状态相同。

二、D触发器的特性

- 存储功能:D触发器可以存储一位二进制数据,具有记忆功能。

- 双稳态特性:D触发器具有两个稳定状态,即Q端和Q'端可以分别输出高电平和低电平。

- 同步特性:D触发器的状态更新与时钟信号同步,只有在CLK信号的上升沿或下降沿时才会更新状态。

- 透明窗口特性:在某些D触发器设计中,当CLK信号为高电平时,D触发器的状态可以实时反映D端的输入信号,称为透明窗口特性。

三、D触发器的应用

D触发器在数字电路设计中有着广泛的应用,主要包括:

- 数据存储:D触发器可以用于存储数据,如寄存器、计数器等。

- 时序控制:D触发器可以用于实现同步逻辑,如分频器、移位寄存器等。

- 信号整形:D触发器可以用于消除信号抖动,提高信号稳定性。

- 脉冲捕捉:D触发器可以用于捕捉脉冲信号,实现脉冲延迟、脉冲宽度控制等功能。

四、电平触发与边沿触发的区别

电平触发和边沿触发是D触发器的两种不同的触发方式,它们的主要区别如下:

- 触发条件不同:电平触发的D触发器在CLK信号保持高电平时,D端的输入信号可以实时影响Q端和Q'端的输出;而边沿触发的D触发器只有在CLK信号的上升沿或下降沿时,D端的输入信号才会影响Q端和Q'端的输出。

- 抗干扰能力不同:边沿触发的D触发器具有较好的抗干扰能力,因为它只在CLK信号的边沿时刻更新状态,可以有效地抑制噪声和抖动。而电平触发的D触发器在CLK信号保持高电平时,容易受到噪声和抖动的影响。

- 功耗不同:电平触发的D触发器在CLK信号保持高电平时,D端的输入信号会持续影响Q端和Q'端的输出,可能导致功耗较高。而边沿触发的D触发器只在CLK信号的边沿时刻更新状态,功耗相对较低。

- 应用场景不同:电平触发的D触发器适用于对实时性要求较高的场景,如实时数据传输、实时信号处理等;而边沿触发的D触发器适用于对稳定性和抗干扰能力要求较高的场景,如同步逻辑设计、信号整形等。

五、D触发器的设计

D触发器的设计主要包括以下几个方面:

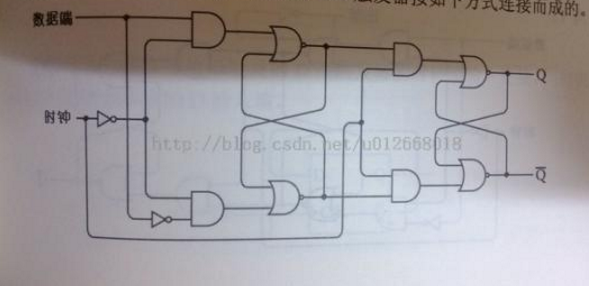

- 基本结构设计:D触发器的基本结构包括两个交叉耦合的反相器或门电路,以及输入端D、输出端Q和Q'、时钟端CLK等。

- 触发方式选择:根据应用场景和性能要求,选择合适的触发方式,如电平触发或边沿触发。

- 门电路设计:选择合适的门电路类型,如CMOS、TTL等,以满足功耗、速度、抗干扰能力等性能要求。

- 时钟信号处理:设计合适的时钟信号处理电路,如时钟缓冲、时钟分频等,以保证时钟信号的稳定性和可靠性。

- 输出电路设计:设计合适的输出电路,如三态输出、线驱动等,以满足不同的应用需求。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

元件

+关注

关注

4文章

915浏览量

36692 -

边沿触发

+关注

关注

0文章

11浏览量

9171 -

数字逻辑电路

+关注

关注

0文章

106浏览量

15817

发布评论请先 登录

相关推荐

什么是边沿触发器_边沿D触发器介绍

边沿触发器,指的是接收时钟脉冲CP 的某一约定跳变(正跳变或负跳变)来到时的输入数据。在CP=l 及CP=0 期间以及CP非约定跳变到来时,触发器不接收数据的触发器。具有下列特点的

发表于 01-31 09:02

•7.2w次阅读

脉冲和边沿触发器区别

脉冲通常是指电子威廉希尔官方网站

中经常运用的一种象脉搏似的短暂起伏的电冲击(电压或电流)。主要特性有波形、幅度、宽度和重复频率。具有下列特点的触发器称为边沿触发方式触发器,简称

发表于 01-31 13:41

•5.4w次阅读

边沿触发器的状态变化由什么控制

边沿触发器(Edge-Triggered Flip-Flop)是一种数字逻辑电路,其状态变化由输入信号的边沿控制,即由输入信号从低电平变为高电平

同步触发器和边沿触发器的区别

同步触发器和边沿触发器是数字电路中两种常见的触发器类型,它们在触发方式、工作原理、性能特点以及应用场景等方面存在显著的差异。

d触发器是电平触发还是边沿触发

D触发器(Data Flip-Flop)是一种常见的数字逻辑电路元件,主要用于存储一位二进制数据。D触发器可以是电平触发的,也可以是边沿

主从jk触发器和边沿jk触发器的区别

主从JK触发器和边沿JK触发器是数字电路中常用的存储元件,它们在功能和应用上既有相似之处,也存在显著的区别。以下将从多个方面介绍这两种触发器

电平触发与边沿触发的区别

电平触发与边沿触发的区别

评论