引言

雪崩耐量是功率器件性能评估的关键指标,那么什么是雪崩耐量呢?即向半导体的接合部施加较大的反向衰减偏压时,电场衰减电流的流动会引起雪崩衰减,此时元件可吸收的能量称为雪崩耐量,表示施加电压时的抗击穿能力。它对步进电机,开关电源等终端产品的安规及可靠性有着紧密的影响。新洁能是国内为数很少的、拥有自主半导体器件工艺设计能力的功率集成电路设计公司,显著区别于只能采用晶圆厂标准工艺制程的一般设计公司。新洁能应用团队从功率器件的雪崩原理入手详细为大家介绍以下几点:

1、雪崩击穿的原理与介绍;

2、单脉冲雪崩与重复雪崩的测试原理有什么不同;

3、雪崩击穿失效机理是什么;

4、如何在应用设计中提升电路的抗雪崩能力;

一、雪崩击穿的原理与介绍

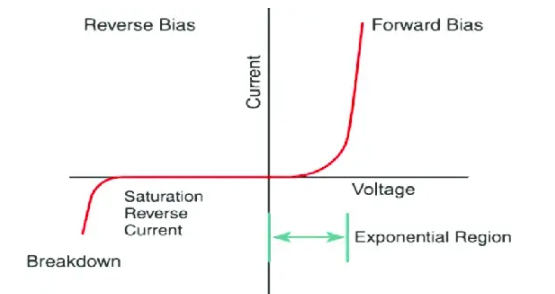

当功率器件PN结的反向电压增大到某一数值后,半导体内载流子通过碰撞电离开始倍增,这一现象与宏观世界中高山雪崩是很像的,所以我们称之为雪崩击穿。

功率器件并不是触发雪崩就会损坏的,而是对雪崩能量有一定的承受能力,称之为雪崩耐量,一般从以下两个特性来考量某个功率器承受的雪崩耐量的强弱,分别是:

1、单脉冲雪崩耐量;

2、重复雪崩耐量。

二、单脉冲雪崩与重复雪崩的测试原理

单脉冲雪崩

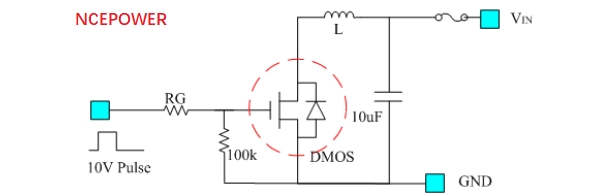

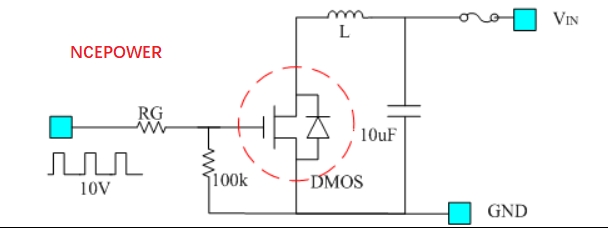

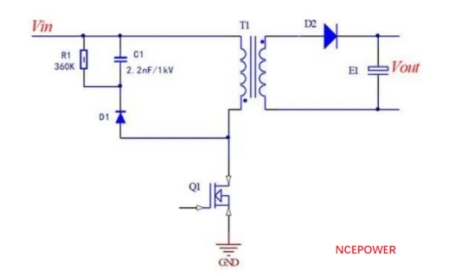

图1给出了单脉冲雪崩测试的原理图,对待测器件的Gate极施加开启信号,器件导通,电流从器件的沟道通路流通对电感L储能;当单脉冲结束,驱动信号由高电平变为低电平,Gate关闭,此时电感能量泄放于器件上。

图1给出了单脉冲雪崩测试的原理图,对待测器件的Gate极施加开启信号,器件导通,电流从器件的沟道通路流通对电感L储能;当单脉冲结束,驱动信号由高电平变为低电平,Gate关闭,此时电感能量泄放于器件上。

(图1)

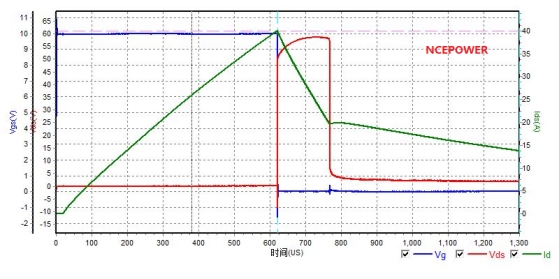

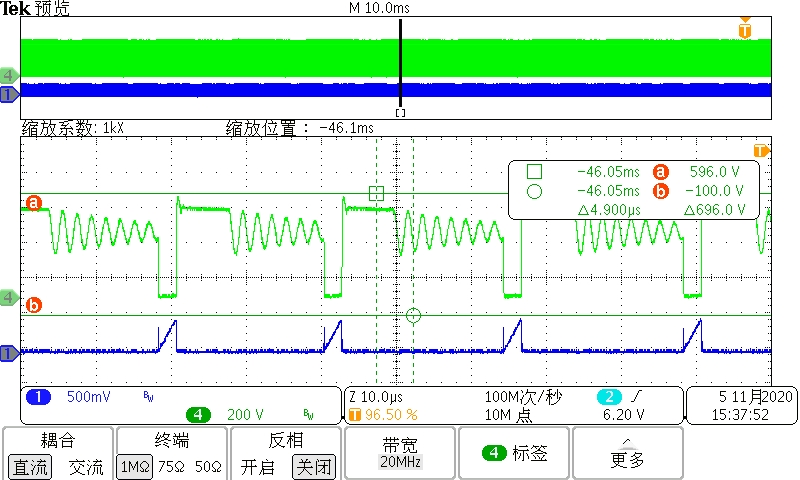

图2给出了单脉冲雪崩测试几个关键位置结点的示波器波形图,可以看到当器件Gate电压Vgs从高变低后,器件的漏端电压瞬时升高到雪崩电压,击穿器件,一直持续到电感能量在数微秒时间内完全泄放完毕。

L=0.50mH,Vd=40.0V,Vgon=10.0V,Vgoff=0.0V,

Rg=25ohm,TestMode=Mode2

(图2)

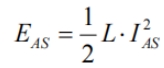

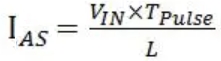

雪崩泄放的总能量由以下公式可得知:

其中:

因为在实际的测试中,我们通常会固定L和VIN的值,所以我们只要通过不断增大脉宽宽度TPulse,测得器件不损坏的最大雪崩耐量即为所测器件的EAS值。

重复雪崩耐量

图3给出了重复雪崩测试的原理图,对待测器件的Gate施加周期性开关信号,通过器件反复开关,周期性对电感储能,并通过器件雪崩释放能量。对于重复雪崩,每次发生雪崩的能量要比EAS小很多,但重复累加的能量会比单脉冲雪崩多很多,所以芯片结温和管壳温度都会升高,当芯片结温达到Tjmax时,即为所测器件的EAR最大值。

(图3)

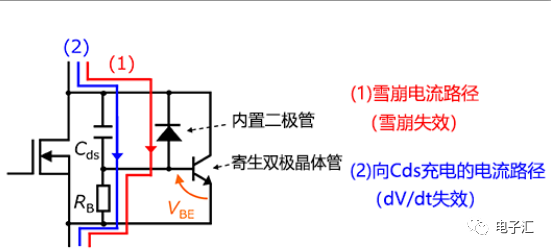

三、雪崩击穿的失效机理

虽然当功率器件承受的雪崩耐量超过极限后,芯片都会发生损坏,但是单脉冲雪崩与重复雪崩的失效机理却并不相同。

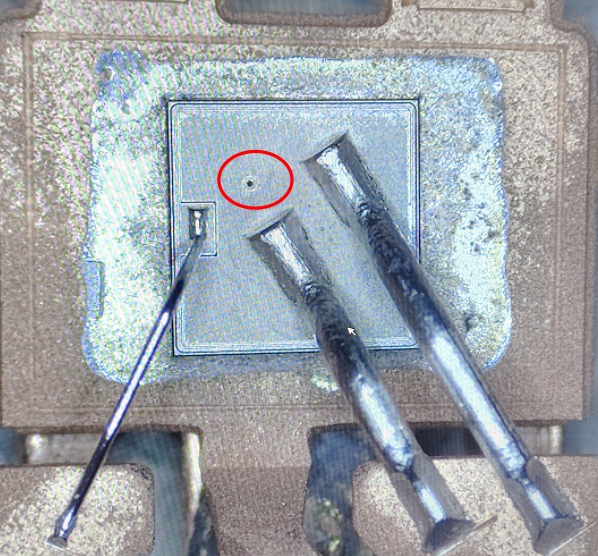

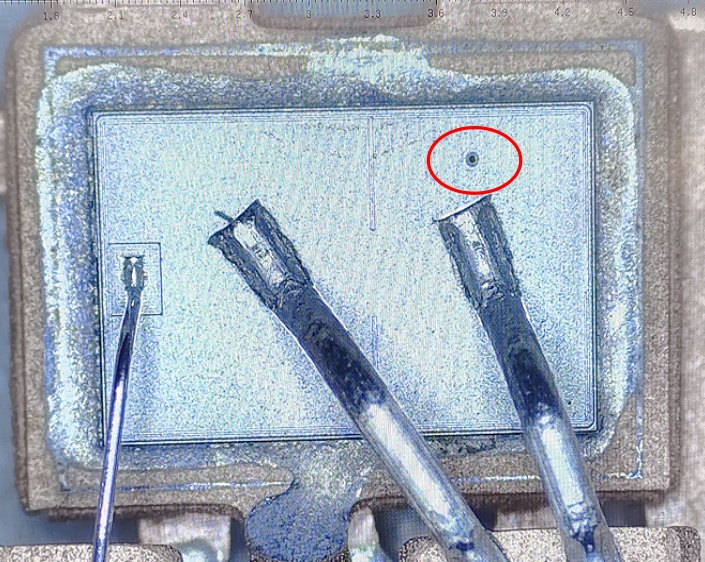

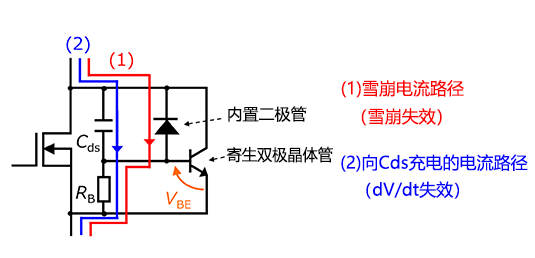

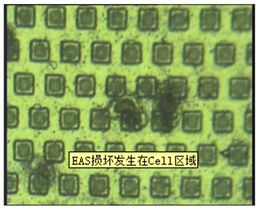

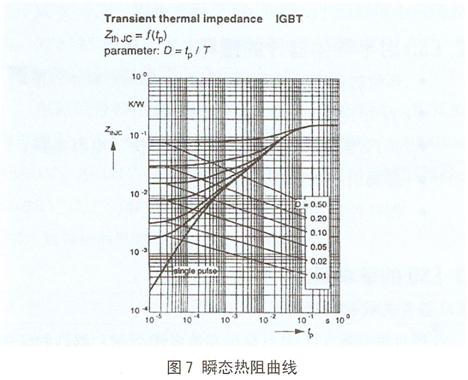

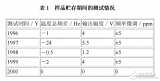

在单脉冲雪崩发生时,持续的时间一般在微秒量级,我们发现由于热容的存在,瞬时热量不足以传递到芯片引线框和封装体,所以雪崩击穿位置的温度会急剧上升,当超过芯片内部PN结极限温度(约200℃)时,芯片会存在过热击穿损坏。单脉冲雪崩的极限温度限制是PN结的热击穿温度,而非器件手册标称的最高工作温度Tjmax(150℃)。重复雪崩的失效机理主要有两种,一种是重复雪崩过程中芯片结温超过Tjmax而带来的器件损坏;另一种表现为在重复雪崩老化过程中,由于热载流子效应而带来的器件参数漂移,这是一个缓慢退化的过程,图4,图5给出了器件在雪崩击穿后局部的损坏形貌。

(图4)

(图5)

四、如何在应用中提升器件雪崩能力

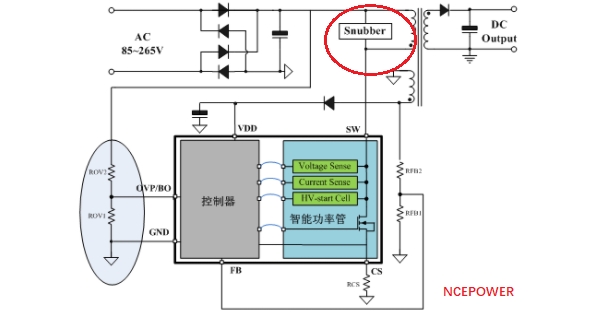

雪崩耐量是功率器件关键指标,我们以开关电源举例,在反激式开关电源中一般都会配置RCD吸收回路来抑制雪崩发生(如图6,图7)。

(图6)

(图7)

RCD的工作过程,是当MOS管导通,电压流过变压器初级线圈,对线圈充电,当MOS管关闭后,电感产生反电动势,变压器次级通过二极管输出电压,由于初级线圈有漏感,不能全部转移到次级,多余的能量就会和电源电压叠加,产生VDS尖峰电压,尖峰电压通过二极管对电容充电,在MOS再次导通时,电容上的电压通过电阻放电,把多余的能量通过电阻消耗掉,RCD的一个工作周期完成,继续循环下一个周期。

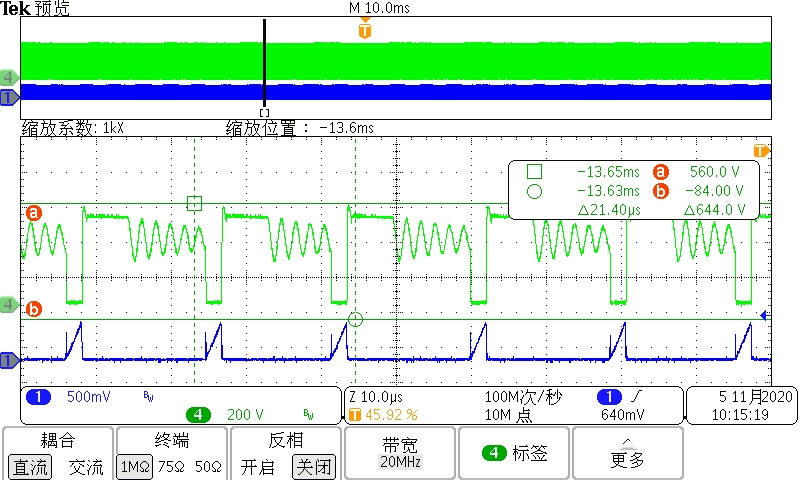

我们以开关电源原边侧功率管的DRAIN波形为例(绿色),如图8是未增加RCD回路的VDS尖峰波形,尖峰电压596V,图9为增加RCD回路的VDS尖峰波形,尖峰电压560V,可以看到尖峰电压有了明显改善,整个系统的雪崩能力也得到了提高,可靠性大幅增强,所以我们选择雪崩耐量优异的分立器件或与之匹配的吸收回路是与整个电源系统可靠性紧密相关的。

(图8)

(图9)

-

MOSFET

+关注

关注

147文章

7160浏览量

213190 -

雪崩击穿

+关注

关注

0文章

23浏览量

7619 -

功率器件

+关注

关注

41文章

1763浏览量

90421

原文标题:功率器件-MOSFET的雪崩耐量机理与扩展

文章出处:【微信号:NcePower,微信公众号:无锡新洁能股份有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

什么是击穿?雪崩击穿和齐纳击穿有什么区别?

雪崩击穿,雪崩击穿是什么意思

MOSFET的失效机理:什么是雪崩失效

功率器件雪崩击穿的工作原理和失效机理

功率器件雪崩击穿的工作原理和失效机理

评论