时钟控制

主机可以使用SD Memory Card总线时钟信号将卡切换到节能模式或控制总线上的数据流(以避免欠运行或过运行)。主机不允许降低时钟频率或关闭时钟。

例如,在具有512字节数据缓冲区的主机希望将数据传输到具有1kbyte写块的卡的情况下。因此,为了保持所有数据的连续传输,从卡的角度来看,到卡的时钟应该在第一个512字节之后停止。然后,主机将用另一个512字节填充其内部缓冲区。在主机中写块的后半部分准备好后,它将通过重新启动时钟电源继续向卡传输数据。这样,卡就不能识别数据传输中的任何中断。有一些限制是HOST应该考虑的:

总线频率可随时更改(受最大数据传输频率和规范文件定义的识别频率的限制.

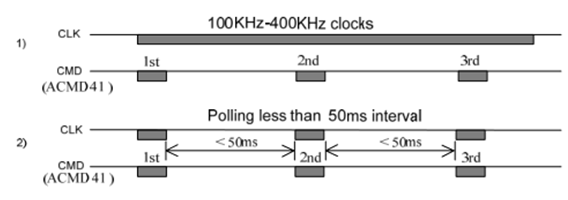

上述豁免是ACMD41 (SD_APP_OP_COND)。发出ACMD41命令后,由主机执行以下1)或2)程序,直到卡准备就绪。

1)发出100 KHz-400 KHz频率范围内的连续时钟。如果主机想要停止时钟,则通过ACMD41命令以小于50 ms的间隔轮询忙位。

这是一个明显的要求,时钟应该运行的卡输出数据或响应令牌。在最后一次SD存储卡总线事务之后,要求主机在关闭时钟之前提供8(eight)个时钟周期供卡完成操作。以下是各种总线事务的列表:没有回应的命令。

8个时钟主机命令结束位之后。带有响应的命令。

8个时钟在卡响应结束位之后。读数据事务。

8个时钟在最后一个数据块的结束位之后。写数据事务。

8人时钟在CRC状态令牌之后。允许主机关闭“忙”卡的时钟。

无论主机时钟如何,卡都将完成编程操作。但是,主机应该为卡提供一个时钟边缘来关闭它的忙音信号。如果没有时钟边缘,卡(除非先前通过取消选择命令cmd7断开连接)将永远迫使DAT线向下。

CRC (Cyclic Redundancy Code)

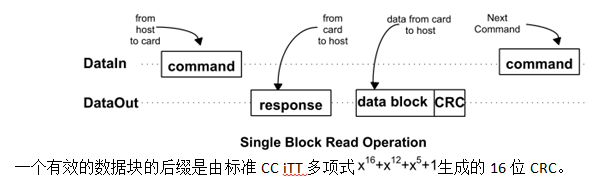

CRC旨在保护SD存储卡命令、响应和数据传输,防止SD存储卡总线上的传输错误。为每个命令生成一个CRC,并检查CMD行上的每个响应。对于数据块,每个传输的块生成一个CRC。生成并检查CRC,如下所述。

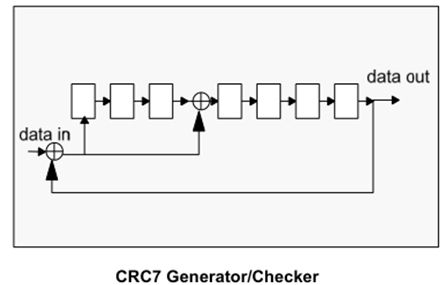

CRC7

CRC7检查用于所有命令、除类型R3之外的所有响应以及CSD和CID寄存器。CRC7是一个7位值,计算方法如下:

第一个位是对应的位串(命令、响应、CID或CSD)的最左边的位多项式的阶n是CRC保护位的个数减少1。命令和响应(n = 39)需要保护的比特数为40,CSD和CID (n = 119)需要保护的比特数为120。

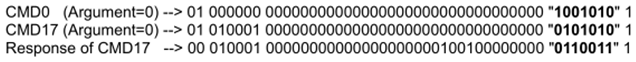

CRC7例子

命令/响应的CRC部分被保留。

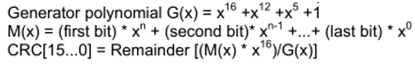

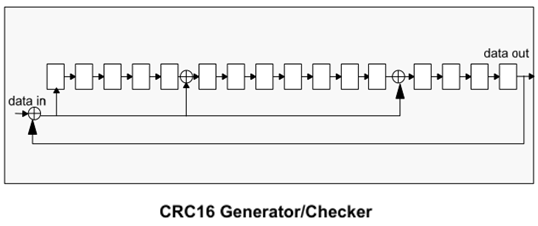

CRC16

在使用一条DAT线路的情况下,CRC16用于块传输模式下的有效负载保护。CRC校验和是一个16位的值,计算方法如下:

第一个位是相应块的第一个数据位。多项式的度n表示数据块的位数减少1

(例如,块长度为512字节时为e.g.n =4095)。发生器多项式G(x)是一个标准的CCITT多项式。代码的最小距离为d-4,用于负载长度为2048字节(n <= 16383)。在单数据线模式和宽总线模式下应使用相同的CRC16方法在宽总线模式下,CRC16在每条线路上分别完成。

CRC16例子

512字节的0xFF data-->CRC16=0x7FA1

错误条件

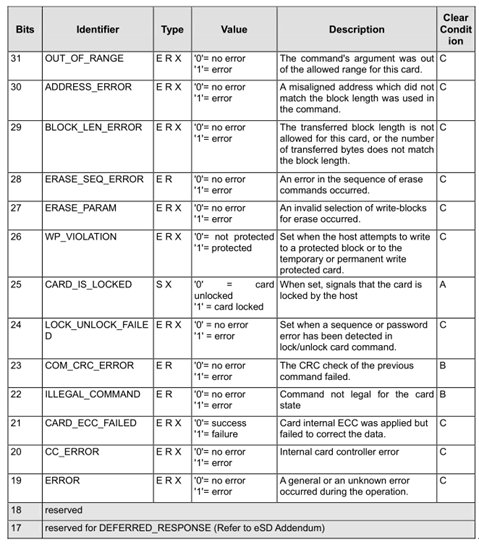

CRC与非法命令

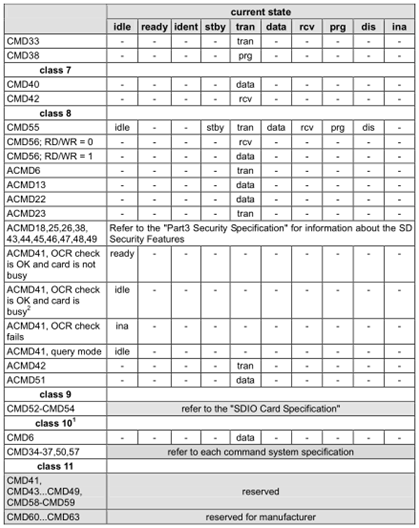

所有命令都由CRC (cvclic redundancy check)位保护。如果地址卡的CRC检查失败,则该卡不响应,命令不执行。卡不改变它的状态,并且在状态寄存器中设置了COM CRC ERROR位。同样,如果接收到非法命令,卡将不改变其状态,不响应,并在状态寄存器中设置ILLEGAL_COMMAND错误位。状态图中只显示非错误状态分支。下表给出了完整的状态转换描述。

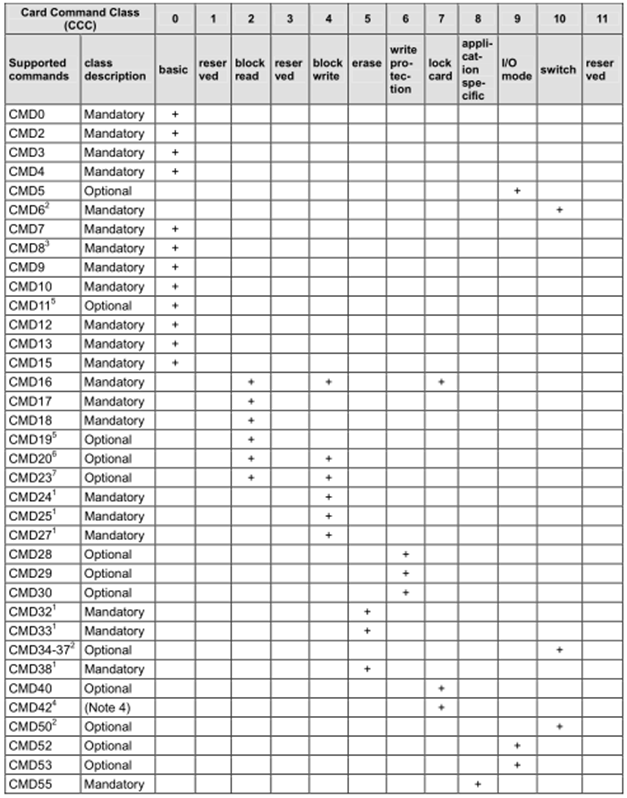

非法命令有不同的类型:属于卡不支持的类的命令(如:只读卡中的写入命令)。

当前状态下不允许的命令(如:CMD2处于传输状态)。

未定义的命令(如:CMD5)。

审核编辑 黄宇

-

存储

+关注

关注

13文章

4314浏览量

85851 -

crc

+关注

关注

0文章

199浏览量

29465 -

SD NAND

+关注

关注

0文章

83浏览量

1239

发布评论请先 登录

相关推荐

瀚海微SD NAND之SD 协议(37)SPI总线保护和读写

瀚海微SD NAND存储功能描述(28)RCA Registers

瀚海微SD NAND存储功能描述(25)SD Registers

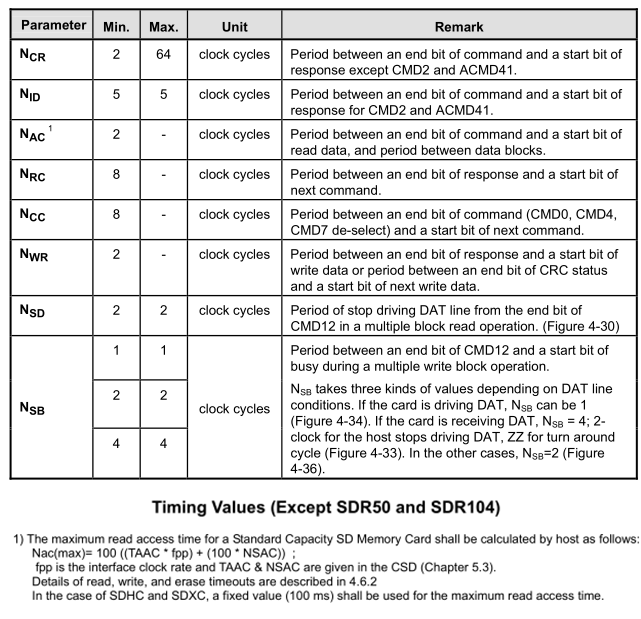

瀚海微SD NAND存储功能描述(22)Timing Values

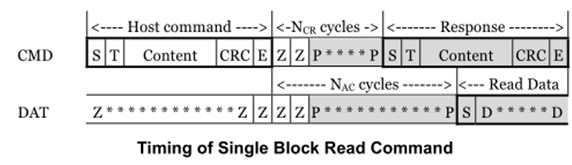

瀚海微SD NAND存储功能描述(21)数据读写

瀚海微SD NAND存储功能描述(17)命令类d

瀚海微SD NAND存储功能描述(14)命令类a

瀚海微SD NAND存储功能描述(11)命令系统CMD8

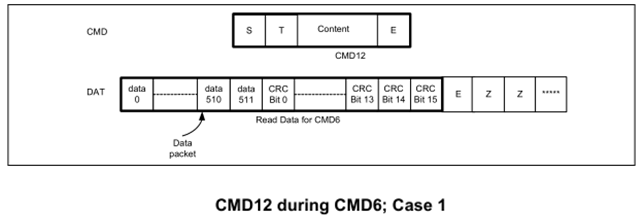

瀚海微SD NAND存储功能描述(10)CMD6和其他命令关系

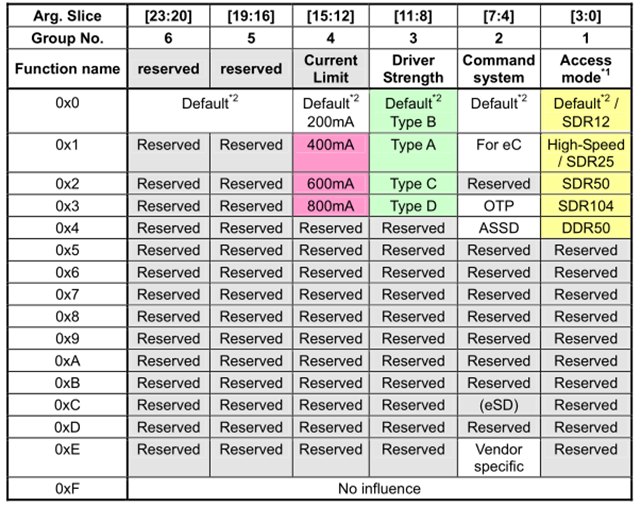

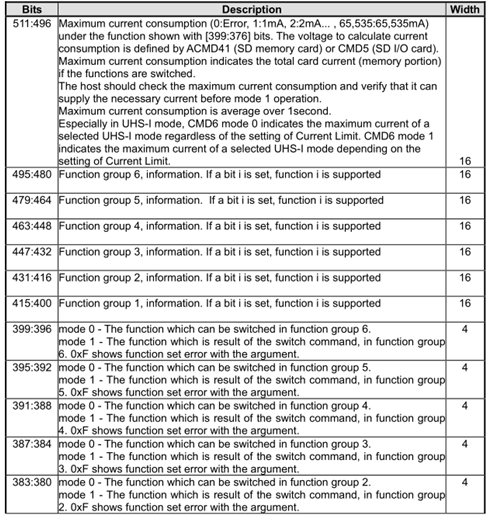

瀚海微SD NAND存储功能描述(9)切换功能

瀚海微SD NAND应用之SD协议存储功能描述2 初始化命令

SD NAND:儿童玩具的多功能存储神器

瀚海微SD NAND存储功能描述(12)时钟控制和CRC

瀚海微SD NAND存储功能描述(12)时钟控制和CRC

评论