主从触发器(又称为脉冲触发器)和边沿触发器在波形上的比较主要体现在它们的触发方式和输出响应上。以下是对两者波形比较的具体分析:

一、触发方式

- 主从触发器 :

- 边沿触发器 :

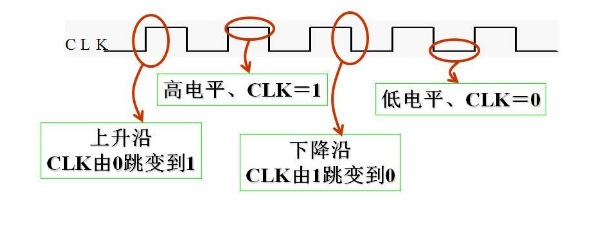

- 边沿触发器仅在时钟信号的约定边缘(如上升沿或下降沿)到来时接收输入信号,并更新其输出状态。

- 在时钟信号的其他阶段(如高电平或低电平期间),边沿触发器不响应输入信号的变化。

- 边沿触发器的输出状态变化直接由时钟信号的边缘和此时的输入信号共同决定。

二、波形特性

- 主从触发器 :

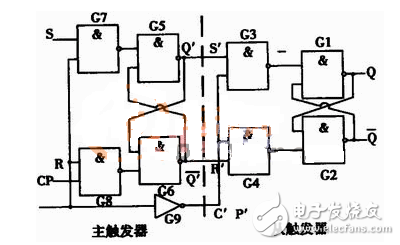

- 主从触发器的波形图通常显示出两个阶段的特征:主触发器接收信号阶段和从触发器更新输出阶段。

- 在CLK为高电平时,主触发器的输入变化可能会被检测到,但这些变化不会立即反映到输出上。

- 直到CLK的边缘到来,从触发器才根据主触发器的状态更新其输出,这可能导致输出波形相对于输入信号有一定的延迟。

- 边沿触发器 :

- 边沿触发器的波形图更加直接地反映了输入信号和时钟信号边缘之间的关系。

- 当时钟信号的边缘到来时,边沿触发器立即根据此时的输入信号更新其输出状态。

- 由于边沿触发器只在时钟信号的边缘时刻接收输入信号,因此它的输出波形通常更加清晰、稳定,且没有不必要的延迟。

三、抗干扰能力

- 边沿触发器通常比主从触发器具有更强的抗干扰能力。这是因为边沿触发器只在时钟信号的边缘时刻接收输入信号,这大大减少了输入端受干扰的时间窗口。相比之下,主从触发器在CLK为高电平时都会接收输入信号,这使得它更容易受到输入端干扰的影响。

综上所述,主从触发器和边沿触发器在波形上的主要区别在于它们的触发方式和输出响应特性。边沿触发器由于只在时钟信号的边缘时刻接收输入信号并更新输出状态,因此通常具有更强的抗干扰能力和更稳定的输出波形。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

主从触发器

+关注

关注

0文章

13浏览量

6387 -

输入信号

+关注

关注

0文章

455浏览量

12553 -

时钟信号

+关注

关注

4文章

448浏览量

28546 -

边沿触发器

+关注

关注

0文章

34浏览量

3983

发布评论请先 登录

相关推荐

主从触发器,主从触发器的原理和特点有哪些?

主从触发器,主从触发器的原理和特点有哪些?

1.电路组成和符号 主从RS触发器电路和逻辑符号如图Z1406所示。其中A、

发表于 03-08 14:06

•1.2w次阅读

边沿触发器波形图

主从触发器可以有效克服钟控触发器的空翻现象,但主从触发器还存在一次翻转现象,降低了抗干扰能力。边沿触发器:只有在CP的上升沿(前沿)或下降沿

发表于 01-31 10:38

•2.4w次阅读

主从rs触发器波形图介绍

主从触发器由主触发器和从触发器组成,时钟信号CP经由非门,变成CP’控制从触发器。当CP=1时,CP‘=0,主触发器动作,从

发表于 02-08 13:40

•2.2w次阅读

主从触发器和边沿触发器的区别是什么

主从触发器(Master-Slave Trigger)和边沿触发器(Edge Trigger)是数字电路中两种不同类型的触发器。它们在设计和功能上有一些关键的区别:

主从触发器都是下降沿触发吗

主从触发器(Master-Slave Flip-Flop)是一种常见的数字逻辑电路,用于存储一位二进制信息。主从触发器通常由两个触发器组成,一个作为主触发器,另一个作为从

主从触发器和同步触发器的区别在哪里

定义: 主从触发器(Master-Slave Trigger)是一种用于实现时钟同步的触发器结构,它由两个触发器组成,一个为主触发器(Master Trigger),另一个为从

主从触发器和脉冲触发器的区别是什么

主从触发器和脉冲触发器是数字电路中常见的两种触发器类型,它们在逻辑功能、电路结构、工作原理等方面存在一些区别。 定义和功能 主从触发器(Master-Slave Flip-Flop)是

主从触发器和边沿触发器的特点及应用

在数字电路设计中,触发器是一种非常重要的基本逻辑元件,用于存储一位二进制信息。触发器的种类繁多,但主要分为两大类:主从触发器(Master-Slave Flip-Flop)和边沿

主从触发器和边沿触发器的区别

主从触发器和边沿触发器是数字电路设计中常用的两种触发器类型,它们在触发机制、动作特点、应用场景等方面存在显著的区别。以下是对两者区别的详细阐

主从jk触发器和边沿jk触发器的区别

主从JK触发器和边沿JK触发器是数字电路中常用的存储元件,它们在功能和应用上既有相似之处,也存在显著的区别。以下将从多个方面介绍这两种触发器

主从触发器和边沿触发器波形比较

主从触发器和边沿触发器波形比较

评论