一、规则设置

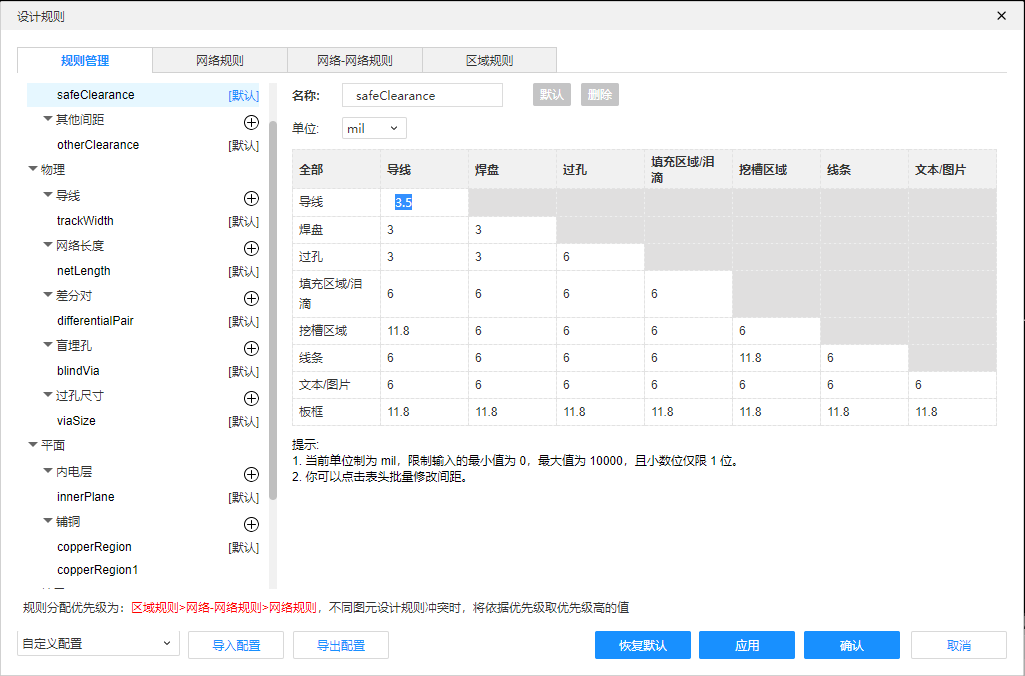

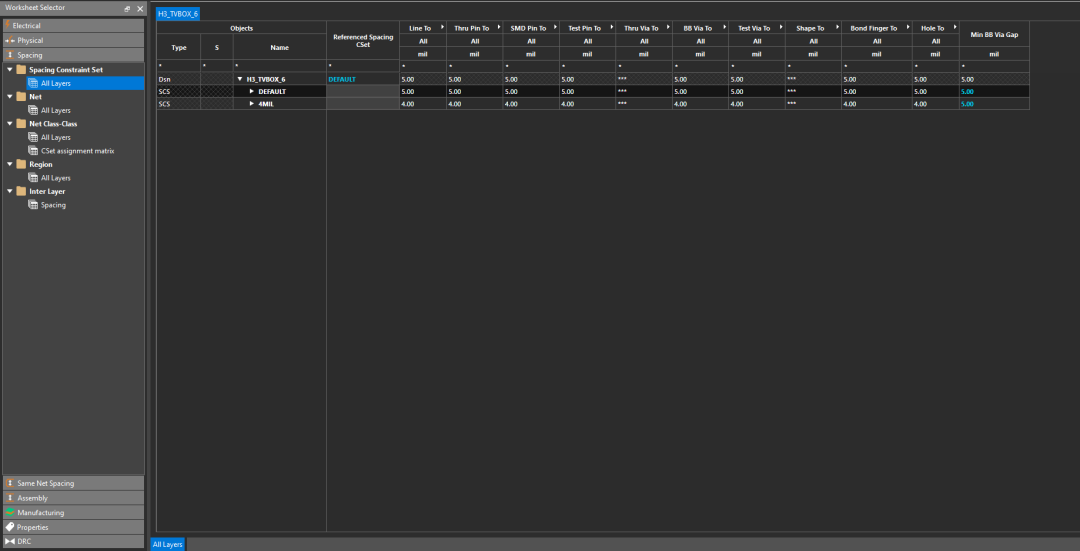

使用EDA设计时,首先进行PCB的规则设置,一般规则设置比较重要的有间距设置、物理规则、平面规则、网络设置。分别展示立创EDA和Allegro的规则设置界面。

立创EDA的规则设计更直观,而Allegro的规则设置则更全面。

具体的规则设置则是根据当前绘制PCB来决定的,同时需要参考板厂生产工艺给定的参数来进行设置。如嘉立创打板时,多层板线距要求大于3.5mil时不额外收取工艺费,这时就需要在安全距离的导线到导线的距离中设置为至少3.5mil/0.089mm。

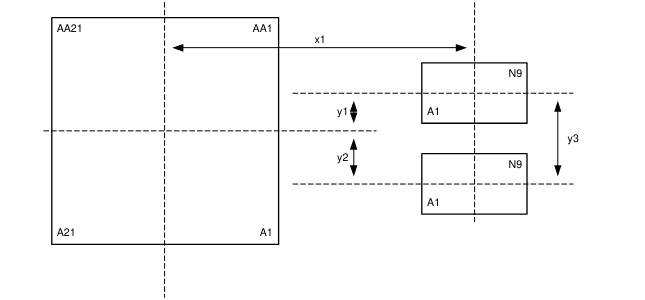

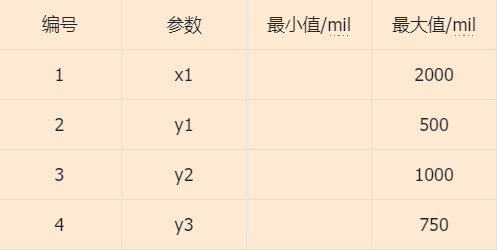

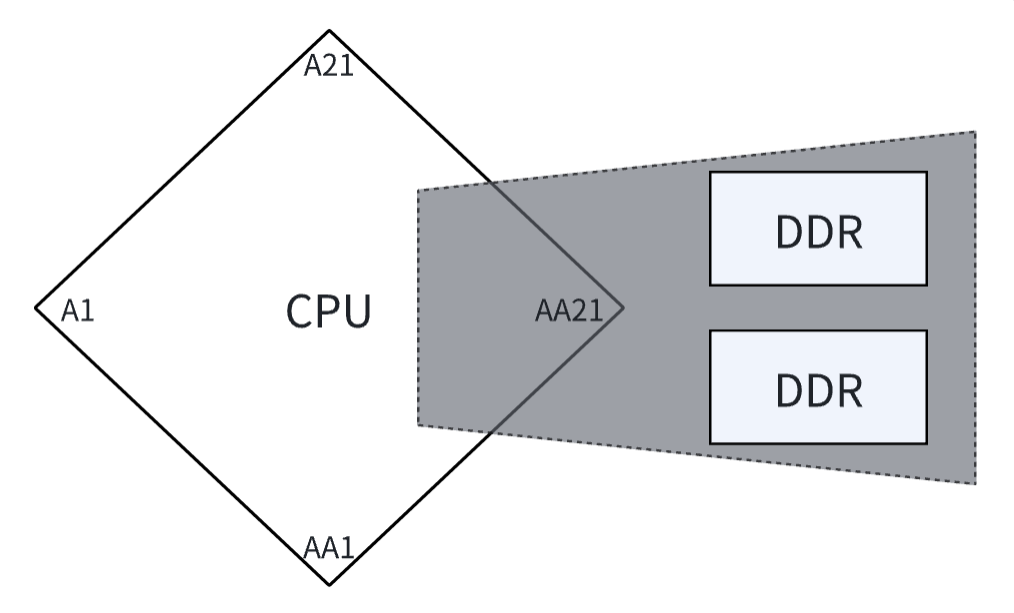

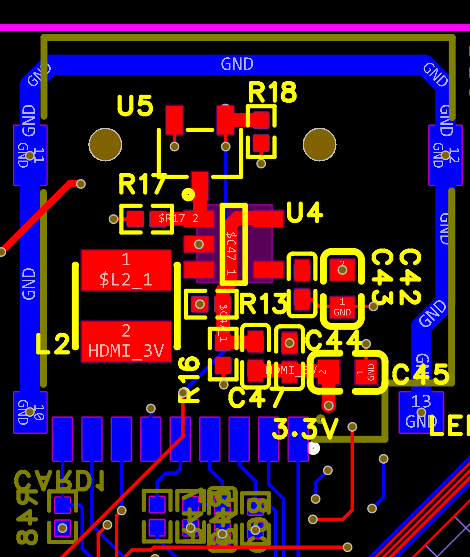

在这些模块中CPU和DDR均为BGA封装,此部分布线有难度,应当优先处理。CPU和DDR的布局可参照下图。

本图只是示意图,放置的最终目的是限制最大布线长度并流出适当的布线空间。

用于DDR电路的区域必须与其他信号隔离开,如下图所示。这个禁止区域的大小应该根据DDR的放置和布线决定。对于非DDR信号,不能在禁止区域内的DDR信号层上走线。只有在通过接地层与DDR信号层隔离开来的其他层上布线时,非LPDDR才能在该区域中布线。一般走线时应该尽量将该区域绕过。

如上图所示,本次布局CPU和DDR采用此布局,灰色部分则是DDR隔离区,DDR信号可以在这里放置,非DDR则最好不要经过这个区域,并且使用包地的方式进一步隔离该区域。

三、CPU及DDR布线要点

走线时应该尽量满足3W规则,即两条导线中心的距离至少为线宽的三倍(如导线线宽5mil,两条导线中心距离应为15mil,两导线边距则是10mil,即2W)。这样布线能有效防止信号之间的串扰。

布信号线时应注意阻抗匹配以及等长布线。等长布线时先将各组线分组设置,这个功能在立创EDA和Cadence中均可实现,详见另一篇文档。阻抗匹配:单端50Ω,差分100Ω。计算阻抗匹配的工具有很多,如果是在嘉立创进行绘制可以直接使用嘉立创阻抗计算神器,也可以使用如ICD Stackup Planner、SI9000等专业阻抗计算软件。

同组信号中优先拉差分信号线,同时需要留足空间以方便后续做等长。

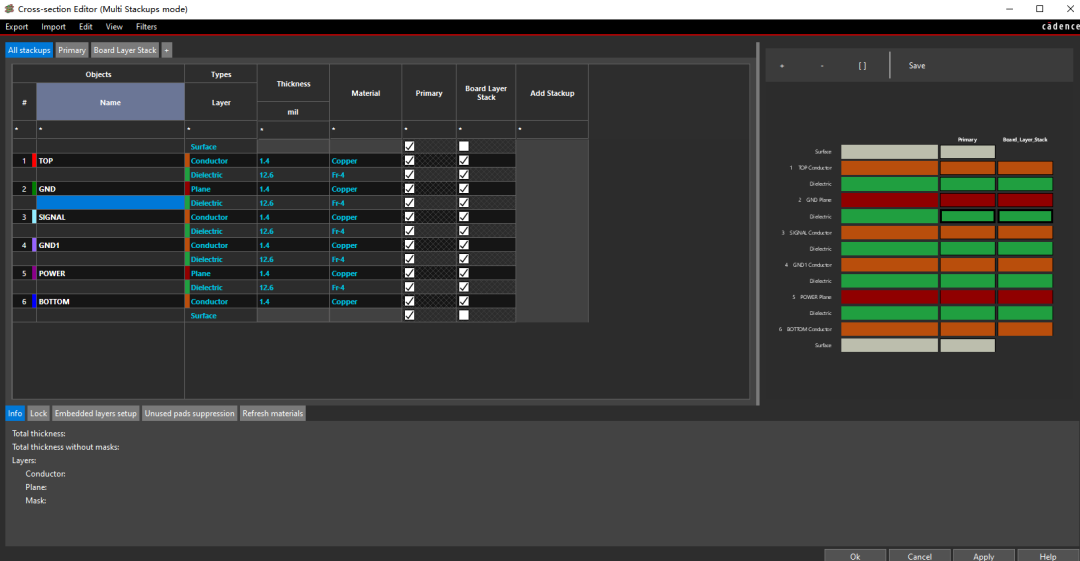

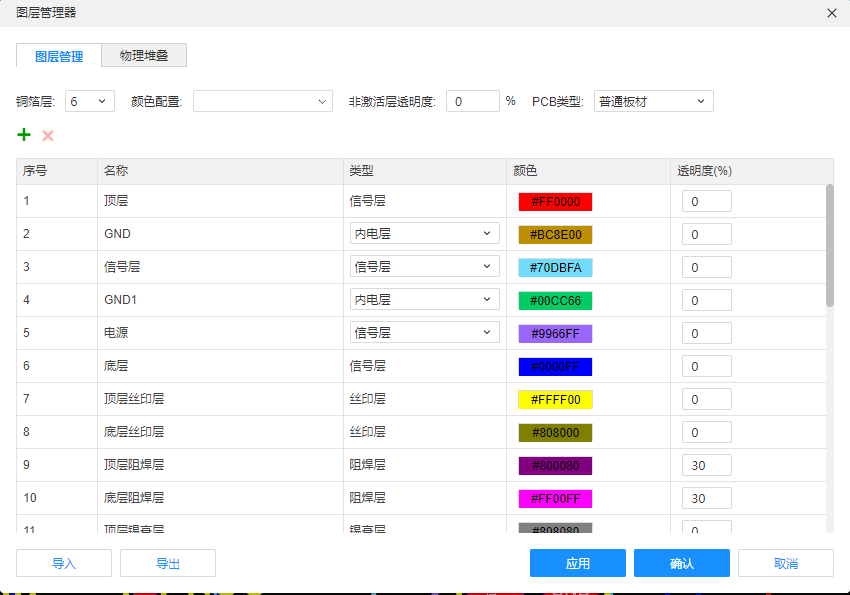

设置参考平面,这个参考平面一般为地平面,因此设计时需定义好叠层。信号线尽量不走顶层和底层,而是走中间层,因为中间层的数据传输速率相较于顶层和底层快,顶层和底层少走线也利于摆放器件。

分别展示Allegro和立创EDA的叠层管理器,六层板的叠层设计一般为信号层——地平面——信号层——地平面——电源层——信号层。这样设置可以保证信号线的参考平面总为地平面。

四、电源部分布局布线要点

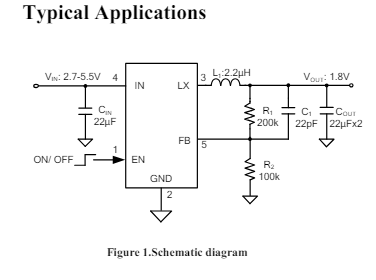

本设计电源较多且多使用DCDC电源芯片,因此电源部分布线一定要注意一下事项:典型电路:一般典型电路都可以从数据手册中找到,如本次使用的DCDC电源芯片SY8089A:

设计时需要参考官方手册给出的典型电路来选取各元器件的值。同时,部分元器件的数值选取可以参考数据手册中给出的计算公式计算,以匹配自己设计的电路。

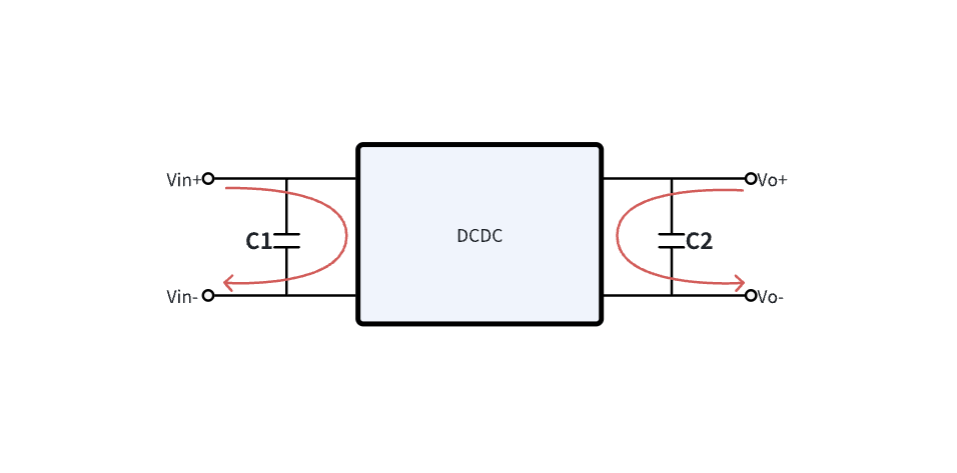

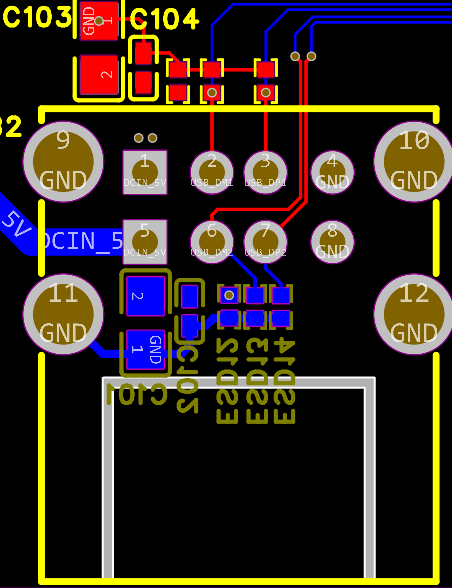

电流路径:

回流路径如红色箭头所示,其中C1、C2是输入和输出电容,这两个电容的作用为减小输入电流和输出电压的纹波。

回流路径如红色箭头所示,其中C1、C2是输入和输出电容,这两个电容的作用为减小输入电流和输出电压的纹波。

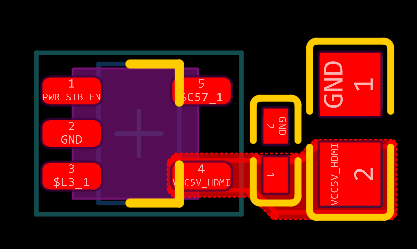

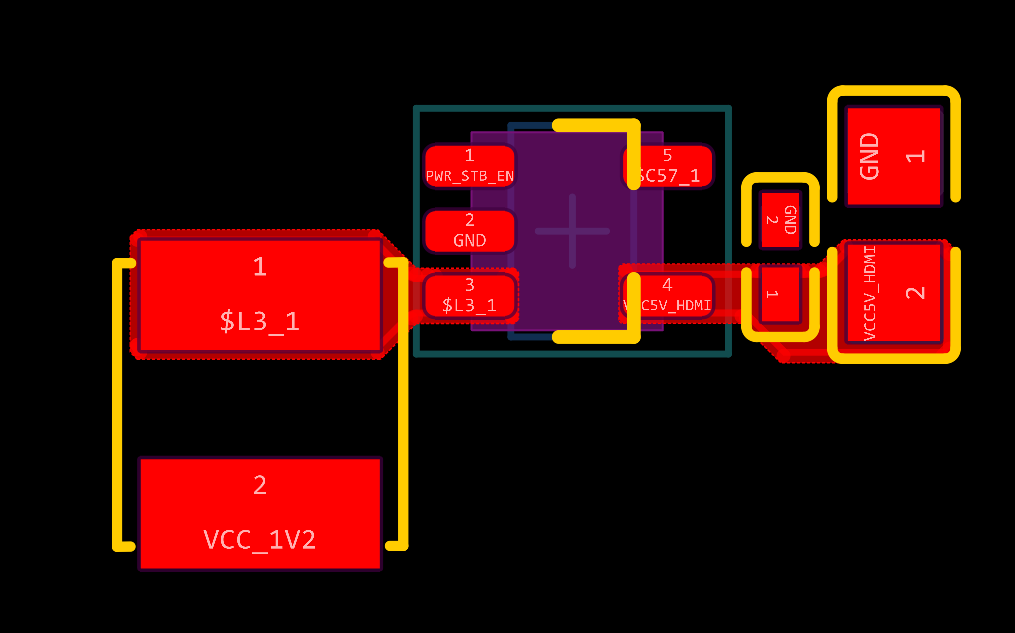

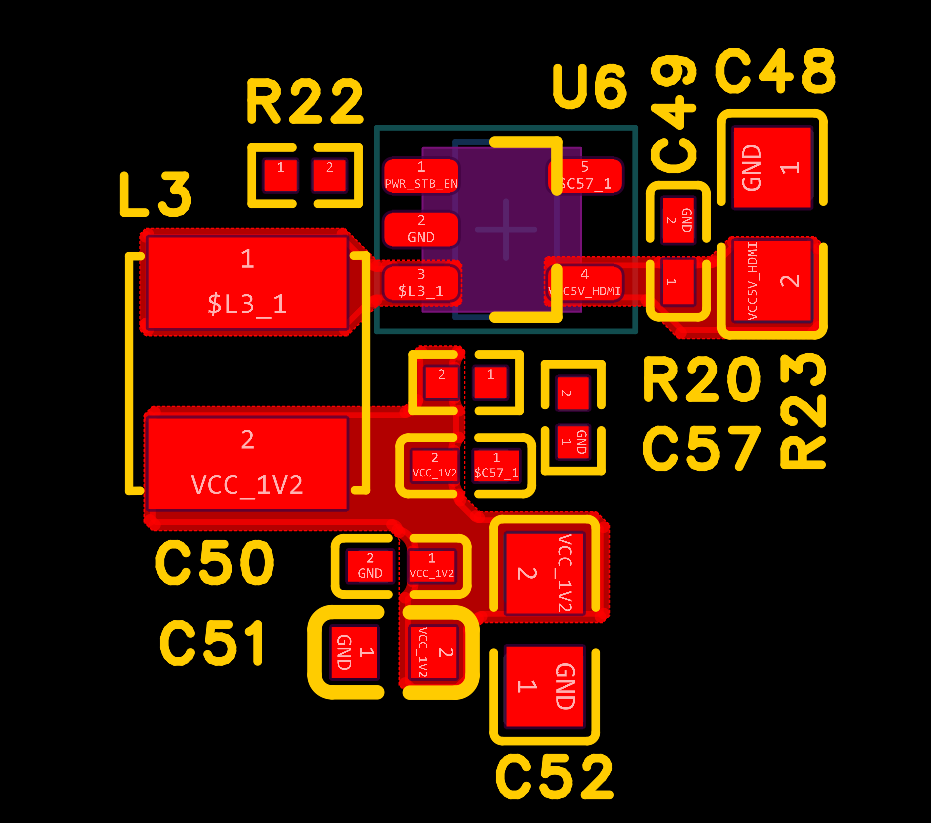

器件布局:

其中输入电容对于任何降压型转换器件来说都是实现其可靠操作的重要器件。因此,在放置完IC后应该首先安放输入电容。放置了输入电容后立即布线将之与IC连接,这样在其走线排布的路径中就不会有其他的器件及走线穿过了。输入电容的电源与接地之间以及IC的VIN和GND之间的额外寄生电感将由于开关动作而产生过大的电压尖峰(V=L*di/dt),这个电压尖峰有可能导致IC故障。

所以,输入电容应该尽可能靠近IC引脚,且走线尽可能粗、短,利用如此连接方式尽可能的减小寄生电感。

在布局中,第二重要的是电感。电感尽量放置在靠近IC处,并保持尽可能小的SW节点铺铜面积。连接SW节点的所有铜箔相当于电容的一块极板,而另一块极板则是电路中的每一点,这个电容是一个噪声耦合路径。通过使SW节点很小,可以最大限度的减少电容极板的面积并减小耦合。

输出电容是完成功率布线的最后一步。其为系统中连接至电源接地端的最终器件,而且它的摆放位置旨在尽可能缩短从电感器背部至电源接地的距离。输出电容如果摆放不当通常会引起不良的输出电压调节。

每种功率器件的安置和布线以尽量缩短它们之间的距离为宗旨。使这些环路面积保持很小可实现SMPS(即开关模式电源)的最佳运作。

除了功率器件外还有一些小信号器件,如:EN(使能)、FB(反馈)、PG(检测)等。噪声较高的功率器件及其节点产生噪声,而interwetten与威廉的赔率体系 小信号器件容易受到噪声干扰。所以应该采用简短和直接的布线将这些器件布局在靠近IC的地方,以尽量防止噪声对其的影响。特别需要注意,必须尽可能使FB节点保持小巧,以最大限度地减少噪声并提供优良的输出电压调节能力。

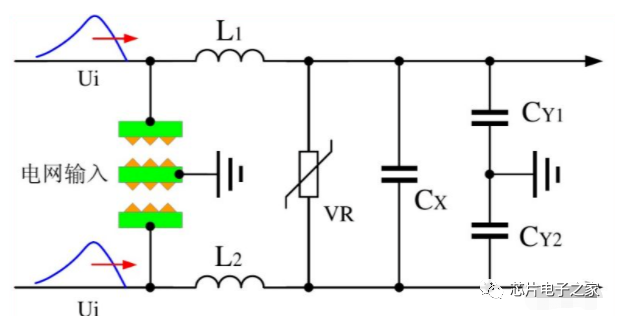

五、HDMI布局布线要点

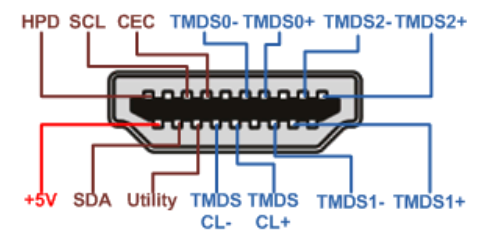

HDMI连接器中有四对最小化传输差分数字信号(TMDS)通道;热插拔检测 (HPD) 通道,可检测何时建立连接;消费 类电子控制 (CEC) 通道,允许用户通过 HDMI 控制器件;实用通道,用于 HDMI 以太网或音频返回通道;SDA 和 SCL 通道,可提供 I2C 控制;以及最后一个通道,可提供 5V 电源。

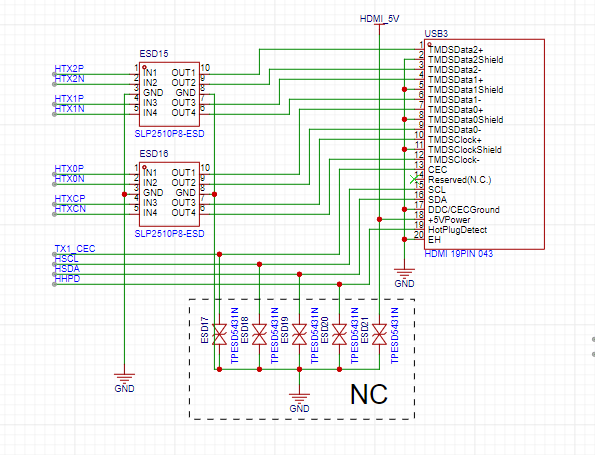

为了防止ESD故障,可以通过 HDMI 连接器将 5V 工作电压、TVS 二极管放置在各通道上。此外TMDS通道为高速线(对于 HDMI 2.0 而言可达18Gbps),放置在这些高速布线上的 ESD 保护二极管要求电容足够低,以保持信号完整性并满 足 HDMI 合规标准。

ESD器件在布局上应该尽可能靠近HDMI引脚,但是也不能太近,考虑到焊接,其距离最好控制在烙铁头能够焊接的距离上(1.5mm左右);

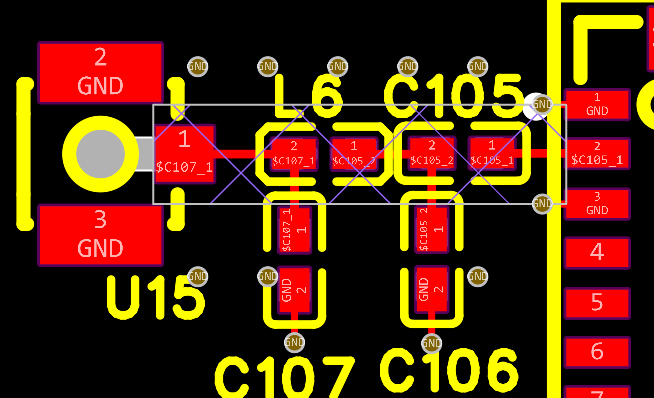

HDMI中六个TMDS通道为三组差分信号,在布线时按照差分线规则引线,换层布线尽量不要超过两次,尽可能不打孔换层。差分对走线需要做100Ω阻抗匹配,阻抗匹配在CPU及DDR布线中有提到。使用坚实的电源层和接地层来实现 100Ω 阻抗控制,以及电源噪声最小化。即差分走线下面应该是完整的参考平面。

HDMI接口的5V电源靠近接口来放置即可,不宜太远;

HDMI走线<3000mil,并行走到连接处即可,不要使用蛇形走线;

差分对内等长误差<200mil,差分对间尽量等长,误差<1000mil即可;

尽可能使HDMI连接器和器件之间的电气长度保持最短,从而使衰减最小化。

六、WIFI模块布局布线要点

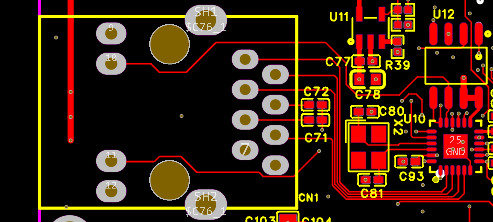

Linux开发板中WIFI使用模块RTL8189ETV,因此布局布线重点在天线的放置位置处。模块需要自己搭建射频电路(RFIOP)。

为保证损耗最小,RF走线尽量短,元件之间尽量排紧凑一些;RF走线尽量走直线,不要使用直角走线,走线宽度以及走线和外围 GND 的间距推荐0.5mm。因PCB 板材和介质会影响 RF 走线阻抗,为保证 RF 走线的阻抗为 50Ω,可以适当调整走线宽度以及走线和外围 GND 的间距。

RF尽量一字走线,如果空间受限无法一字走线,可使用L形走线,但不能使用U形走线。

RF走线四周一定要包地处理,上下层通过GND过孔连接。

射频部分布局尽量靠近板边,尽可能远离强辐射信号(高速信号等)。

七、EMAC布局布线要点

Linux开发板中使用了两个以太网接口,其中一个使用以太网转换芯片。以太网转换芯片PHY和变压器之间的距离也应该尽可能的短,距离一般不超过127mm,若RJ45接口自带变压器,则以太网转换芯片尽可能的靠近RJ45接口放置。时钟电路应当尽可能的靠近以太网转换芯片,远离电路板的边缘以及其它高频信号、IO端口走线和其它磁性元器件。

八、TF卡布局布线要点

VCC_SD的电容需要靠近卡座引脚放置进行滤波,遵循先大后小的原则。

TF卡尽量放置在板边,方便插拔,ESD器件要靠近TF卡来放置,走线需要先经过ESD器件再进入SD卡,不要打孔穿;

TF卡走线为单端线,控制阻抗50欧姆;

所有的信号线尽量走在同一层,这样有利于信号的一致性,走线与高频信号隔开,空间准许的情况下,单根包地,空间紧张的情况下整组进行包地处理,走线需要有完整的参考平面;

TF卡的时钟信号,与其他信号线的间距保证20mil左右,有空间的情况下,包地处理;

组内数据线不要相差太大,需要控制400mil以内,走线总长度不要太长尽量控制在317.5mm之内,以提高稳定性和兼容性。

在打孔换层的地方加回流地过孔,缩短回流了路径。

九、USB布局布线要点

USB应该接口靠近板边或结构定位放置,伸出板边一定位置(直插除外),方便插拔;

注意ESD和USB的距离,留有一定的的间距,考虑后焊的情况;

在布局时,尽量使差分线路最短,以缩短差分线距离;

USB要走差分,阻抗控制为90欧姆,并包地处理,总长度最好不要超过1800mil;

尽可能缩短走线长度,优先考虑对高速USB差分(RX、TX差分)的布线,USB差分走线在走线的时候,尽可以有的减少换层过孔,从而可以更好的做到阻抗的控制,避免信号的反射。

-

DDR

+关注

关注

11文章

712浏览量

65318 -

布线

+关注

关注

9文章

771浏览量

84322 -

PCB布局

+关注

关注

9文章

183浏览量

27838 -

EDA设计

+关注

关注

1文章

47浏览量

13682

发布评论请先 登录

相关推荐

PCB规划/布局和布线的设计技巧和要点

PCB布局布线11个要点资料下载

干货!PCB布局布线九大最全要点

干货!PCB布局布线九大最全要点

评论