高速信号的定义

在数字电路中,高速信号通常指的是指在超过信号传输线上限频率时会发生失真、波形变形或者数据丢失的信号。这种高速信号的频率通常超过几十兆赫兹,甚至可以达到几个G赫兹。对于高速信号的传输,传统的数字逻辑设计已经不能满足需求,因此需要深入了解高速信号传输的方式和原理,此文不对此做详细的介绍。

以下几种针对高速信号的定义,在某种意义上都具有合理性,比如:

A.当信号的上升时间小于6倍信号的传输延时是高速信号

B.当频率大于50MHZ的信号是高速信号

C.当信号的边沿时间小于100PS的时候被认为是高速信号

D.考虑趋肤效应和电离损耗带来的影响时的信号是高速信号

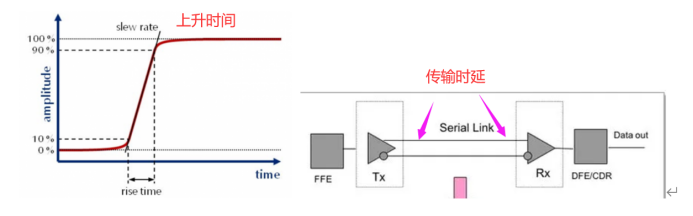

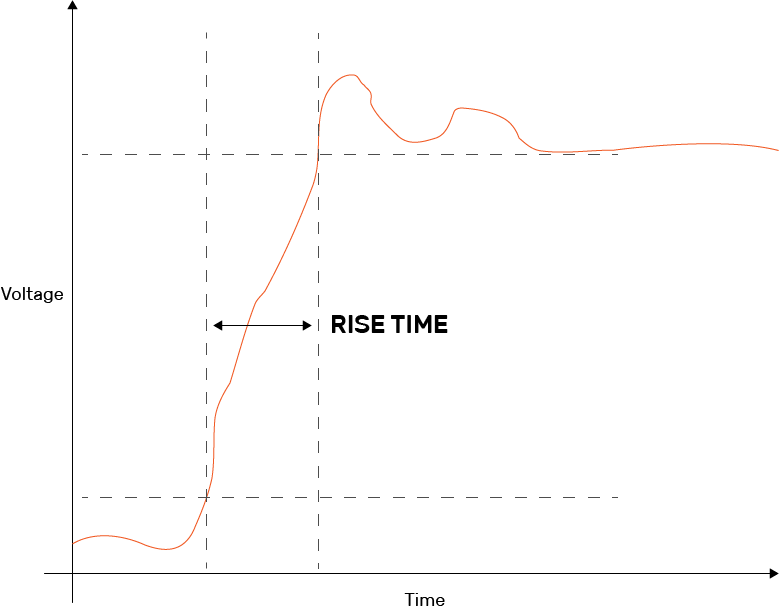

以上不同的应用场景都可以作为高速信号的判别标准,此文我们重点讨论一下A场景:上升时间小于6倍信号传输延时。传输延时按照信号的总长度除以信号传播速度进行计算,信号传播速度约等于6mil/ps。信号的上升时间一般可以通过IBIS模型或是数据手册获取(通常信号的上升时间取电平幅度值从10%上升到90%的时间范围,在IBIS模型中给出的上升时间取的是电平幅度变化值的20~80%)。对于上升时间和传播时延可参考如下图:

SIDesigner 验证分析

在这里我们用巨霖科技的软件工具SIDesigner设计了两个小案例,利用最常见的阻抗不匹配产生反射,并查看反射造成的影响来验证场景A的说法。

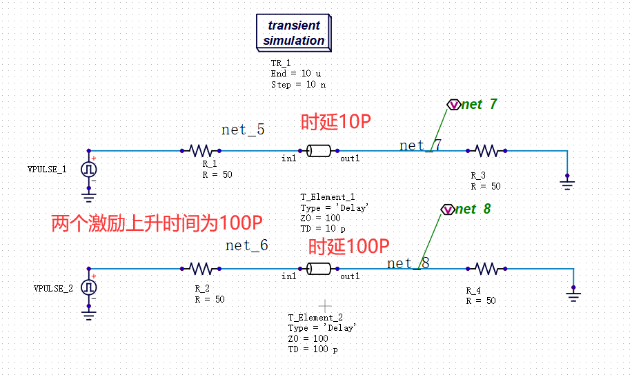

验证一:相同的上升沿下降沿时间,不同的传输时延(传输距离不同)

当信号的边沿时间都是100ps,传输时延分别设置为10P和100P,传输延时是10ps,10(传输延时)*6<100(信号边沿时间),因此此信号线不属于高速信号。传输延时是100ps,100(传输延时)*6>100(信号边沿时间),此信号线属于高速信号。

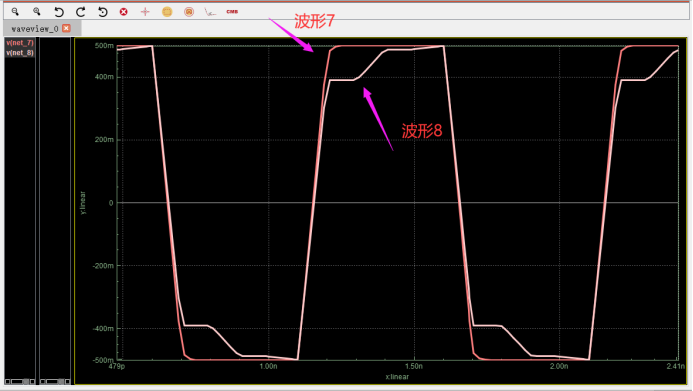

分别查看net7和net8两个观测点,观测这两路波形。可以清楚的判别出,当波形7不作为高速信号考虑的时候,波形方正,阻抗带来的影响并没有表现出来。而作为高速信号的波形8,波形波动较大,看来阻抗不匹配带来了恶劣的影响。

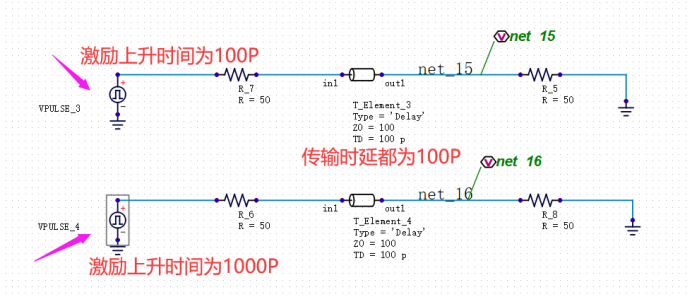

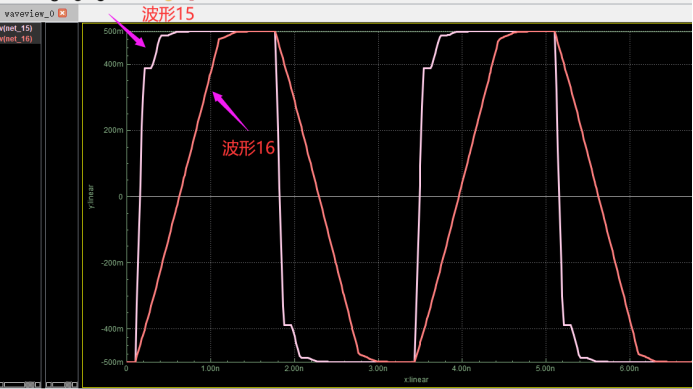

验证二:同等传输时延(传输距离),不同的信号上升沿下降沿时间

我们将两组走线的传输延时调节为100PS (约长度为600mil的传输线),不同之处在于,作为对比的net15和net16两个信号的边沿上升时间分别为100ps与1000ps。同样根据我们的计算公式,对于net15信号:1006>100,满足高速信号的定义。对于net16信号:1006<1000,不满足高速信号的定义。

看上图结果也是和理论值相吻合的,满足高速信号定义的net15,阻抗不匹配带来明显反射。不满足高速信号定义的net16,信号受到的影响很小,波形无大的失真。

结论总结:

判断是否属于高速信号,使用的是边沿时间,而不是更为大家接受的频率。这是因为高频不一定等于高速,同样,低频信号也不能完全忽略它不会产生信号完整性的问题。比如一个30MHZ的信号,如果其上升沿非常陡峭,达到了我们关于高速信号的定义,一样需要注意其信号完整性的问题。

当一个信号不满足高速信号的定义时,很多引起信号质量问题的因素都可以忽略。这也是为什么在早期的电路中没有信号完整性这个概念,早期的器件由于生产工艺等多种原因,决定了信号的边沿上升时间缓慢,达不到需要考虑传输线效应的地步。

之所以一再强调边沿时间,是由于信号中的低频分量主要影响信号的幅度,而高频分量影响边沿。一个信号的边沿越陡峭,其含有的高频分量也就越多。

-

数字电路

+关注

关注

193文章

1605浏览量

80592 -

高速信号

+关注

关注

1文章

226浏览量

17696 -

仿真验证

+关注

关注

0文章

25浏览量

8135

原文标题:高速信号简介及仿真验证分析

文章出处:【微信号:巨霖,微信公众号:巨霖】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

【转帖】PCB仿真分析解决方案

【转载】Allegro SI 高速信号完整性仿真连载之二(附详细流程)

为什么说现在具备高速信号仿真知识非常重要?

为什么说现在具备高速信号仿真知识非常重要?

仿真小技巧~高速信号如何选择走线层?

【论文】基于信号完整性分析的高速PCB仿真与设计_曾爱凤

PCB中过孔对高速信号传输的影响

高速信号的定义和仿真验证分析

高速信号的定义和仿真验证分析

评论