数字电路是现代电子威廉希尔官方网站 的基础,而晶体管是数字电路中的核心元件。晶体管的工作状态直接影响到数字电路的性能和可靠性。

- 晶体管的工作原理

晶体管是一种半导体器件,主要由两个PN结组成,分为NPN型和PNP型两种。晶体管的工作原理基于PN结的单向导电特性。

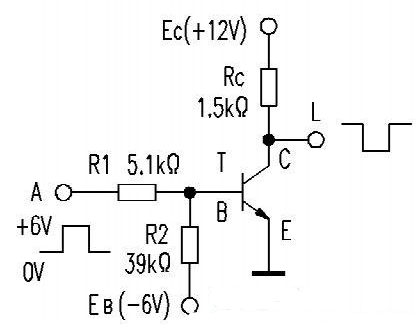

对于NPN型晶体管,当基极(B)与发射极(E)之间加上正向电压时,发射区的自由电子会向基区扩散,同时基区的空穴也会向发射区扩散。由于基区的掺杂浓度较低,扩散到基区的电子数量远大于空穴数量。这些多余的电子会在基区形成电子积累层,使得基极与集电极(C)之间的电阻降低,从而实现集电极电流的控制。

对于PNP型晶体管,工作原理与NPN型相反。当基极与发射极之间加上负向电压时,发射区的空穴会向基区扩散,基区的自由电子会向发射区扩散。同样,由于基区的掺杂浓度较低,扩散到基区的空穴数量远大于自由电子数量。这些多余的空穴会在基区形成空穴积累层,使得基极与集电极之间的电阻降低,从而实现集电极电流的控制。

- 晶体管的工作模式

晶体管的工作模式主要包括截止区、放大区、饱和区和反向偏置区。

2.1 截止区

当晶体管的基极-发射极电压(VBE)小于0.7V(对于硅晶体管)时,晶体管处于截止状态。此时,基极与发射极之间的PN结处于反向偏置状态,基极电流(IB)接近于零,集电极电流(IC)也接近于零。

2.2 放大区

当VBE大于0.7V时,晶体管进入放大区。在放大区,基极电流的变化会引起集电极电流的相应变化,实现电流放大功能。此时,晶体管的集电极-发射极电压(VCE)小于集电极电源电压(VC)。

2.3 饱和区

当VBE和VCE都较大时,晶体管进入饱和区。在饱和区,基极电流的增加不再引起集电极电流的显著增加,晶体管的输出特性趋于饱和。此时,VCE接近于零。

2.4 反向偏置区

当晶体管的集电极-基极电压(VBC)小于0时,晶体管处于反向偏置状态。此时,集电极与基极之间的PN结处于反向偏置状态,可能会导致晶体管损坏。

- 晶体管的工作条件

晶体管的工作条件主要包括温度、电源电压、电流等。

3.1 温度

温度对晶体管的性能有显著影响。随着温度的升高,晶体管的参数(如β值、VBE等)会发生变化,可能导致晶体管性能下降或损坏。因此,在设计数字电路时,需要考虑晶体管的工作温度范围。

3.2 电源电压

电源电压是晶体管正常工作的基础。电源电压的稳定性和纹波对晶体管的性能有重要影响。过高或过低的电源电压都可能导致晶体管损坏或性能下降。

3.3 电流

晶体管的电流包括基极电流、集电极电流和发射极电流。晶体管的电流参数(如ICBO、ICEO等)对数字电路的性能有直接影响。在设计数字电路时,需要合理选择晶体管的电流参数,以满足电路性能要求。

- 晶体管对数字电路性能的影响

晶体管作为数字电路的核心元件,其性能直接影响到数字电路的性能。以下是晶体管对数字电路性能的几个主要影响因素:

4.1 速度

晶体管的开关速度决定了数字电路的响应速度。晶体管的开关速度与晶体管的参数(如β值、存储时间等)有关。在设计高速数字电路时,需要选择具有高速性能的晶体管。

4.2 功耗

晶体管的功耗包括静态功耗和动态功耗。静态功耗主要与晶体管的饱和电压和集电极电流有关,动态功耗与晶体管的开关速度和电流变化有关。在设计低功耗数字电路时,需要选择具有低功耗特性的晶体管。

4.3 噪声

晶体管的噪声主要来源于基极电流的波动和集电极电流的波动。晶体管的噪声对数字电路的性能有负面影响,可能导致电路的误动作或性能下降。在设计数字电路时,需要考虑晶体管的噪声性能。

-

元件

+关注

关注

4文章

914浏览量

36691 -

晶体管

+关注

关注

77文章

9684浏览量

138106 -

电子威廉希尔官方网站

+关注

关注

18文章

890浏览量

55979 -

数字电路

+关注

关注

193文章

1605浏览量

80594

发布评论请先 登录

相关推荐

数字电路中的晶体管工作在什么状态

数字电路中的晶体管工作在什么状态

评论