最近有个项目是超低噪声采集系统,方案已经基本确定,在验证大板上方案进展顺利,输入噪声可以达到100nVpp。

然而将系统集成微型化后,出现了问题,输入噪声竟然升高了4倍,达到了400nVpp。

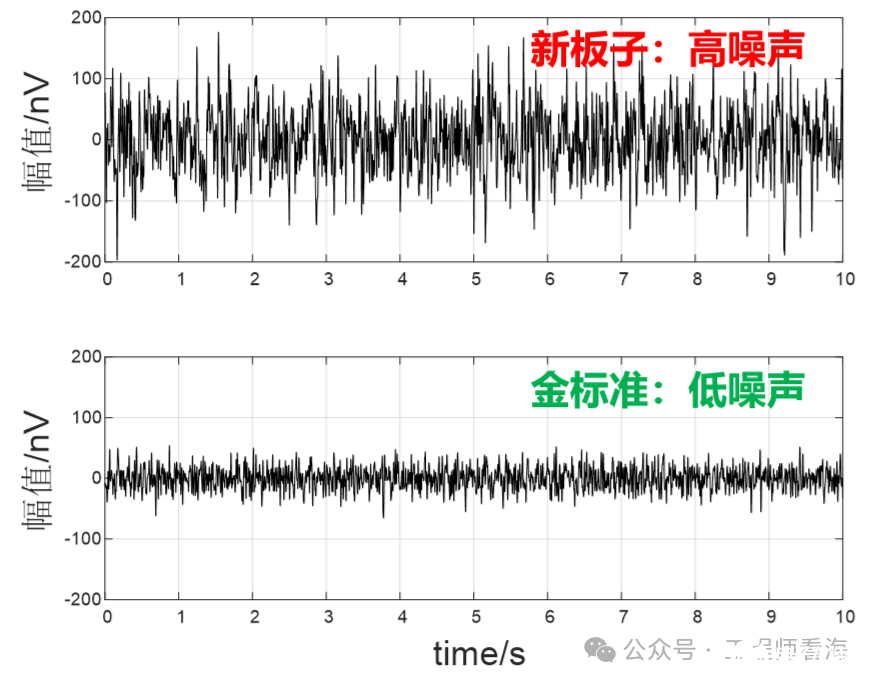

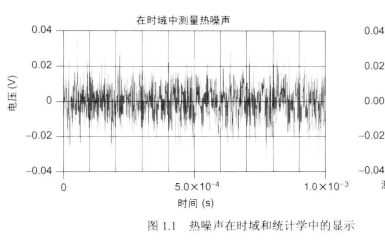

下图是噪声测试结果,第一行是集成后的板子,噪声竟然达到了400nVpp,而第二行是旧板子,噪声只有100nVpp。

这是怎么回事呢?

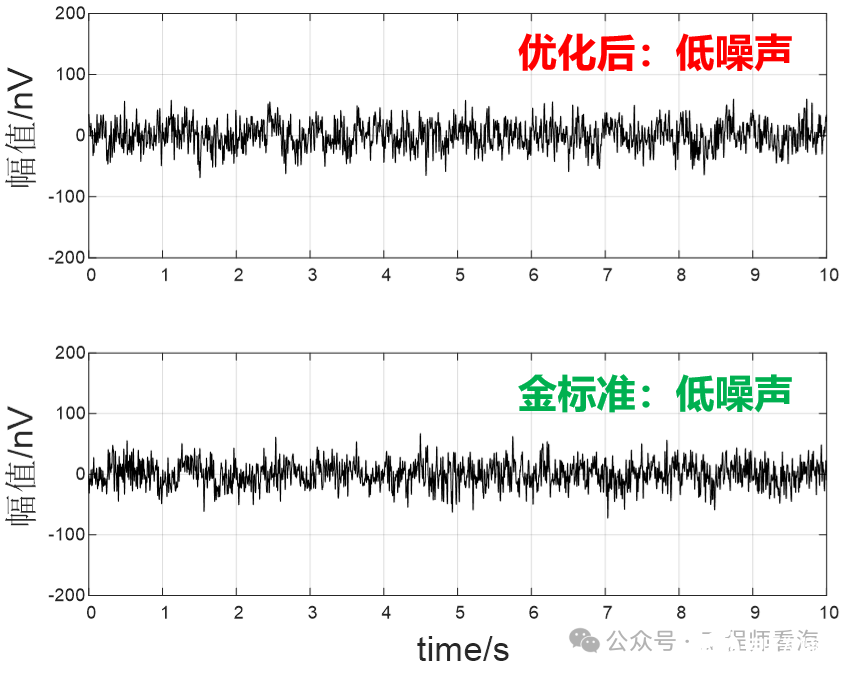

后来锁定问题是电路的输入RFI滤波器件选型错误,集成的板子物料混料,更改物料后噪声正常。

下图是优化后的噪声情况,优化后的输入噪声大约100nVpp,与旧的标准板子结果接近。

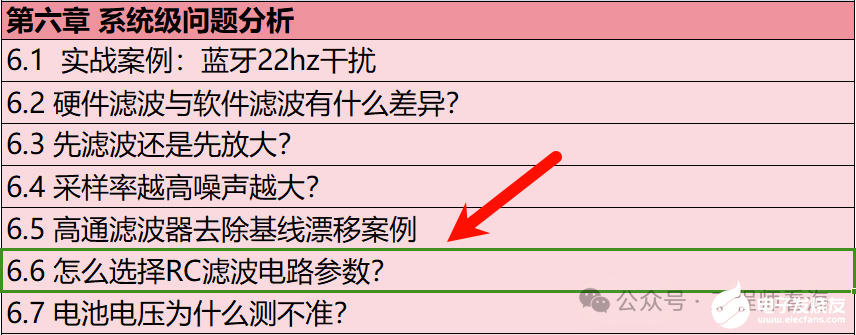

怎么优化参数的呢?

答案在《运放秘籍》第三部6.6小节:怎么选择RC滤波电路参数。

【淘宝】https://m.tb.cn/h.gZPqnDWmjspIhVx?tk=wUbtWr5UFUu HU0025 「运放秘籍第三部_信号电路与系统新说_工程师看海_运放教程」

点击链接直接打开 或者 淘宝搜索直接打开

如果看到这里,请点赞、收藏、分享三连!

限时免费扫码进群,交流更多行业威廉希尔官方网站

审核编辑 黄宇

-

电路

+关注

关注

172文章

5914浏览量

172250 -

噪声

+关注

关注

13文章

1122浏览量

47413 -

滤波

+关注

关注

10文章

667浏览量

56646

发布评论请先 登录

相关推荐

噪声小于100nVpp的模拟前端设计包括BOM及原理图

热卖 纳伏表 Keysight 34420A

Keithley 2182A 纳伏表长期收|售

安捷伦Agilent34420A纳伏表/是德KEITHLEY2182A长期收购

美国安捷伦Agilent34420A 7位半万用表纳伏微欧表

低功耗低噪声CMOS放大器设计与优化

开源硬件-TIDA-00765-15kg 范围内实现 1g 分辨率且噪声低于 100nVpp 的前端 PCB layout 设计

运算放大器噪声优化手册PDF电子书免费下载

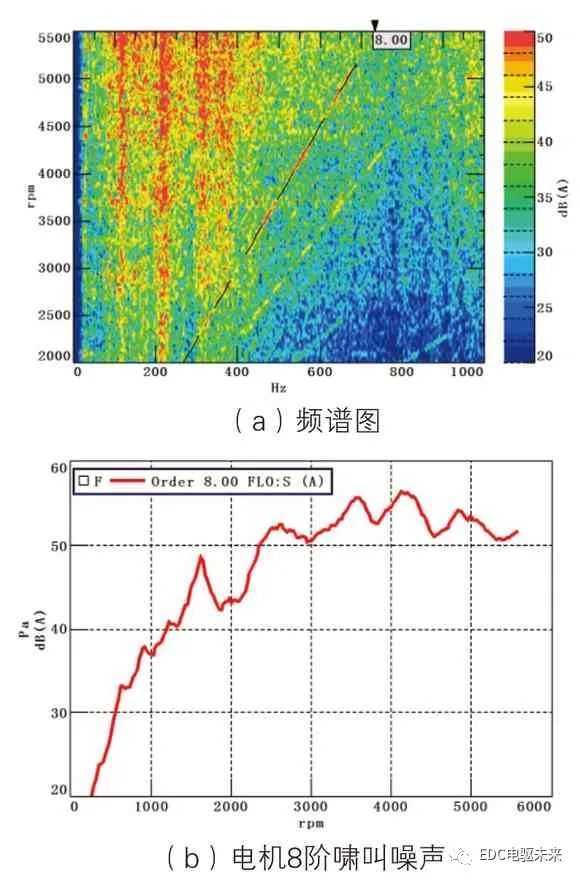

纯电动汽车电机啸叫噪声优化

100nVpp百纳伏噪声优化

100nVpp百纳伏噪声优化

评论