一、D触发器的基本概念

D触发器(Data Flip-Flop或Delay Flip-Flop)是数字电子电路中一种重要的存储器件,主要用于存储1位二进制数据。它具有记忆功能,能够在特定的时钟脉冲作用下,将输入端的信号状态锁存到输出端,并保持该状态直到下一个时钟脉冲的到来。D触发器是数字逻辑电路中构成多种时序电路的基本逻辑单元,因此在数字系统和计算机中有着广泛的应用。

二、D触发器的工作原理

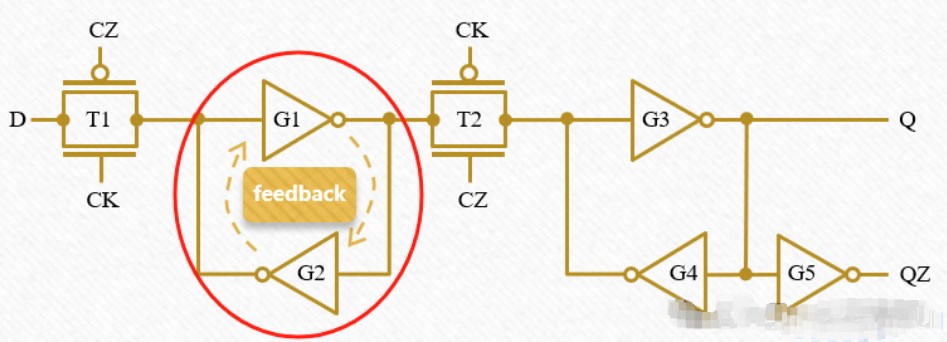

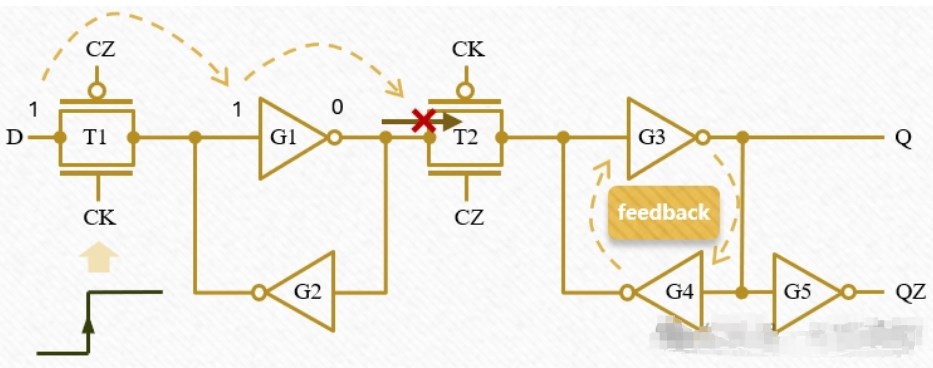

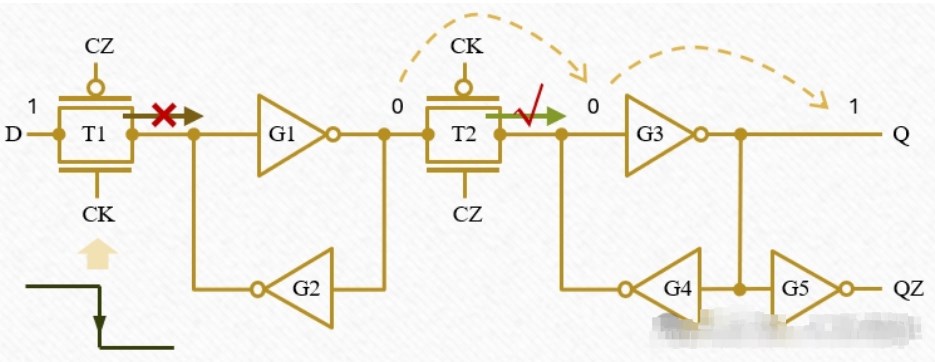

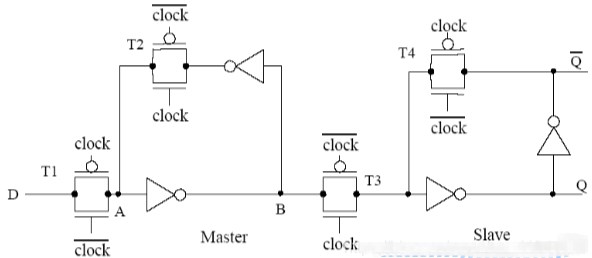

时钟信号CK通过倒相器生成反相信号CZ。D端是D触发器的信号输入。Q和QZ是D触发器的输出端。QZ通过G5输出Q的反相信号。为了便于文字表达,通常用CZ和QZ表示!CK和!Q(用“!”表示取反NOT,和上划线表示一样,读“bá”)。

G1和G2形成回路。G1的输出通过G2连接到G1的输入,称为反馈(feed back)。同理,G3和G4也形成反馈回路。

当CK为高电平时,T1导通,输入端D的信号通过G1和G2的反馈回路,使得G1的输出始终保持为D的反相电平。此时,T2截止,呈现高阻状态,G3不能接受G1的输出,而是通过G3和G4的反馈回路,保持其原有的信号。

当CK为低电平时,T1截止,呈现高阻状态,G1不能接受D的输入信号,而是保持T1导通时输入的信号。而T2导通,G3接受G1的输出信号,将改变其输出Q的信号。

等到下一个时钟信号CK再为高电平时下一个D信号才能进入这个D触发器。

CK为高电平期间,称为保持状态。CK为低电平期间,称为传输状态。

这种由时钟控制的电路,称为时序电路。这是由于D触发器与时钟信号控制来决定其信号的状态,而且能够保持一定的电平,所以称为具有记忆功能的电路。

其中,由T1、G1、G2构成的电路,以及由T2、G3、G4构成的电路都称为锁存器(latch)。

这种D触发器的类型称为主从触发器(master-slave)。前一个锁存器为主触发器,后一个锁存器为从触发器。

三、D触发器的电路结构

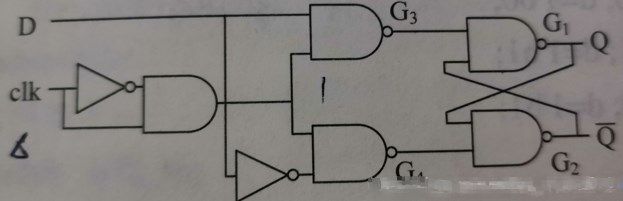

触发器主要有两种电路结构,CMOS逻辑门如图,和传输门构成的D触发器如图所示。

图为CMOS逻辑门构成D触发器

图为传输门构成D触发器

两种电路结构实现的D触发器功能一模一样,我们以图2-1为例来分析触发工作原理。如图2-1所示:在clk上升沿到来之前,D输入端无论输入任何值触发器状态不会改变,次态等于现态。当时钟上升沿到来时,与时钟信号连接的非门产生的短暂延迟,使得触发器状态置成D输入端的状态。

四、D触发器的脉冲特性

D触发器的脉冲特性主要体现在其触发方式上,主要分为电平触发和边沿触发两种。

1. 电平触发

电平触发D触发器在时钟脉冲(CP)等于某一特定电平(如高电平)时即可触发。这种触发方式相对简单,但在实际应用中容易受到干扰,因为只要CP保持在该电平,输入端D的状态变化就可能影响触发器的输出。因此,电平触发D触发器的抗干扰能力较弱。

2. 边沿触发

边沿触发D触发器在时钟脉冲的上升沿或下降沿触发。这种触发方式具有更强的抗干扰能力,因为输入信号D的状态变化只有在时钟脉冲的边沿到来时才会被触发器捕获并锁存。边沿D触发器也被称为维持-阻塞边沿D触发器,因为它在CP=1期间具有维持阻塞作用,即D端的数据状态变化不会影响触发器的输出状态。

边沿触发D触发器的脉冲特性可以进一步细化为以下几个方面:

建立时间(t_set):指输入信号D在时钟脉冲边沿到来之前必须保持稳定的最小时间。这是为了确保D端的数据在触发器翻转前已经稳定地传输到内部逻辑电路中。

保持时间(t_hold):指时钟脉冲边沿到来之后,输入信号D必须继续保持稳定的最小时间。这是为了防止在触发器翻转过程中,D端的数据发生变化而导致输出状态错误。

传输延迟(t_pd):指从时钟脉冲边沿到来到触发器输出状态稳定所需的时间。这是触发器内部逻辑电路处理输入信号并产生输出响应的时间延迟。

五、D触发器的应用

D触发器在数字系统和计算机中有着广泛的应用,主要包括以下几个方面:

1. 时序控制

D触发器可以用于时序电路中,通过控制时钟脉冲的序列来控制电路的状态变化。例如,在计数器电路中,D触发器可以存储和传递计数信息,实现计数的功能。

2. 寄存器

D触发器可以作为寄存器的基本单元,用于存储和传输数据。在数字系统中,寄存器是存储数据的重要部件,D触发器通过其记忆功能,能够稳定地保存数据并在需要时将其输出。

3. 波形发生器

通过特定的连接方式和时钟脉冲序列,D触发器可以生成各种波形信号。例如,利用D触发器的翻转功能,可以产生方波、锯齿波等周期性波形信号。

4. 同步电路

在同步电路中,D触发器用于同步不同部分的时钟信号,确保整个电路按照统一的时钟节拍工作。这有助于减少电路中的时序错误和信号冲突。

D触发器作为数字电子电路中的重要存储器件,具有记忆功能和多种触发方式。其结构主要由存储单元和控制单元组成,通过控制时钟脉冲的序列和D端的输入信号来实现对输出状态的控制。D触发器的功能包括置0、置1、保持和翻转等,这些功能使得D触发器在时序控制、计数器、寄存器和波形发生器等领域有着广泛的应用。随着数字威廉希尔官方网站 的不断发展,D触发器的性能和功能也将不断提升和完善。

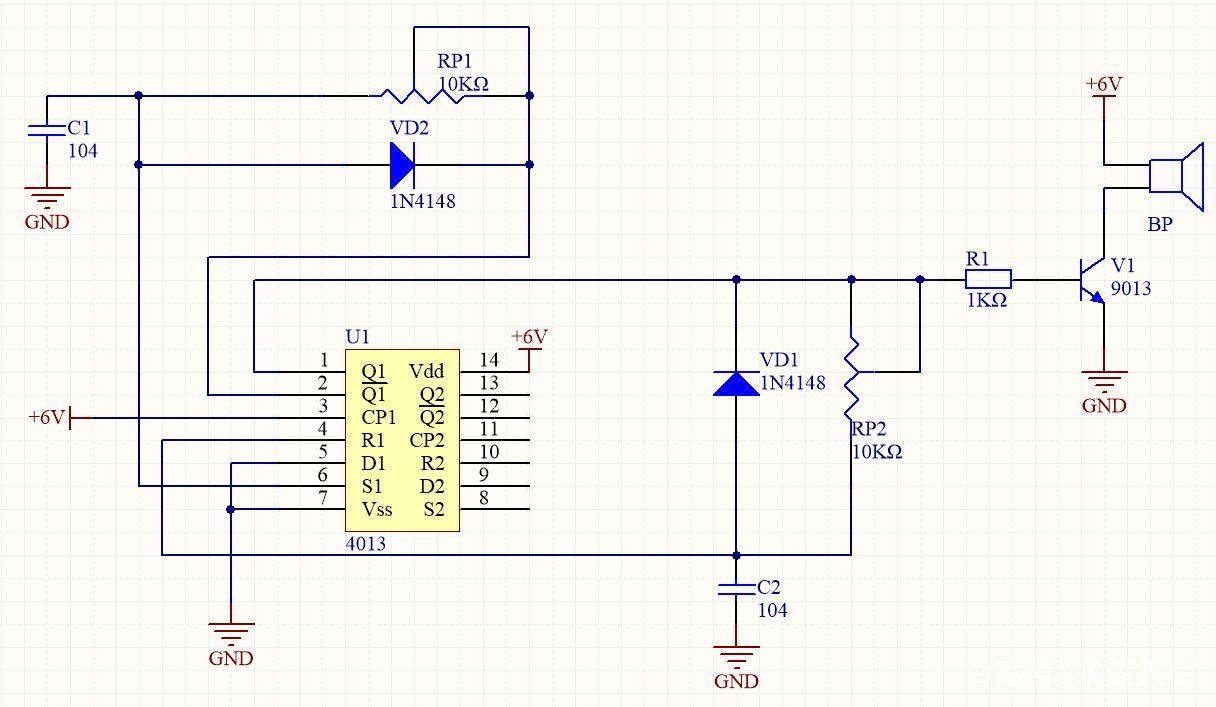

六、基于D触发器的音频信号发生器电路图

这是一个用D触发器组成音频信号发生器,电路原理图如图所示。

在电源接通后的瞬间,Q1端(第1脚)输出为高电平,该高电平通过RP2向C2充电,当C2端电压上升到复位电平时,Q1 端变为低电平,C2通过二极管VD2向Q1端放电。此时!Q1(Q1的取反)输出端(第2脚)变为高电平,该高电平通过RP1向C1充电。当C1端电压上升到置位电平时,触发器翻转,Q1变为高电平,!Q1变为低电平,Q1端的高电平向C2充电,C1通过二极管VD1向变为低电平的!Q1端放电,如此不断循环,在Q1和!Q1端交替出现高、低电平,形成振荡。因此该电路是一个无稳态的振荡器。QI 端的振荡信号通过电阻R1加到三极管V1的基极,经过V1放大后推动扬声器BP发出响亮的音频声。

-

逻辑电路

+关注

关注

13文章

494浏览量

42631 -

计算机

+关注

关注

19文章

7496浏览量

88004 -

D触发器

+关注

关注

3文章

164浏览量

47918 -

音频信号发生器

+关注

关注

1文章

5浏览量

3199

发布评论请先 登录

相关推荐

基于D触发器的音频信号发生器电路图 D触发器的工作原理和脉冲特性

基于D触发器的音频信号发生器电路图 D触发器的工作原理和脉冲特性

评论