反相器和非门是数字逻辑电路中的基本组件,它们在数字电路设计中扮演着重要的角色。尽管它们在功能上有一定的相似性,但它们之间还是存在一些关键的区别。

- 定义

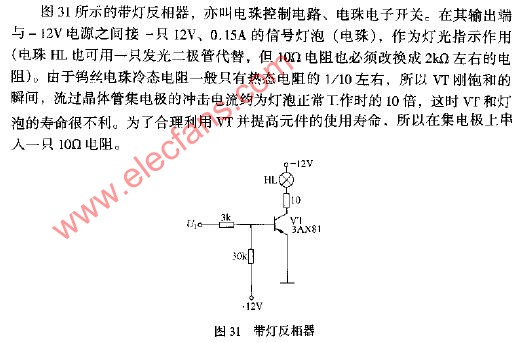

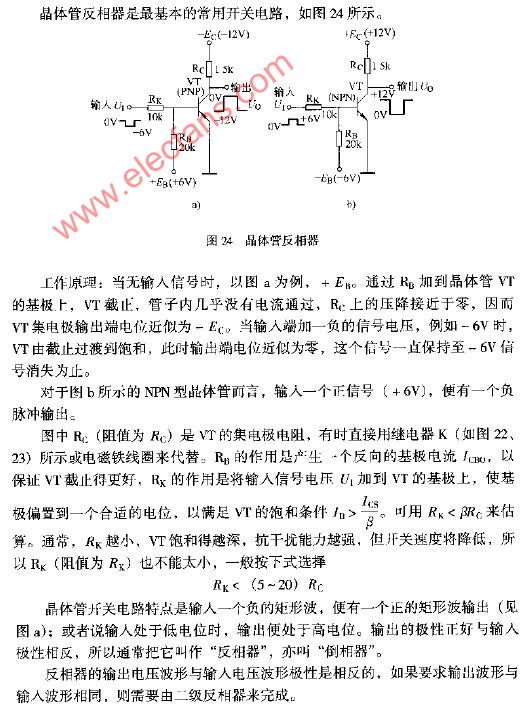

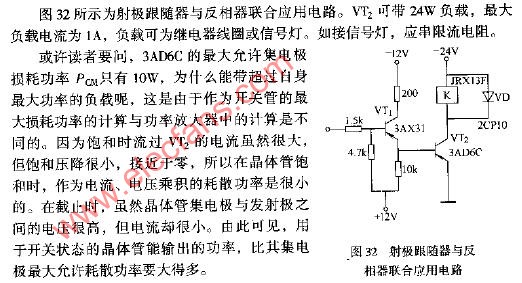

反相器(Inverter)是一种只有一个输入端和一个输出端的数字逻辑门,其输出状态与输入状态相反。当输入为高电平时,输出为低电平;当输入为低电平时,输出为高电平。反相器的逻辑功能可以用逻辑非(NOT)运算表示。

非门(NAND gate)是一种具有两个输入端和一个输出端的数字逻辑门,其输出状态为两个输入端的逻辑与(AND)运算的反(NOT)。当两个输入端都为高电平时,输出为低电平;当至少有一个输入端为低电平时,输出为高电平。非门的逻辑功能可以用逻辑与非(NAND)运算表示。

反相器的工作原理相对简单。当输入端接收到高电平时,反相器内部的晶体管或逻辑门会将电流导向地线,使输出端呈现低电平状态;反之,当输入端接收到低电平时,反相器内部的晶体管或逻辑门会将电流导向电源,使输出端呈现高电平状态。

非门的工作原理稍微复杂一些。非门内部通常包含两个晶体管或逻辑门,它们通过与门(AND gate)和非门(NOT gate)的组合实现逻辑与非运算。当两个输入端都为高电平时,与门的输出为高电平,经过非门后,输出端呈现低电平状态;当至少有一个输入端为低电平时,与门的输出为低电平,经过非门后,输出端呈现高电平状态。

- 电路结构

反相器的电路结构相对简单,通常由一个晶体管或逻辑门组成。在CMOS威廉希尔官方网站 中,反相器通常由一个N型晶体管和一个P型晶体管组成,它们通过互补对称的方式实现反相功能。

非门的电路结构相对复杂,通常由两个晶体管或逻辑门组成。在CMOS威廉希尔官方网站 中,非门通常由两个N型晶体管和两个P型晶体管组成,它们通过与门和非门的组合实现逻辑与非功能。

- 逻辑功能

反相器的逻辑功能是逻辑非(NOT)运算,其真值表如下:

| 输入A | 输出Y |

|---|---|

| 0 | 1 |

| 1 | 0 |

非门的逻辑功能是逻辑与非(NAND)运算,其真值表如下:

| 输入A | 输入B | 输出Y |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

- 应用场景

反相器和非门在数字电路设计中都有广泛的应用场景。

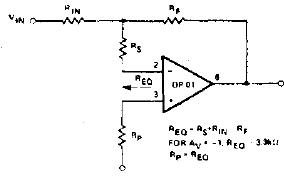

反相器主要用于实现信号的反向、信号的缓冲、信号的隔离等。在实际电路设计中,反相器可以用于消除信号的延迟、提高信号的稳定性、减少信号的干扰等。

非门则主要用于实现复杂的逻辑运算,如与非、或非、异或等。在实际电路设计中,非门可以用于实现各种复杂的逻辑功能,如数据选择、数据编码、数据解码等。

- 优缺点

反相器的优点是电路结构简单、功耗低、速度快。但是,反相器的缺点是功能单一,只能实现逻辑非运算。

非门的优点是功能强大,可以组合成各种复杂的逻辑功能。但是,非门的缺点是电路结构复杂、功耗较高、速度较慢。

反相器与非门的差异:

- 功能与逻辑表达式

- 功能:反相器和非门在功能上都实现了信号的取反,即输入和输出之间具有反相关系。但反相器主要应用于interwetten与威廉的赔率体系 电路,而非门则更多地应用于数字电路和逻辑运算。

- 逻辑表达式:反相器和非门的逻辑表达式均为Y = ¬A(其中A为输入信号,Y为输出信号,¬表示逻辑非操作)。这表明两者在逻辑功能上是等效的。

- 构成方式与实现

- 符号表示

- 反相器在电路图中通常用一个圆圈或带小圆圈的三角形表示,强调其相位反转的功能。

- 非门在电路图中则通常用一个三角形表示,强调其逻辑非的功能。这种符号表示的差异有助于在电路图中快速识别两者的功能。

- 应用领域

反相器是所有数字设计的核心。静态CMOS反相器具有以下重要特性:

①输出高电平为V DD ,输出低电平为GND;

②属于无比逻辑,功能不受晶体管相对尺寸影响;

③具有低输出阻抗,输入电阻极高;

④理论上具有无穷大扇出,单个反相器可以驱动无穷多个门,增加扇出会增加传播延时,动态特性会变差,但不会影响稳态特性;

⑤在稳态工作情况下,电源线和地线之间没有直接通路,没有电流存在,意味着理论上没有静态功耗。

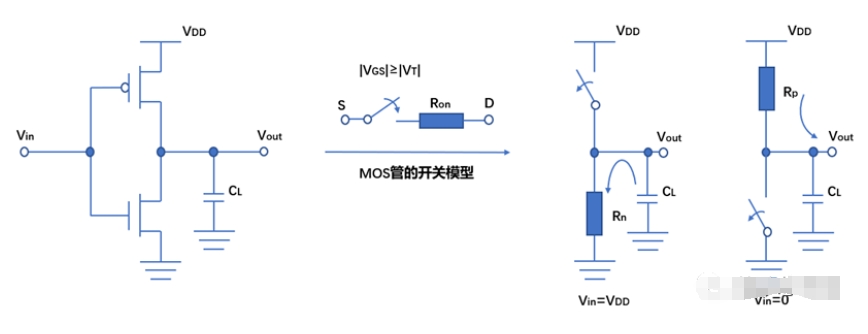

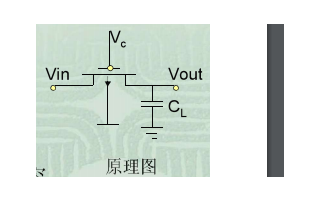

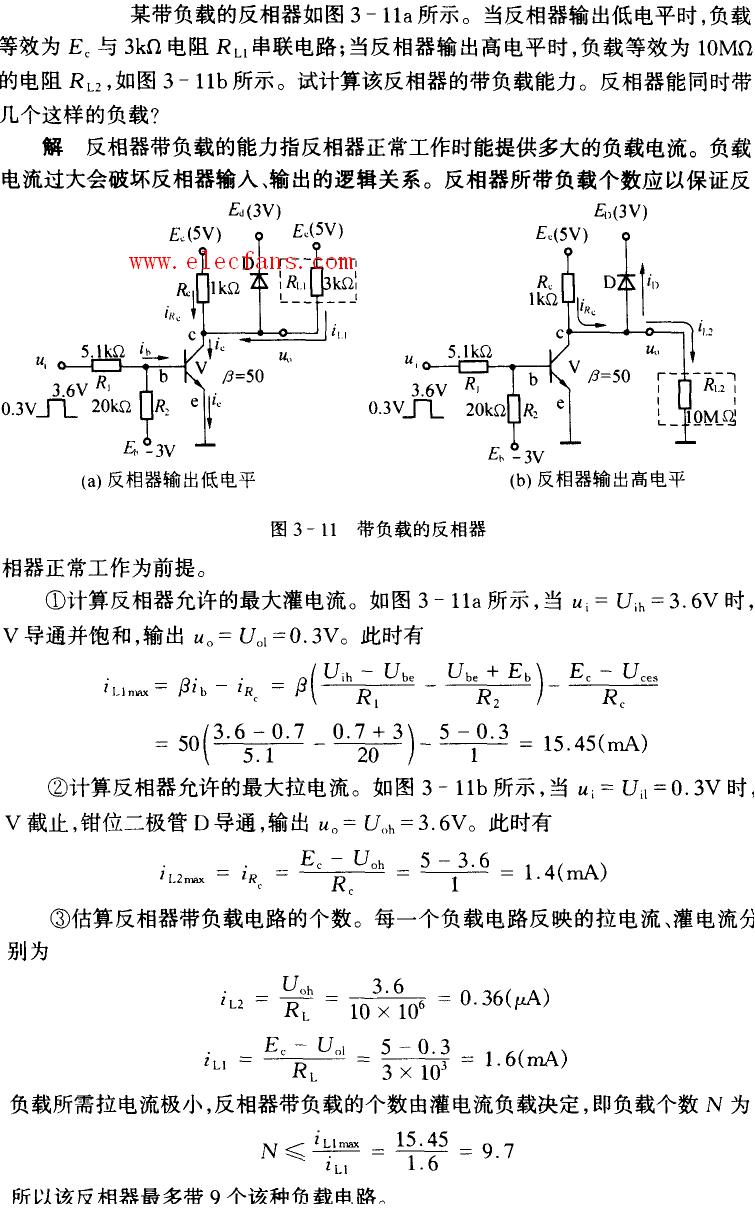

如下图是一个静态CMOS反相器的电路图,由一个上拉的PMOS器件和一个下拉的NMOS器件组成。通过使用MOS管的开关模型,可以将其等效成右边所示的反相器开关模型。当V in =VDD时,下拉NMOS器件开始工作,PMOS器件断开,将存储在负载电容CL上的电压放电至0V。当V in =0V时,上拉PMOS器件开始工作,NMOS器件断开,向负载电容CL充电至V DD 。

我们为什么要使用NMOS器件作为下拉器件,PMOS器件作为上拉器件呢?主要原因是PMOS器件是强1器件,而NMOS器件是强0器件。如下图所示,使用NMOS器件放电时可以将存储在负载电容CL上的电压放电至0V,而使用PMOS器件只能放电至|V Tp |。同样,使用PMOS器件充电时,可以向负载电容CL充电至V DD ,而使用NMOS器件只能充电至V DD -V Tn 。

CMOS反相器的总功耗分为动态功耗和静态功耗,我们首先看一下动态功耗。动态功耗主要有两种,由充放电电容引起的动态功耗和由直接通路电流引起的动态功耗。充放电电容引起的动态功耗大致过程是在充电过程中,一半能量被PMOS管消耗,一半能量存储在CL负载电容中;放电过程中,存储在电容上的能量被NMOS管消耗。

f 0→1 :称为开关活动性,是消耗能量的翻转频率,也就是每秒通断次数

另一种动态功耗是由于输入波形存在上升和下降时间,导致在开关过程中从VDD到GND之间在短期内出现一条直流通路,造成短路电流。

接下来,我们分析一下峰值电流

• 当负载很大,输出的下降时间明显比输入上升时间大,输入在输出改变之前就已经通过了过渡区,PMOS的源漏电压近似为0,P管就基本关断了,所以Ipeak很小

• 反之,当负载很小,输出下降时间明显小于输入上升时间,PMOS的VDS大部分时间等于V DD ,所以导致了最大的短路电流

我们得到的结论是:使输出的下降时间大于输入上升时间可以减小短路功耗,但输出的上升/下降时间太大会降低电路速度,并在扇出门中引起短路电流。换句话说,当负载电容比较小时,直接通路电流引起的动态功耗将占主导,而当负载电容较大时,充放电负载电容引起的动态功耗将占主导。

静态功耗一般由源(或漏)与衬底之间的反偏二极管漏电和亚阈值漏电构成:

①源(或漏)与衬底之间的反偏二极管漏电

通常情况下非常小,该部分漏电是由热产生的载流子引起的,该数值随结温而增加,并且呈指数关系。

②亚阈值漏电

VGS接近阈值电压时会有源漏电流,在深亚微米工艺下,电源电压降低导致这一电流越发显著。

静态功耗计算公式为:

I stat :指在没有开关活动存在时在电源两条轨线之间流动的电流。

CMOS反相器的总功耗为:

应当指出的是在典型的CMOS电路中由充放电电容引起的动态功耗占主导地位,直接通路电流引起的功耗可以通过设计控制在限定范围内,而漏电造成的静态功耗在未来的工艺制程下会占据更大比重。

反相器和非门在数字逻辑电路中都有重要的作用。它们在定义、工作原理、电路结构、逻辑功能、应用场景等方面都存在一定的区别。在实际电路设计中,需要根据具体的应用需求和性能要求,选择合适的逻辑门。

-

反相器

+关注

关注

6文章

311浏览量

43296 -

数字电路

+关注

关注

193文章

1605浏览量

80594 -

非门

+关注

关注

1文章

32浏览量

33887 -

数字逻辑电路

+关注

关注

0文章

106浏览量

15814

发布评论请先 登录

相关推荐

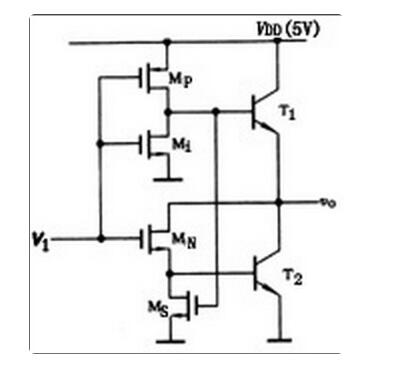

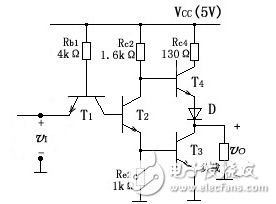

TTL反相器的基本电路图

反相器和非门有什么区别

TTL反相器的基本电路(六款TTL反相器的基本电路设计原理图详解)

cmos反相器设计电路图

MOS反相器和CMOS反相器的详细资料说明

反相器和非门的区别 反相器电路图介绍

反相器和非门的区别 反相器电路图介绍

评论