本文翻译自Synopsys的官方文章:

在数字设计的Implementation过程中,从RTL到GDSII的每一步都是高度计算密集型的。在SoC层面,为了最小化互连的延迟,我们需要评估数百个partition的各种布局方案。一旦确定了布局方案,接下来就是进行每个partition内的其余步骤,以实现全芯片的implementation和signoff。由于每一步的计算需求已经很高,并且还要乘以partition的数量,这就引发了一个问题:传统用于数字设计的CPU是否已经达到了容量极限?GPU是否能够满足计算需求?

如今,GPU以其处理人工智能、机器学习、游戏和高性能计算等要求最为苛刻的工作负载而闻名。随着芯片越来越大、越来越复杂,也许也是时候考虑用GPU来完成数字芯片设计的Implementation了。

CPU在EDA工作负载中的容量挑战

CPU长期以来被认为是计算机的“大脑”。拥有数十亿个晶体管和多个处理核心,如今的CPU非常适合完成广泛的任务,并且能够快速完成。另一方面,GPU最初是为特定目的设计的,但随着时间的推移,它们也转变为通用的并行处理器。

一般来讲,EDA工具都是在基于x86处理器的CPU上运行的。然而,随着多芯片设计等复杂架构变得越来越普遍,我们正在接近CPU计算容量的限制。考虑到芯片设计团队始终面临的上市时间压力,利用额外的工具和威廉希尔官方网站 来加速芯片设计过程的任何方面都是有意义的。在验证和分析方面,新思科技的PrimeSim和VCS仿真流程已经从GPU加速中受益。虽然数字设计流程中的每个任务并不是都非常适合GPU,但有些任务确实可以加速。

最先进的高性能数据中心x86 CPU核心平均有64到128个核心,每个box最多约有200个核心。需要更多核心的任务需要分布在许多box上;如果网络不够快,这会产生一些开销。RTL到GDSII流程和优化威廉希尔官方网站 包含许多相互依赖性。为了使流程中的每个任务能够成功并行执行,作业分布在CPU box之间的数据共享必须非常快速,延迟要小。然而,实际上,网络延迟会妨碍周转时间,使得完整的RTL到GDSII流程的分布式并行化变得不那么有吸引力。

另一方面,GPU核心可以轻松扩展。每个核心执行的操作更少,而且非常微小,以至于你可以在一个插座中拥有数万个核心,以提供巨大的处理能力,同时保持可管理的占用空间。能够从大规模并行性中受益的任务非常适合GPU。然而,这样的任务也必须是主要单向的,因为任何决策和迭代都会减慢进程和/或需要回到CPU进行“如果那么”决策。这排除了许多RTL到GDSII数字implementation流程中的任务,尽管并非所有任务都不适合。

使用GPU加速加快布局过程

在数字设计流程中,自动布局是已经展示出在GPU上运行前景的一项任务。在商业环境中运行的原型中,新思科技的Fusion Compiler GPU加速布局威廉希尔官方网站 相比CPU,已经展示出显著的周转时间优势:

使用GPU放置一个3nm GPU流处理器设计,包含1.4M个可放置的标准单元和20个可放置的硬宏,仅需38秒,相比之下,CPU驱动的布局需要13分钟

使用GPU放置一个12nm汽车CPU设计,包含2.9M个可放置的标准单元和200个可放置的硬宏,仅需82秒,相比之下,CPU驱动的布局需要19分钟

结合新思科技DSO.ai的AI驱动自动设计空间优化,我们预计将在相同的完成时间线上将AI驱动的搜索空间扩大15倍到20倍。这样做可以使设计团队实现更好的功耗、性能和面积(PPA)结果。

在许多方面,由于对最终设计PPA的高影响,布局和 floorplanning 是涉及最广泛探索的implementation步骤。我们可以想象,即使GPU计算资源通常与强大的CPU计算集群分开,单个designer使用基于GPU的布局威廉希尔官方网站 也能具有很高的生产力。然而,在RTL到GDSII 的implementation流程的其余部分中,通过CPU和GPU集群之间移动设计数据引入的延迟可能会限制吞吐量优势。

新的数据中心SoC正在设计中,CPU和GPU资源之间具有统一内存,用于TB级工作负载。这些新兴架构消除了利用GPU加速所需的设计数据移动,并将允许我们考虑在数字设计流程中应用GPU加速的其他位置,特别是当设计师可以将GPU与AI驱动的implementation工具配对时,可以进行更快、更广泛的探索和更好的结果。随着像新思科技.ai这样的AI驱动的全栈EDA流程解决方案产生更好的PPA结果、更快的达到目标时间和更高的工程生产力,人们只能想象GPU加速的加入将如何进一步改变芯片设计。

总结

虽然芯片设计过程中的仿真部分对于在GPU上运行并不陌生,但很快数字设计流程的各个方面也将有机会利用GPU加速。对于大型芯片或复杂架构(如多芯片设计),CPU在运行RTL到GDSII流程时所需的计算容量正在耗尽,无法达到期望的速度。凭借其可扩展性和处理能力,GPU有可能提供更快的周转时间和更好的芯片结果。使用GPU驱动的放置器进行的原型实验已经将布局速度提高了多达20倍。随着AI集成到EDA流程中,加入GPU可以形成一个强大的组合,以提高PPA(功耗、性能和面积)和上市时间。

审核编辑:刘清

-

芯片设计

+关注

关注

15文章

1017浏览量

54880 -

人工智能

+关注

关注

1791文章

47208浏览量

238304 -

RTL

+关注

关注

1文章

385浏览量

59766 -

机器学习

+关注

关注

66文章

8408浏览量

132580 -

GPU芯片

+关注

关注

1文章

303浏览量

5806

原文标题:GPU可以加速芯片设计的Implementaion吗?

文章出处:【微信号:傅里叶的猫,微信公众号:傅里叶的猫】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

数字压力表的准确度如何?是否适用于精密测量?

数字孪生如何改变传统行业

TLC2272输入电压为1V左右,较小放大倍数,在输入电压慢慢增大,输出就只有4.75V就达到了极限,为什么?

opa690前级放大,噪声达到了100mv,为什么?

JAVA应用CPU跳点自动DUMP工具

数字功放机和传统功放哪个好用

如何将精益思维应用于传统工厂的数字化转型?

如何判断stm8s207是否已经运行?

什么是输出极限电流?怎么测试电源模块的输出极限电流?

gpu是什么和cpu的区别

LTM4644 SS管脚接地,是否可以达到禁止该通道输出的目的?

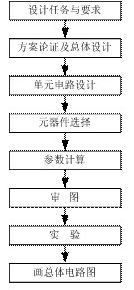

传统数字系统的设计过程包括哪些

传统用于数字设计的CPU是否已经达到了容量极限?

传统用于数字设计的CPU是否已经达到了容量极限?

评论