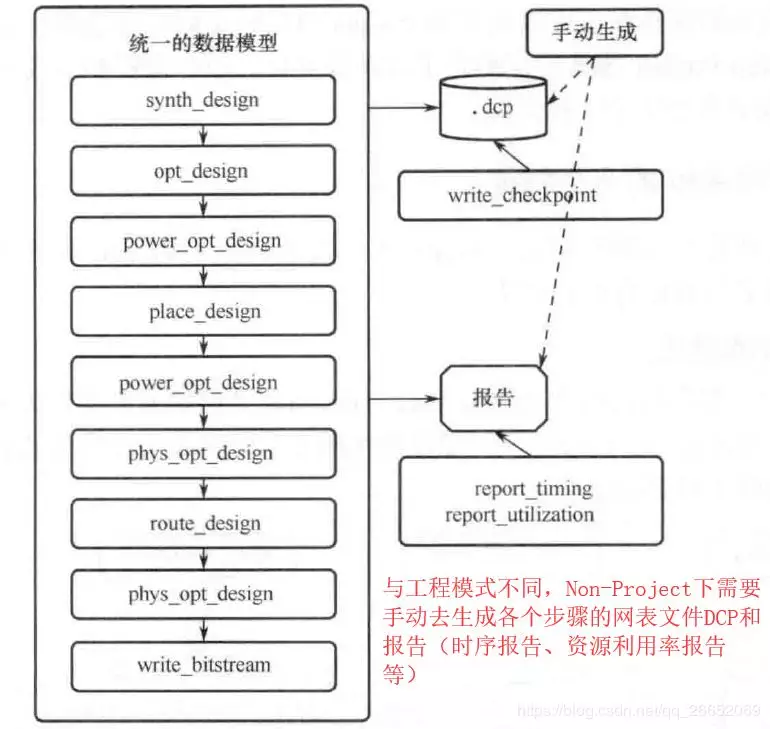

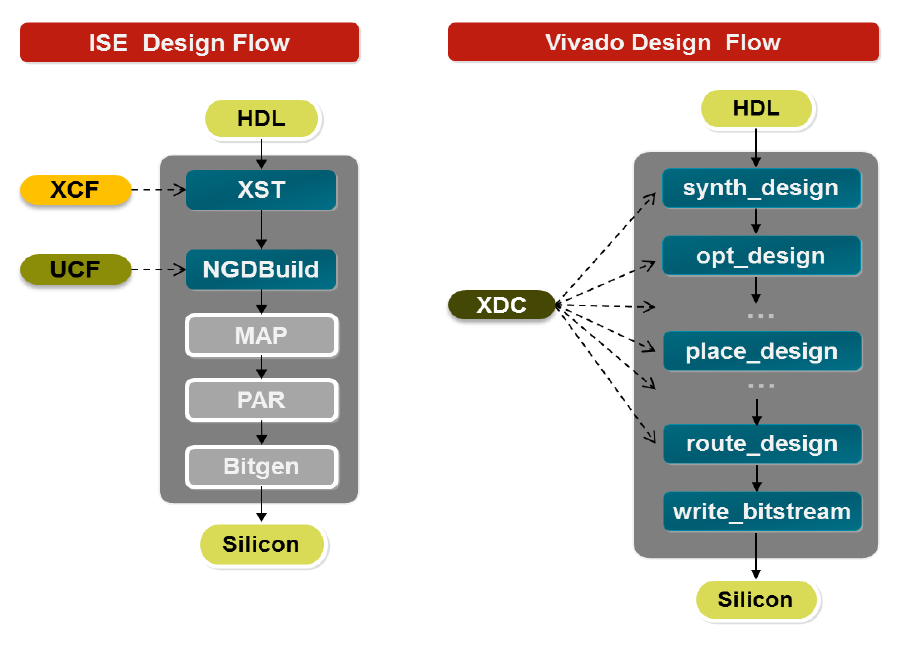

本文介绍了在 AMD VivadoDesign Tool中用工程模式使用 DFX 流程以及需要注意的地方。在使用 DFX 工程模式的过程中要把具体步骤映射到相应的 DFX 非工程模式的步骤,这样才能更好地理解整个流程的运行逻辑。

1. 创建初始普通工程

DFX 工程模式会将 DFX 的要求自动嵌入到 Vivdao 流程中,后续用户可以在 Vivado IDE 中访问该工程。

所有静态逻辑和各个 RM(Reconfigurable Module)的源文件,各个 Configuration 的输出文件都会都被自动管理,而在 DFX 非工程模式中这个文件都需要用户自行管理。

DFX 模式中创建工程的流程和普通设计没有区别,用户需要把静态部分的源文件和约束文件加入到新建的工程中。

Intitial Configuration 的 RM 所包含的源文件和约束文件可以在此时加入工程,也可以在后续步骤中加入到当前的工程中。如果此时不加入 Intitial Configuration 的 RM 的相关文件,可以暂时将此 RM 作为黑盒处理。在这里我们一般选择同时把 Intitial Configuration 的 RM 所包含的源文件和约束文件到加入工程中。

2. 将初始普通工程设置成 DFX 工程

建成初始普通工程后,建议把工程通过以下任一的方法做好备份。

1. File -> Project -> Archive

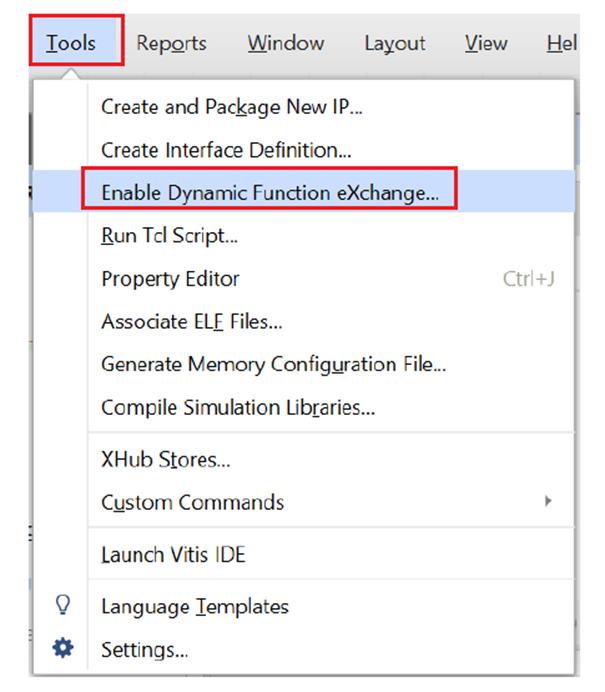

2. 在 TCL CONSOLE 执行 "write_project_tcl XX.tcl" 获得重建工程所需的 TCL 脚本。通过主菜单 Tools -> Enable Dynamic Function eXchange 将初始普通工程设置成 DFX 工程。

注意:这个操作一旦执行不可逆转, 不可撤销。

3. 创建分区定义(Create Partition Definition)

这步操作对应非工程模式中创建 RP(Reconfigurable Partitions)的步骤, 对应的模块的 HD.REGUFIGURABLE 属性被自动被设置成 True。

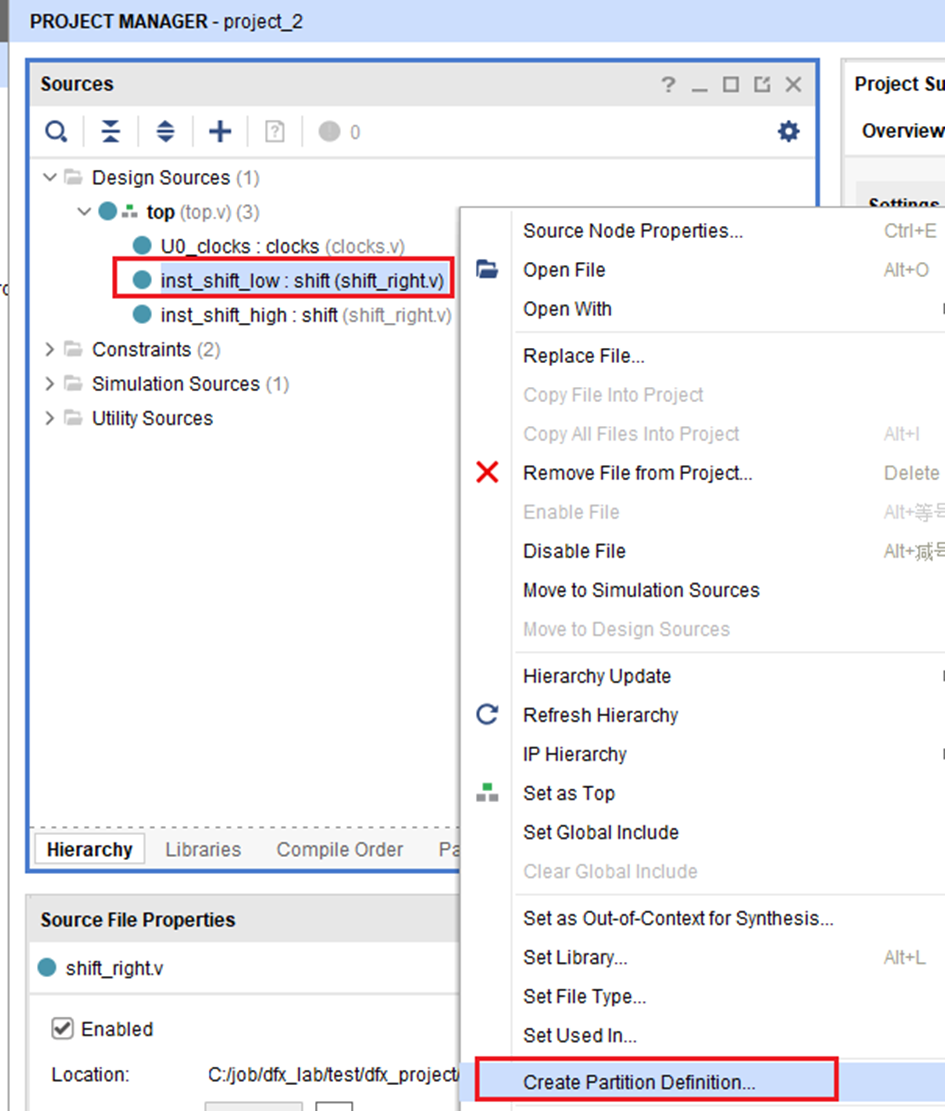

当把普通工程转成 DFX 工程之后,可以从 RTL Source/Hierarchy 窗口中选择一个文件(对应的 Instance)作为 RP。

注意:动态顶层文件不能是 IP,DCP 或者 EDIF。如果暂时没有动态部分的逻辑,这里允许选择黑盒文件。(在后续的 opt_design 步骤之前,需要用网表或者灰盒填充这个黑盒)。

在这里的例子中,同一个 Module 被例化了两次,不管是哪一个 Instance 被定义成 Partition, 这两个 Instance 都会变成 RP。如果实际只需要一个 Module 作 RP,那么需要手动修改其中一个 Module 的名字,使他们相互不同。

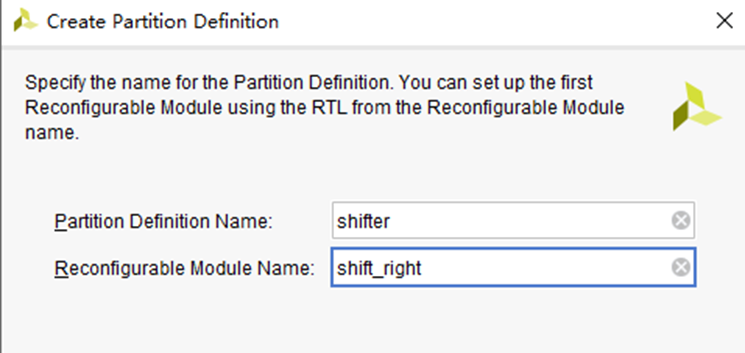

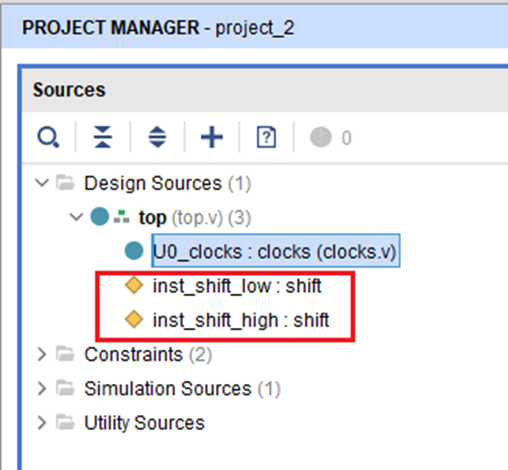

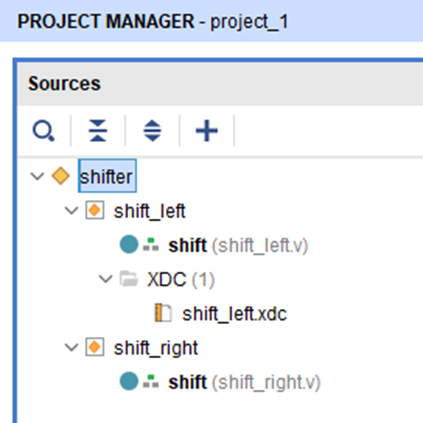

在弹窗"Create Partition Name"中分别给 Partition Definition 和 Reconfiguratble Module 命名后,Source 窗口会相应改变: 黄色菱形代表的模块即是 Partition Definition。

在非工程模式中静态部分和动态部分是分开综合再 Link 到一起。在非工程模式中,工具会自动对 RP 模块进行 OOC 综合后合并到顶层,和在非工程模式的原理一致。在这里要注意动态区逻辑和静态区逻辑的综合依然是保持相互独立。

4. 按照 DFX Wizard 的引导完成 DFX 工程的设置

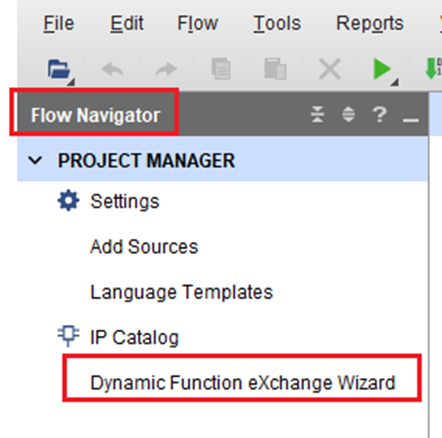

1. 在工具菜单或者 Flow Navigator 中启动 DFX Wizard。

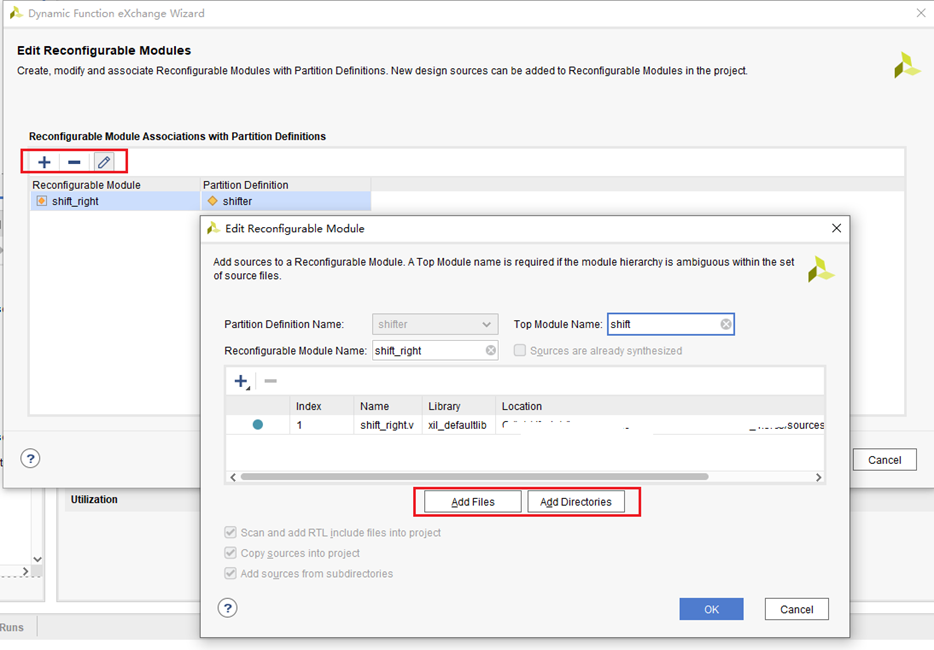

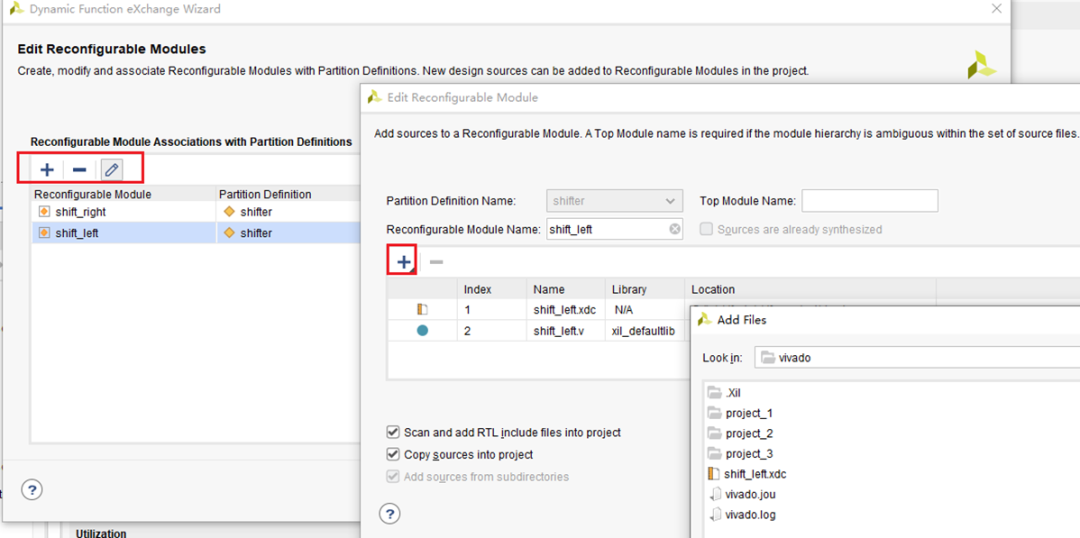

2. 点击 Next 进入 Edit Reconfigurable Modules 页面。

这里可以看到之前加的 RM shift_right 已经存在了。蓝色的+、-和铅笔按钮分别对应增加、删除和修改 RM 源文件的操作。

3. 点击+号可以创建一个新的 RM,点击“Add Files"或者"Add Directories”。

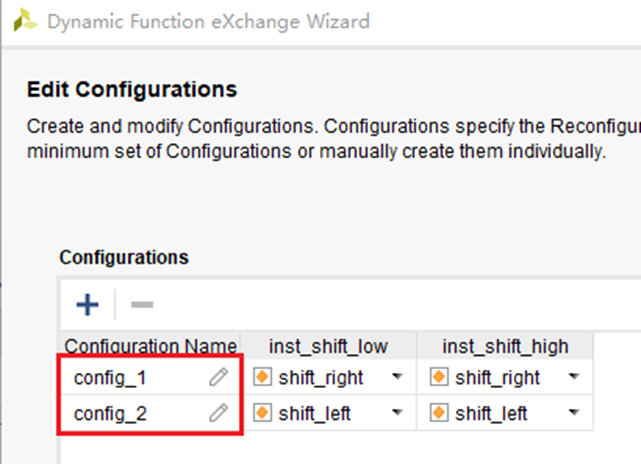

4. 点击 Next,进入"Edit Configurations"页面。

点击+号添加Configuration,也可以直接点击"automatically create configurations"让工具自动生成 Configuration。这里我们直接让工具自动产生 Configuration,然后我们可以按照我们自己的需求在这基础上进行修改。

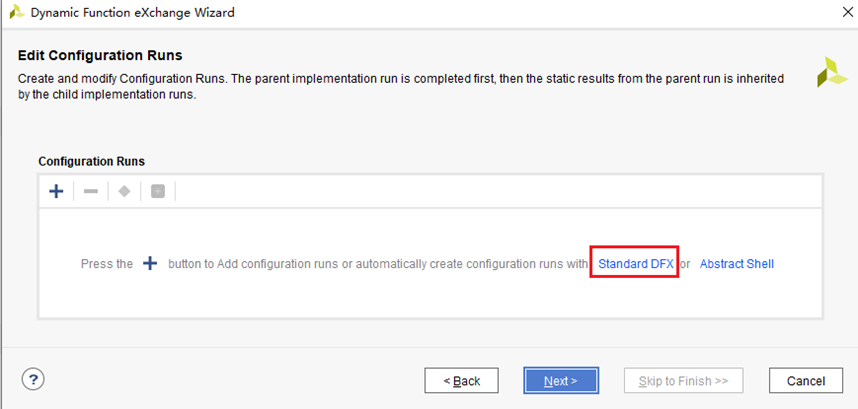

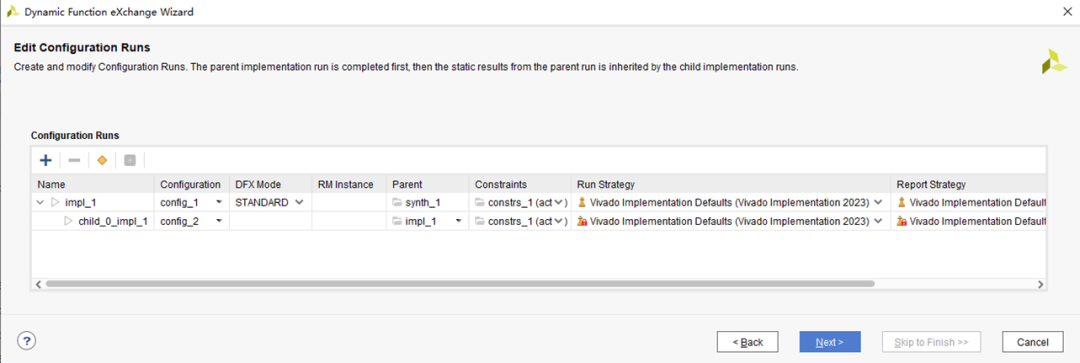

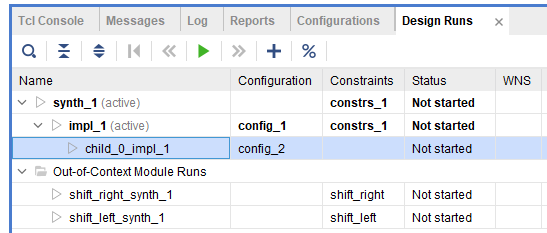

5. 点击 Next,进入"Edit Configuration Runs" 页面,把这些 Configuration 和直接的 Run 挂钩。

和上一个页面相似,点击+号可以添加 Runs,这里我们直接点击"Standard DFX", 工具会自动产生 Configuration Runs。

然后我们可以在这基础上进行修改, 按需增减 Configuration Runs;同时通过下拉菜单设置每个 Run 的 Run strategy 和 Report Strategy。

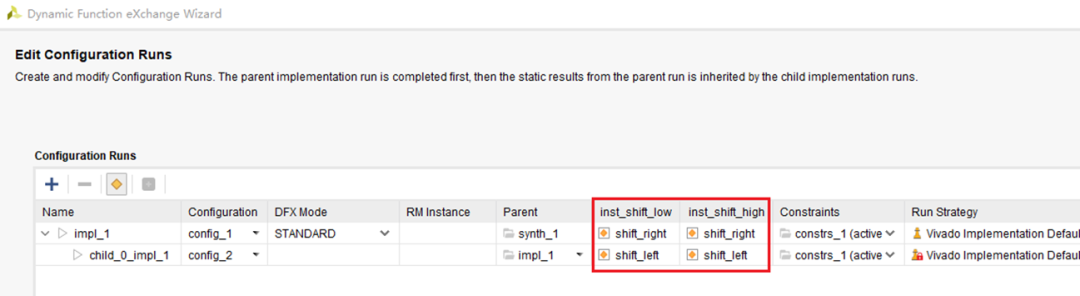

在此页面上点击黄色钻石符号,可以显示每个 Configuration Run 中的 RP 所包含 RM 的名字。

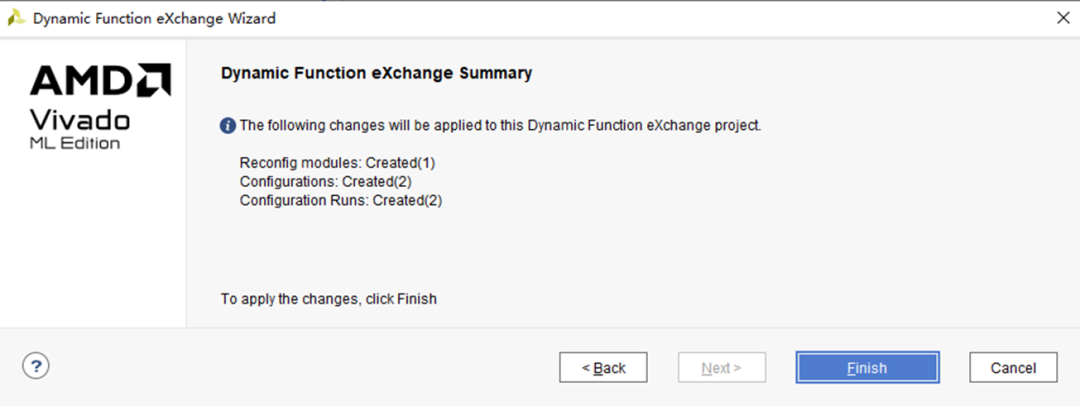

6. 点击 Next 进入 Summary 页面。

可以看到当次创建的RM,Configuration 以及 Configuration Runs 的数目。

点击“Finish”退出 DFX Wizard。

5. 查看各个 RM 所包含的源文件

在 Source 窗口,Partition Definitions 中依次展开 RP, RM 可以看到每个 RM 中包含的源文件。

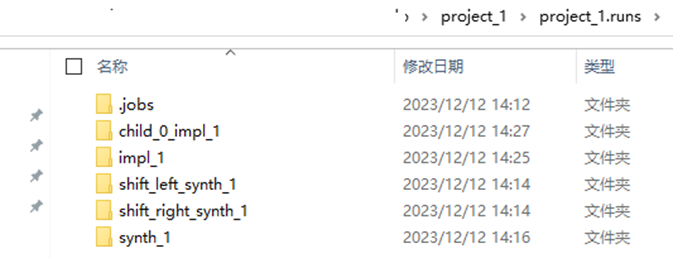

6. 在 Deisgn Runs 或者 Flow Naviagator 中启动 Runs 的运行,直至生成比特流文件

Child Impl run 会使用和其 Parent Impl run 相同的静态逻辑。

完成 Implementation 后,工具会自动执行 Pr_verify 命令验证这些 Run 之间边界逻辑的一致性。

7. 在各个 Run 的目录下,可以找到各自的 Full bit 和 Partial bit

审核编辑:刘清

-

TCL

+关注

关注

10文章

1722浏览量

88566 -

RTL

+关注

关注

1文章

385浏览量

59763 -

Vivado

+关注

关注

19文章

812浏览量

66473

原文标题:开发者分享|如何在 AMD Vivado™ Design Tool 中用工程模式使用 DFX 流程

文章出处:【微信号:gh_2d1c7e2d540e,微信公众号:XILINX开发者社区】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

用 TCL 定制 Vivado 设计实现流程

液晶电视工程模式

如何在Vivado中执行工程变更命令 (ECO)

如何在Vivado Design Suite 中进行IP加密

关于Vivado non-project模式

Vivado Design Suite 用户指南介绍

AMD Vivado Design Suite 2023.2的优势

深入探索Vivado非工程模式FPGA设计流程

AMD Vivado Design Suite 2024.1全新推出

U50的AMD Vivado Design Tool flow设置

如何在AMD Vivado™ Design Tool中用工程模式使用DFX流程?

如何在AMD Vivado™ Design Tool中用工程模式使用DFX流程?

评论