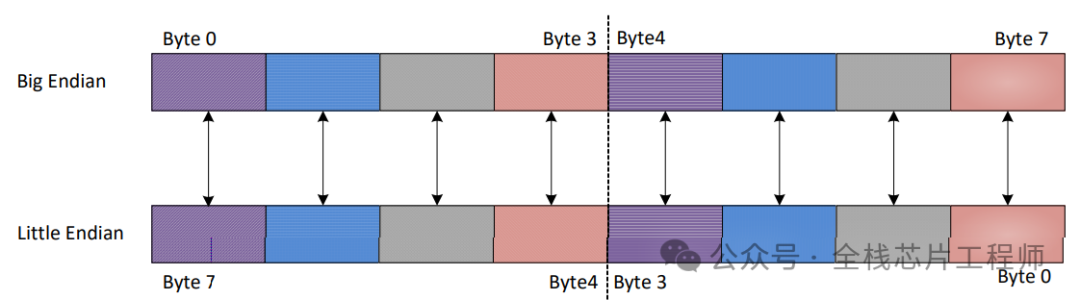

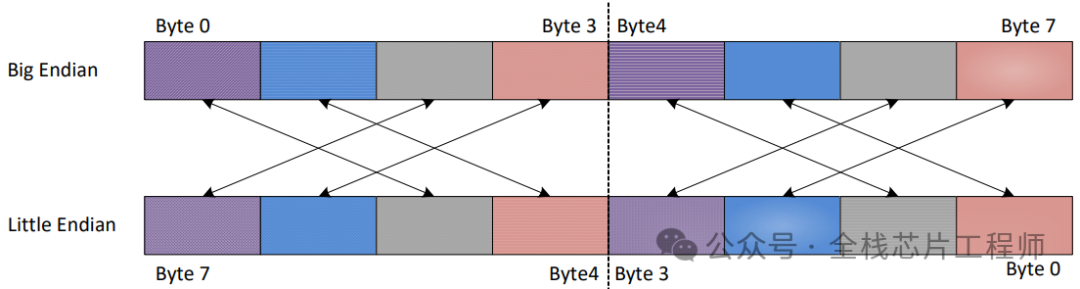

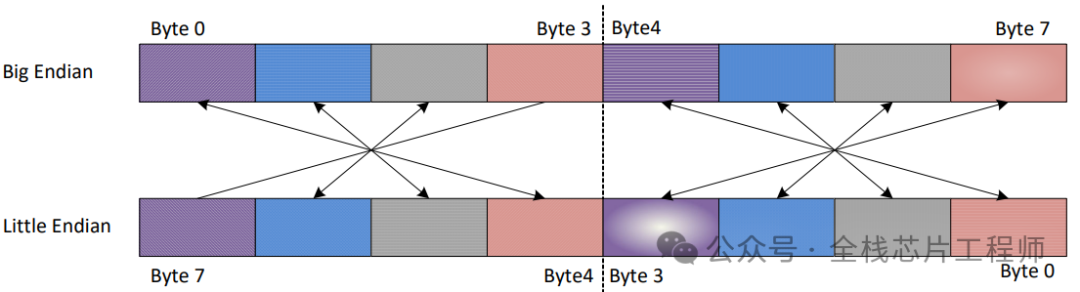

大端,最高字节存储在最低的内存地址,小端则是最低有效字节存储在最低的内存地址。在Verilog中实现大端(Big-Endian)和小端(Little-Endian)之间的转换通常涉及到对多字节数据的操作。

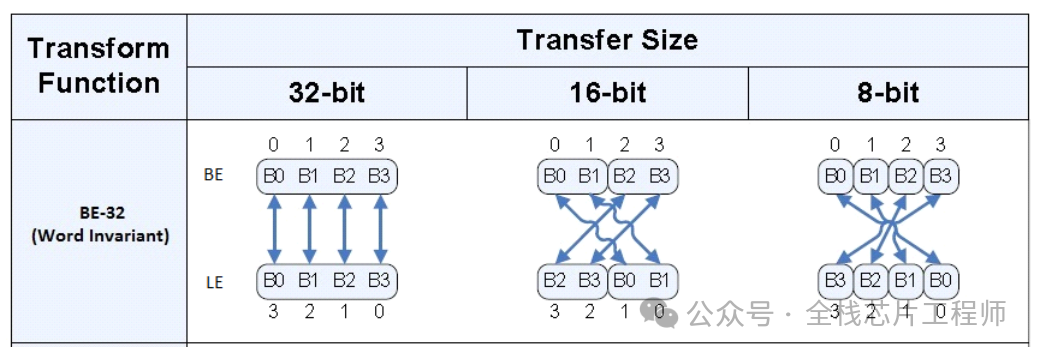

按照word传输不变的要求,一般我们可以分为三种:

第一种:word传输不变,Word access的处理。

第二种:word传输不变,half Word access的处理。

第三种:word传输不变,Byte access的处理。

以下是一个简单的Verilog代码示例,展示了如何在大端和小端之间进行转换。这个例子中,我们假设要转换的数据是一个32位的数字。

module endian_converter(

input wire clk, // 时钟信号

input wire [31:0] data_in, // 输入数据,假设为大端格式

input wire [2:0] mode, // 模式选择信号,2'b00为大转小,2'b01为小转大

output reg [31:0] data_out // 输出数据

);

// 根据模式选择信号进行字节序转换

always @(*) begin

case (mode)

2'b00: begin // 大端转小端

data_out[7:0] = data_in[31:24];

data_out[15:8] = data_in[23:16];

data_out[23:16] = data_in[15:8];

data_out[31:24] = data_in[7:0];

end

2'b01: begin // 小端转大端

data_out[7:0] = data_in[7:0];

data_out[15:8] = data_in[15:8];

data_out[23:16] = data_in[23:16];

data_out[31:24] = data_in[31:24];

end

default: data_out = 32'b0; // 无效模式,输出清零

endcase

end

endmodule

这个模块在每个时钟上升沿触发时执行转换。根据mode的值,数据会被重新排列。对于大端转小端(2'b00),最高有效字节(MSB)被移动到最低有效字节(LSB)的位置,而最低有效字节被移动到最高有效字节的位置。对于小端转大端(2'b01),数据保持不变,因为我们假设输入已经是按照预期的格式排列的。

审核编辑:黄飞

-

内存

+关注

关注

8文章

3025浏览量

74056 -

Verilog

+关注

关注

28文章

1351浏览量

110101

原文标题:字传输不变的3种大小端处理方式

文章出处:【微信号:全栈芯片工程师,微信公众号:全栈芯片工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

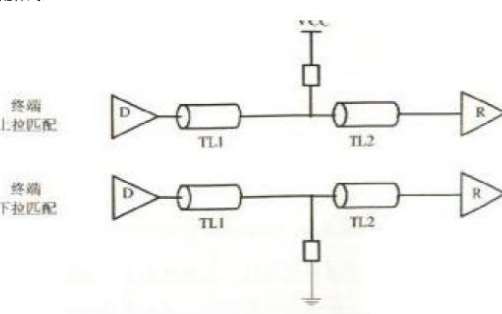

阻抗匹配的四种处理方式

无铅PCB的设计方法和表面处理方式选择等介绍

基于android采用异步处理方式开发移动护理程序的设计

介绍学习一种模拟信号的处理方式:对数处理

字传输不变的3种大小端处理方式

字传输不变的3种大小端处理方式

评论