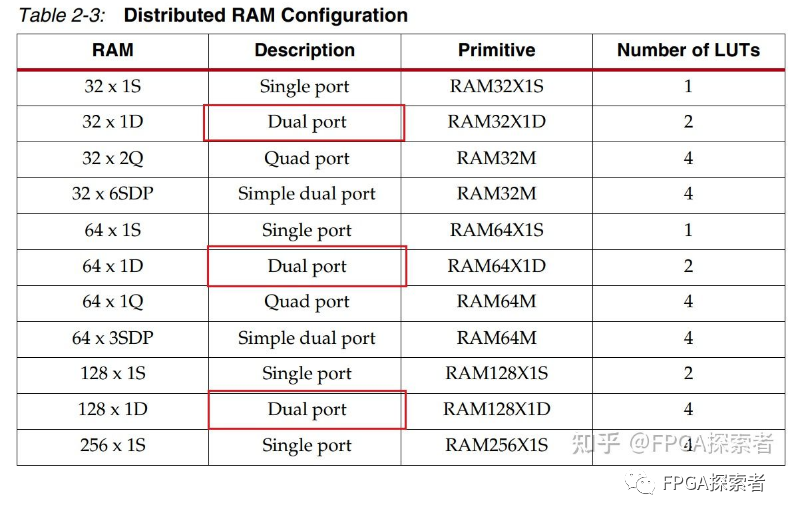

FPGA双口RAM的使用主要涉及配置和使用双端口RAM模块。双端口RAM的特点是有两组独立的端口,可以对同一存储块进行读写操作,从而实现并行访问。

在使用FPGA双口RAM时,首先需要定义一个双端口RAM的模块,包括地址和数据输入输出端口、读写使能端口,以及两个独立的读写端口。在Verilog HDL等硬件描述语言中,可以通过读写控制信号来实现双端口的读写操作。例如,当读写控制信号为1时,将指定的内存地址中的数据写入或读出。

在配置双口RAM时,需要注意写保护操作,以防止多个写操作同时发生。这可以通过引入互斥机制来实现。同时,还需要考虑到不同读写操作间存在的时序问题,以确保读写操作能够按正确的顺序进行。

在仿真测试阶段,可以通过编写仿真激励来interwetten与威廉的赔率体系 双口RAM的读写操作。例如,可以设置特定的读写地址和数据,观察RAM的输出是否符合预期。通过这种方式,可以验证双口RAM的功能和性能。

总的来说,FPGA双口RAM的使用涉及多个方面,包括模块定义、配置、读写控制和仿真测试等。通过合理使用双口RAM,可以实现并行访问和高效数据处理,提高FPGA系统的性能和灵活性。

请注意,具体的使用方法可能会因FPGA芯片型号、开发工具以及应用场景的不同而有所差异。因此,在实际应用中,建议参考相关文档和教程,以确保正确配置和使用FPGA双口RAM。

-

FPGA

+关注

关注

1629文章

21729浏览量

603023 -

RAM

+关注

关注

8文章

1368浏览量

114649 -

端口

+关注

关注

4文章

964浏览量

32052

发布评论请先 登录

相关推荐

基于FPGA的双口RAM实现及应用

在做fpga双口ram的时候 这是我做的仿真 为什么读地址、和写地址计数只能读到7

基于FPGA的双口RAM与PCI9O52接口设计

基于cyclone EP1C6的LED 屏设计方案

基于FPGA的双口RAM实现及应用

基于cyclone EP1C6的LED大屏方案

fpga双口ram的使用

fpga双口ram的使用

评论