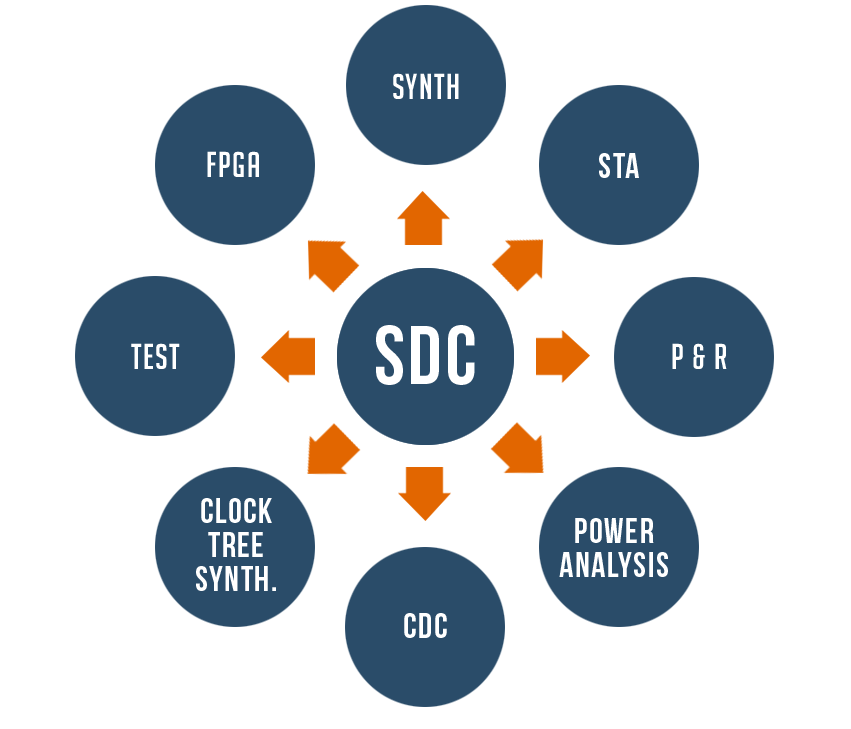

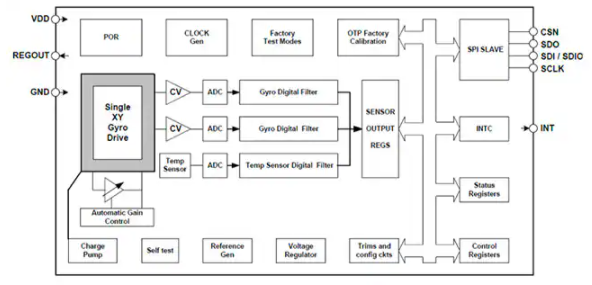

SOC设计变得越来越复杂,成本越来越高,设计和验证也越来越困难。设计尺寸、众多的IP、先进威廉希尔官方网站 节点、时钟和时钟域数量的增加,以及multi-mode/multi-coner组合中为时序收敛造成设计约束变得越来越复杂。为高效的应对复杂的设计约束,需要一个完整的产品来生成、管理,整合和验证与静态时序分析引擎相关的设计约束,以确保设计的正确性。

在约束、时钟或时序方面的错误所造成的巨大代价通常迫使设计团队采取最小化策略——设计一个完全最小的、安全的、最不容易出错的时序约束集合。设计领域经验丰富的领导者认识到这是一个复杂的、多方面的问题,需要各种能力和威廉希尔官方网站 来解决。简单的结构或语义工具和方法只能捕获简单的问题,而且会产生大量的误报信息,需要设计人员进行检查。一个完善的解决方案应该是辅助和帮助设计团队创建设计约束条件,覆盖设计需求,使其满足功耗、性能和面积目标,同时最小化由于时钟或时序问题而导致的其他风险。

为解决上述问题,Excellicon公司提供了Conman和Concert的组合解决方案,来帮助设计公司应对各种在设计中出现的SDC问题。

Conman:设计约束文件的编译和管理

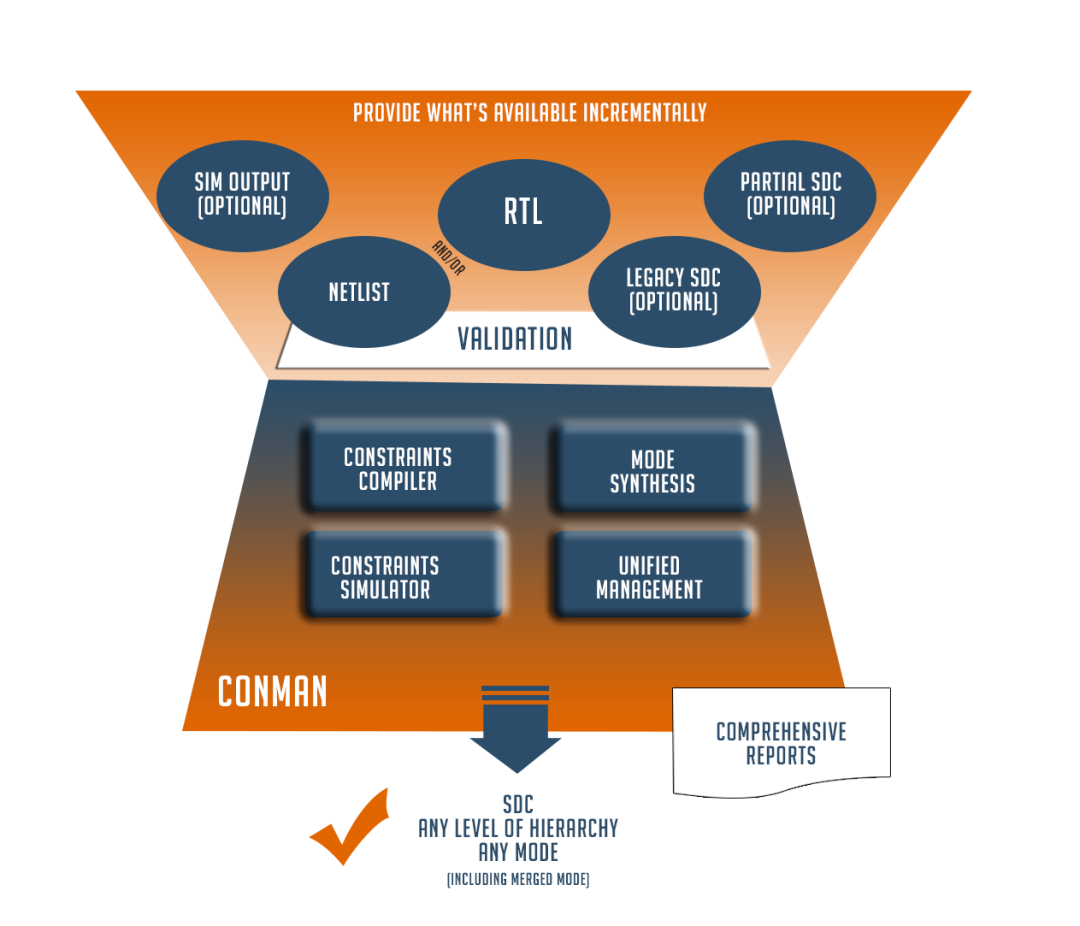

ConMan是第一个商用的形式化设计约束编译器工具,它可以自动为任何层次结构和SoC的任何模式生成SDC,从而大大缩短了时序收敛的周期。ConMan提供了一种直观的方法,可以自动编译和管理针对于不同设计的sign off质量级别的、构造及正确的时间约束文件,且工具已经通过ISO2626认证。

ConMan还通过在设计周期的早期将前端与后端对齐来重新定义时序约束,从而消除了仿真测试中假设的时序与SDC文件中用于实现时序之间的断层。 ConMan生成并维护单一数据源,供前端和后端设计人员使用,以捕获、生成和管理所有操作模式的设计时序约束,同时在设计的所有阶段向设计人员提供反馈。使用ConMan,设计人员可以从前端工程师开始RTL开发,一直到后端团队的实现阶段,开始生成时序约束。所有信息通过ConMan跟踪,并可以通过报告或可视化的interwetten与威廉的赔率体系 计时数据进行查看。

设计人员可以手动提供时序信息,也可以选择从旧的SDC或通过设计层次结构的任何块的仿真结果提取时序信息。ConMan使用其强大的形式化符号仿真引擎自动验证所有的输入数据,然后在设计层次结构中组装和传播所有的时序数据,解决时序冲突,并在需要时向设计师提供数据以进一步细化。

ConMan平台包含以下组件:

仅以RTL或gate作为输入的多模式约束生成Multi-Mode Constraints

约束管理

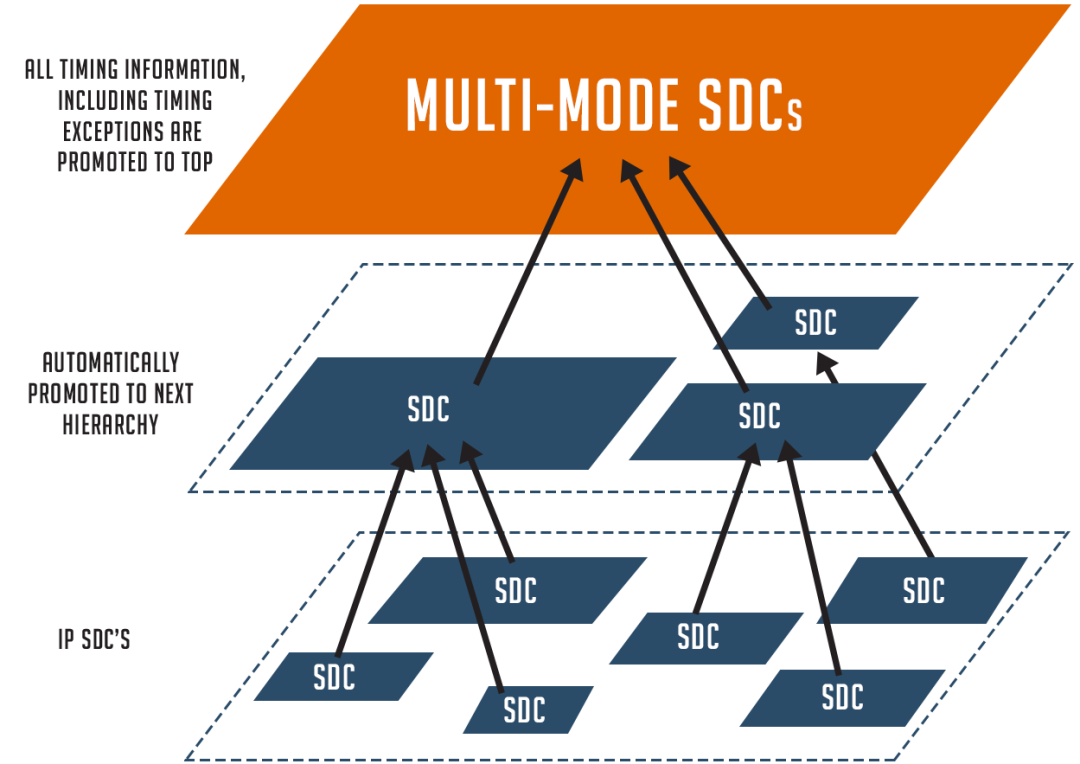

约束设定的提升(promotion)

时钟可视化与分析

Multi-Mode Constraints Generation

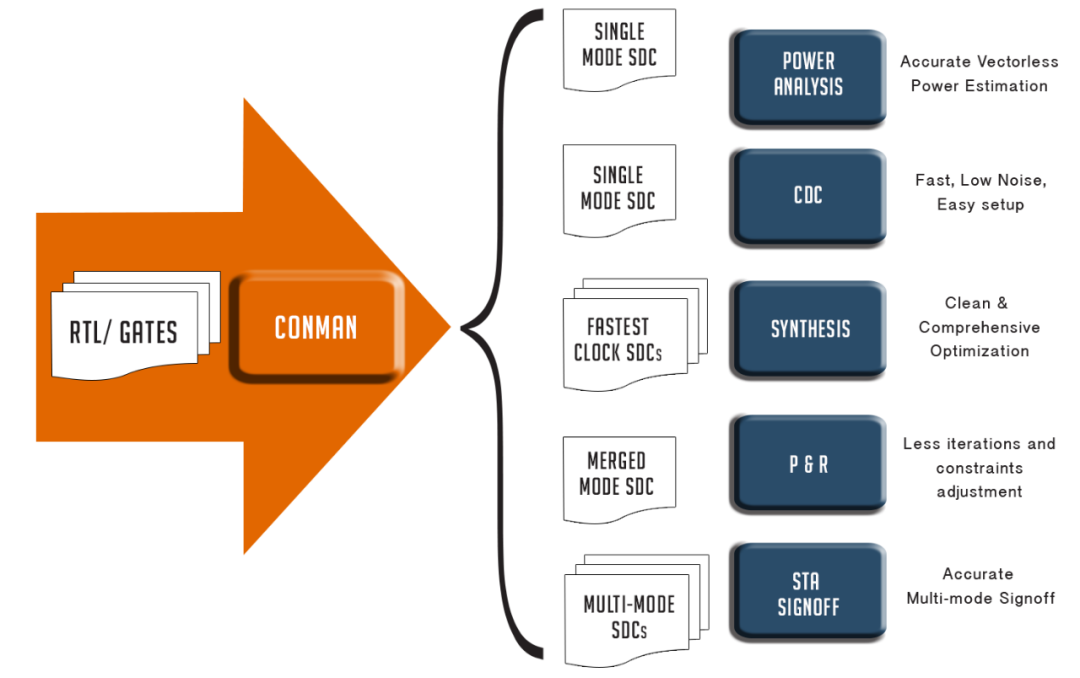

ConMan生成SDC格式的全面时序约束,适用于任何设计层次和任何模式。不需要SDC语法知识。

sdc用于任何层次结构,任何模式和任何类型- RTL或Gates

不同类型:单模式,合并模式-层次化或者扁平化100%发现所有时钟和模式引脚

完整的SDC时序约束,包含时钟,时序异常,Case Analysis,IO延迟,时钟组,drc等。

单数据库多模式,RTL和Gate的时序约束

约束管理

约束管理

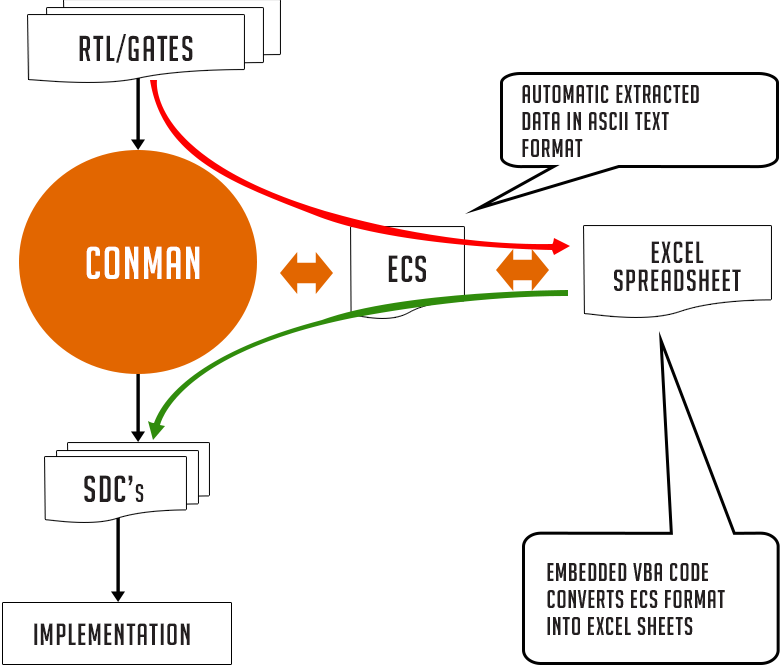

ConMan提供了Excel的无缝接口,通过该接口,所有的时序约束都可以在工具外部进行管理或修改。这种双向接口允许设计师使用熟悉的Excel电子表格格式来检查时序数据,并在需要时修改它。

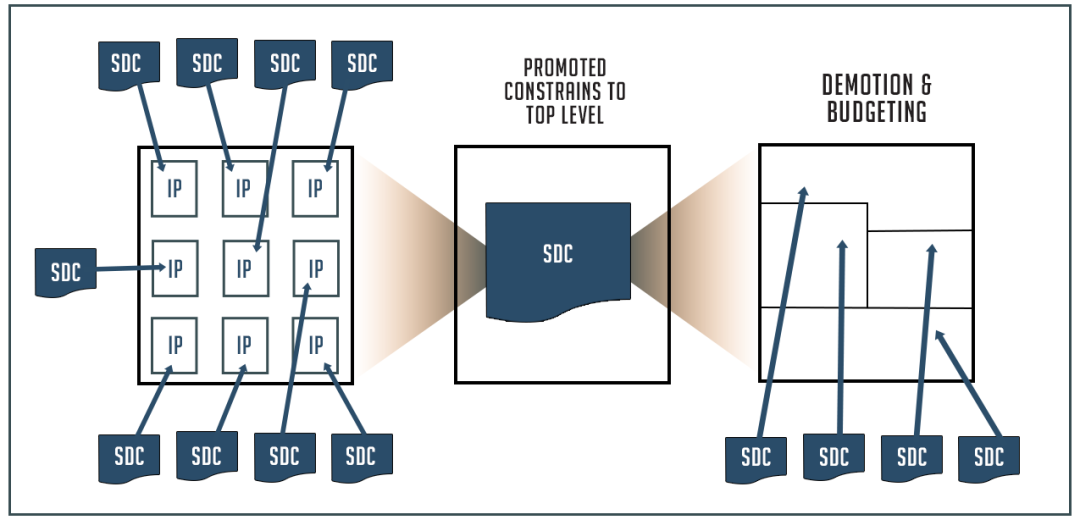

约束条件的提升(Promotion)

目前,约束的大多数传播都是使用操作层次分隔符的手工方法完成的。这种威廉希尔官方网站 增加了在编辑过程中引入错误和丢失约束的风险。Excellicon的多传播功能不仅自动化方式节省设计师手工编辑数据需要花费数周的过程,而且还为设计师提供了很大的灵活性来处理他们可能遇到的任何情况,既然他们试图生成适当的高质量的约束。

ConMan提供了三种威廉希尔官方网站

,用于将较低级别的时序约束提升到层次结构的任何层。支持混合使用这三种方法。

集成方法- IP时序约束允许改变作为顶层设计结构的结果

隔离方法—IP时序约束保持原样。

上下文方法——顶层和低级别的约束都可用,但它们不在彼此的上下文中。随着设计者定义和指导的时序约束的增量传播而进行推广。

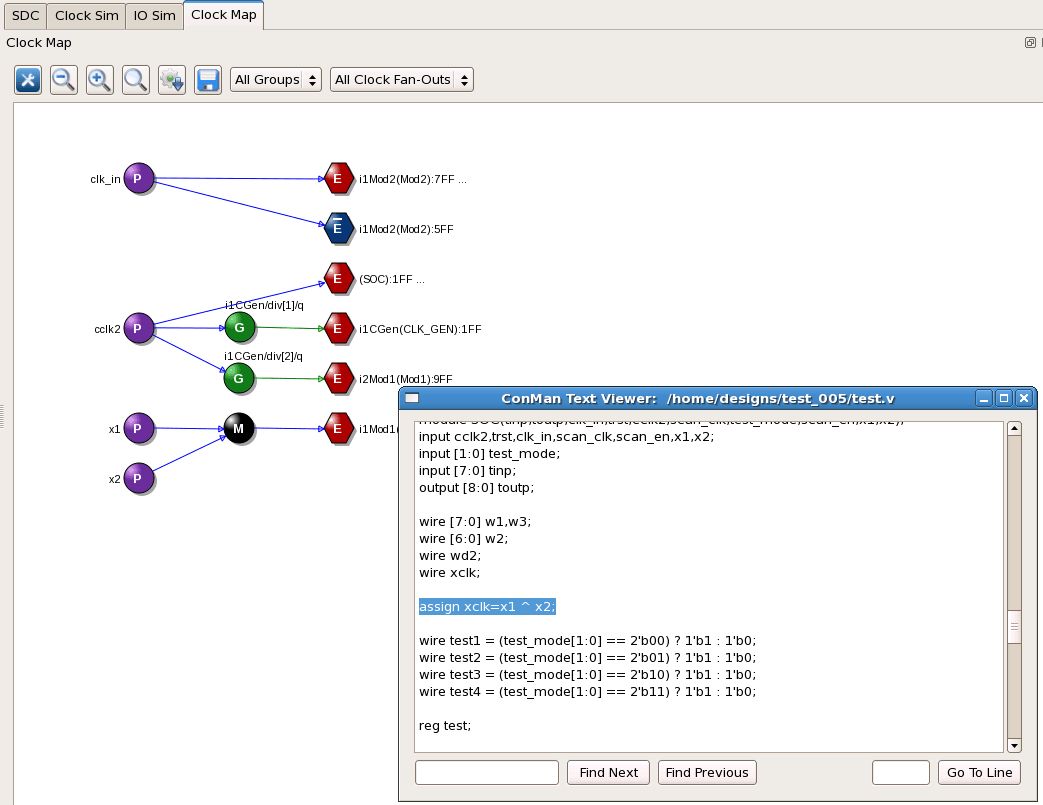

时钟可视化与分析

理解任何设计的时钟总是最困难的任务之一,并且非常容易出错。现有的解决方案绘制了一个完整的逻辑示意图,从其中识别时钟逻辑不仅是困难的,有时是不可能的。

ConMan利用一种直观的抽象方法来显示时钟图(自动从HDL中提取),从中设计者可以快速理解任何层次结构、全平面或分层视图的时钟逻辑。此外,ConMan使用其正式引擎使设计人员能够执行时钟传播的“假设”分析,以创建不同的操作模式。

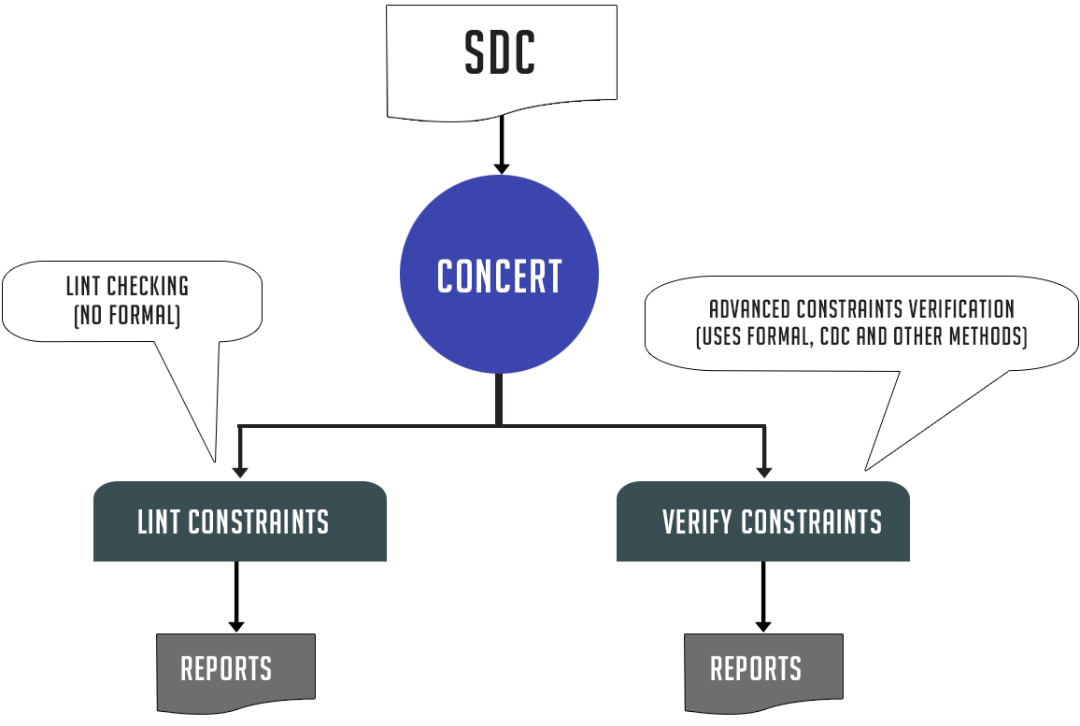

ConCert :约束证明平台

ConCert 是一个sign off平台,为 ASIC/SOC 或 FPGA 流程的任何阶段的提供时序约束验证、降级(Demotion)和预算(Budgeting)独一无二的系统。

ConCert 平台包含以下组件:

约束验证

Exception工具箱

Demotion和Budgeting工具箱

等价检查

设计分析

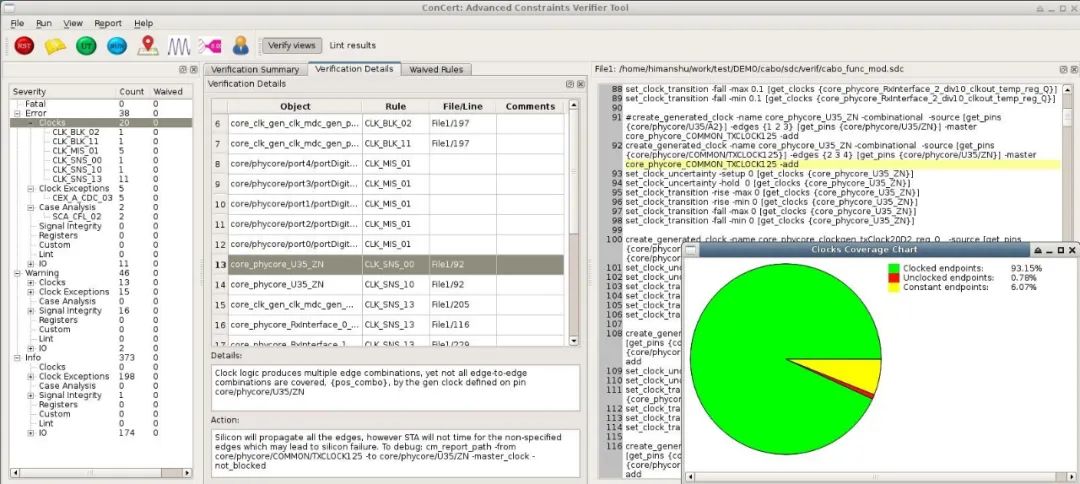

约束验证

ConCert 使用形式化算法来验证时序约束,从而提供对设计及其相关时序约束的准确深入分析。ConCert 的约束验证方法不同于当今市场上可用的传统工具。传统工具主要是通过使用数千条规则来关注语法和基本正确性的 SDC linter。这总是会在输出报告中产生大量噪音。此外,时序意图丢失并且无法通过此类传统工具进行分析。

ConCert 除了 linting 之外,还利用其形式化引擎来分析设计和 SDC 文件的行为。提取设计的时序意图和相关的 SDC 文件并进行比较,以生成精确的分析报告。这种方法可以消除噪声输出,并将约束验证领域扩展到下一代,远远超出语法和基本检查。

此外,通过 ConCert,设计人员还可以在原始 SDC 缺少约束的情况下生成增量 SDC,或者使 SDC 信号完整性相兼容。

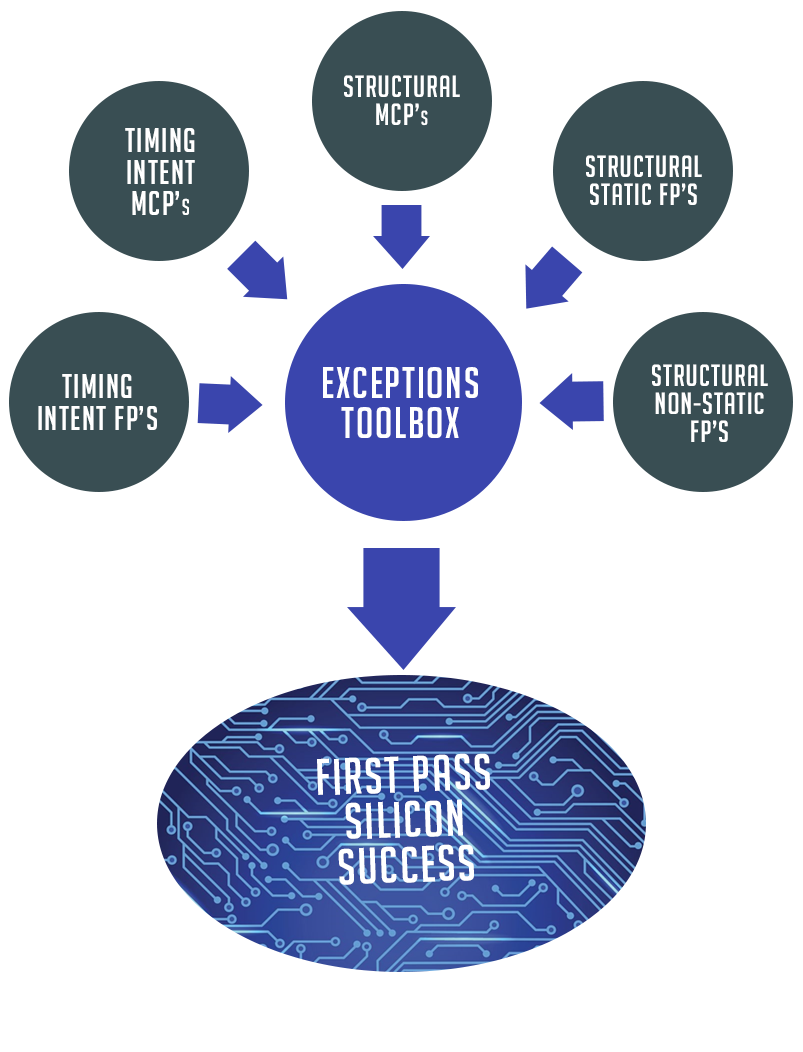

例外工具箱

时序约束文件通常包含大量异常,例如错误路径 (FP) 和多周期路径 (MCP)。此类例外通常分为“结构”和“时间意图”例外。结构异常取决于设计结构,可以通过形式化威廉希尔官方网站 进行验证。然而,时序意图类型的异常与设计结构无关,即它们基于设计人员的意图(例如对所有复位引脚设置错误路径约束),因此不能使用形式化威廉希尔官方网站 来验证它们。

典型时序约束文件中大约 20% 的 FP 和 MCP 异常属于结构类型。然而,挑战在于其余 80% 的例外情况,这些例外情况属于 RTL 设计人员在功能设计时定义的时序意图性质。由于形式化威廉希尔官方网站 不能用于此类异常,设计人员传统上通过手动审查约束文件来验证它们。

ConCert-ET 是 ConCert 的一个插件,是当今市场上唯一的工具,不仅可以通过形式化方式验证结构异常,还可以使用专有方法验证时序意图类型的异常。

约束模拟

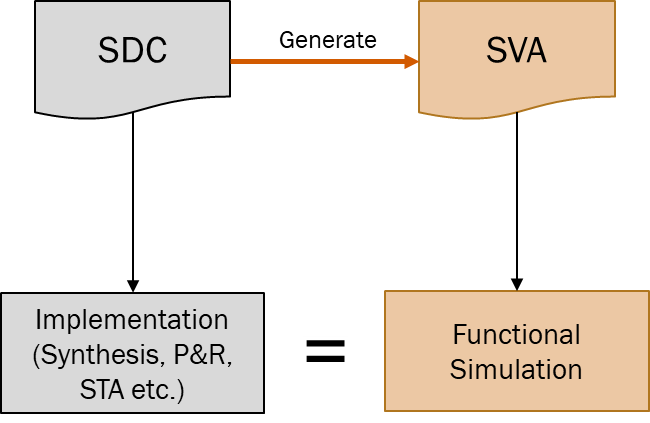

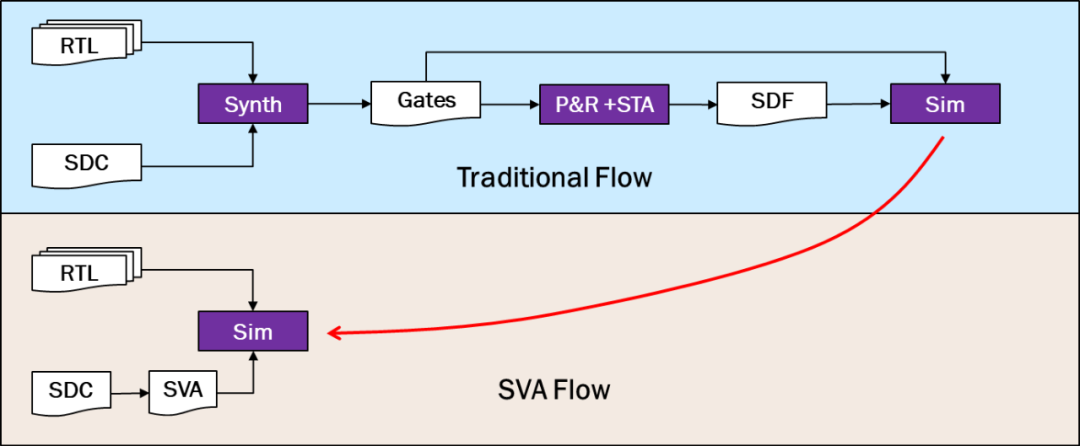

通常,对 RTL 进行仿真以确保功能正确性。与设计相关的时序以 SDC 格式捕获,与 RTL 功能无关。设计的两个方面,即功能和时序,仅在设计周期后期执行 SDF 反标的GLS仿真时才对齐。

即使有了约束验证工具、LEC、STA、CDC 分析和故障分析工具等静态工具的可用性,人们仍会假设不需要 GLS。然而,今天不存在可以验证时序约束的时序意图性质的 EDA 解决方案。时序意图是指独立于设计结构但基于设计者意图的约束。例如,SDC文件中定义的复杂时钟波形;或在 SDC 文件中指定的错误/多周期路径不是基于逻辑结构,而是基于设计人员的经验和只是来指定。

这就需要 GLS 来捕捉这些类型的问题。但是,GLS 的一个主要问题是设置 GLS 环境是一项极其繁琐的任务。为了规避这些问题并帮助在 ASIC 周期的早期阶段仿真设计(无需通过 SDF 进行延迟反标),Excellicon 开发了一种 ABSV(基于断言的 SDC 验证)功能,其中相关的时序约束被转换为可在仿真期间使用的 SVA。

这种方法消除了运行 SDF反标的 GLS 的需要,从而显着减少了循环迭代时间。SVA 也可以在 RTL 阶段进行仿真,从而完全简化整个流程。

降级和预算

ConCert-BT 是 ConCert 的一个附加组件,使设计人员能够以从 RTL 到物理实现的不同精度级别执行约束降级(demotion)和分层预算(budgeting)。

该产品具有完整的功能:

约束降级

预算生成

基于百分比

基于逻辑的层次

基于固有单元延迟和布局寄生的延迟

验证所有设计macros的预算

手动细化预算

根据 STA 时序slack值自动重新分配时序预算

具有每个macros过去的预算历史进行分层预算管理

使用 ConMan,设计人员可以将 IP 约束提升到顶层,随后通过 ConCert-BT 可以将约束降级到 P&R 活动的宏观层面。ConCert-BT 在配置工具以选择性地降级某些约束或自动降级所有约束方面提供了充分的灵活性。

随着设计在物理实现过程的趋于稳定,时序预算也会不断变化。这包括对 ECO 的 RTL 更改,这可能会导致设计中各个模块之间的时序不平衡,这需要调整 IO 延迟值以解决macros之间的时序违反问题。设计人员必须找到一种重新分配预算的方法,以解决False路径的时序问题;手动完成的方式会导致长时间的迭代,并且通常是芯片的次优时序。

由于物理实现工程师团队在他们自己的模块上并行工作,接口时序必须考虑准确的预算,以使顶层时序顺利通过而没有任何违反。前端设计人员可以使用 ConCert-BT 在实施周期的早期阶段使用基于百分比或基于逻辑的预算生成适当的预算,而后端工程师可以利用最强大的物理预算生成使用平面图信息进行预算,并在整个时序收敛周期中管理预算,包括创建时序模型,从而在流片前进行最终迭代。

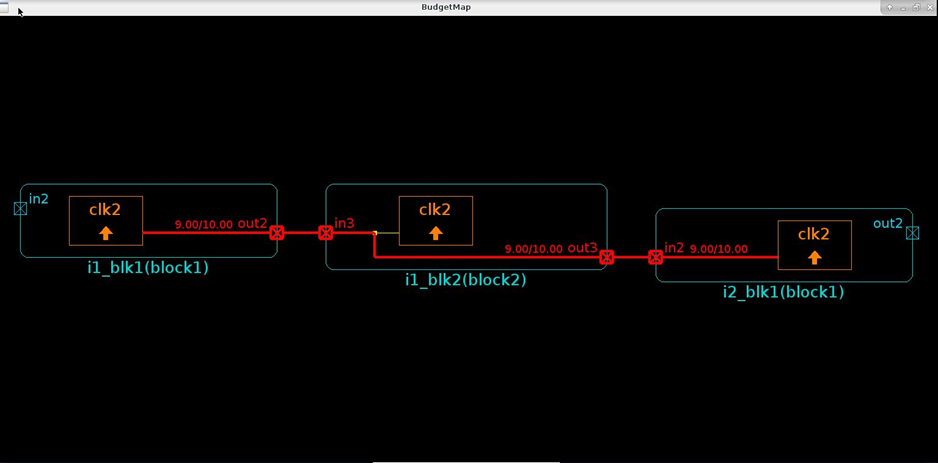

ConCert-BT 提供了一个全面的解决方案,不仅可以跨macros验证现有预算的正确性,还可以通过其直观的 Budget Map GUI 显示预算。通过 BudgetMap,设计人员可以轻松调试失败的路径并采取纠正措施。

等价检查

随着设计从一个设计阶段进展到另一个设计阶段,约束总是会发生变化。可能会添加新的约束或修改现有的约束,这可能会导致时序约束不等效并失去最初的意图。

由于 SoC 是层次化设计的,因此可能存在模块级时序可能与顶层时序不相关的情况。当执行顶层完全扁平(flatten) STA 时,这可能会出现问题。

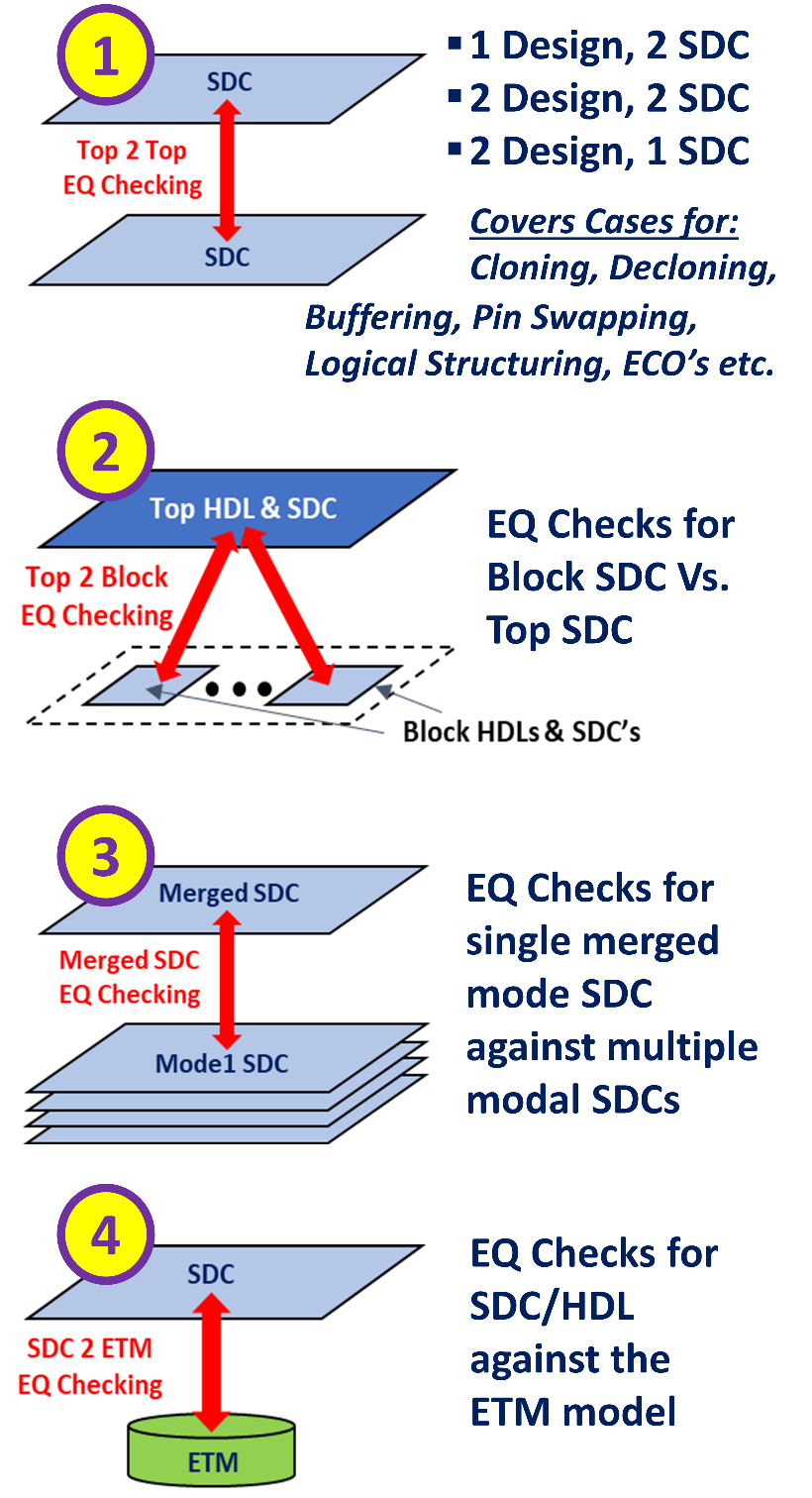

因此,需要证明约束之间的时序等效性。ConCert 提供两种等效方法:

Top to Top——检查设计周期不同阶段之间的约束等效性

Top to Block – 检查顶层约束和模块间的约束等效性

审核编辑:刘清

-

EDA工具

+关注

关注

4文章

267浏览量

31789 -

SoC设计

+关注

关注

1文章

148浏览量

18774 -

信号完整性

+关注

关注

68文章

1405浏览量

95459 -

RTL

+关注

关注

1文章

385浏览量

59763 -

SDC

+关注

关注

0文章

48浏览量

15534

原文标题:SOC中的SDC约束正变得越来越庞大和复杂,我们该如何应对

文章出处:【微信号:ExASIC,微信公众号:ExASIC】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

IC datasheet为什么越来越薄了?

蓝牙威廉希尔官方网站 越来越鸡肋

为什么RF滤波器越来越重要?

如何将Altera的SDC约束转换为Xilinx XDC约束

黑科技大盘点 机器人已经在我们的生活中越来越普及

不得不承认人类越来越像人工智能了!

自动驾驶供应链的关系越来越复杂 成本问题成发展的核心

看门狗功能在 MCU 应用中越来越重要

为什么FPGA在原型验证中越来越重要

可穿戴设备中的传感器:尺寸越来越“小”,左右越来越“大”

我们的城市为什么越来越热?

我们该如何应对SOC中越来越庞大和复杂的SDC约束?

我们该如何应对SOC中越来越庞大和复杂的SDC约束?

评论