AnaPico公司的APPH系列相噪分析仪以-190dBc/Hz的本底噪声和小于5fs本底抖动而具有极高的灵敏度,能够以高于时域抖动的灵敏度测量频域中的相位噪声并及其便利的转换为对应的抖动数值。

APPH相位噪声分析仪

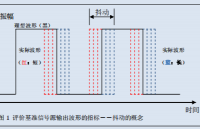

APPH相位噪声分析仪抖动(Jitter):反映的是数字信号偏离其理想位置的时间偏差。高频数字信号的bit周期都非常短,一般在几百ps甚至几十ps,很小的抖动都会造成信号采样位置电平的变化,所以高频数字信号对于抖动都有严格的要求。

实际信号可能具有较高复杂性,比如既有随机抖动成分(RJ),也有不同频率的确定性抖动成分(DJ)。确定性抖动可能由于码间干扰或一些周期性干扰引起,而随机抖动很大一部分来源于信号上的噪声。一般我们把数字信号超过阈值的状态判决为“1”,把低于阈值的状态判决为“0”,由于信号的上升沿不是无限陡的,所以垂直的幅度噪声就会造成信号过阈值点时刻的左右变化,这就是由于噪声造成信号抖动的原因。

要进行信号抖动的分析,最常用的工具是宽带示波器配合上响应的抖动分析软件。示波器里的抖动分析软件可以方便地对抖动的大小和各种成分进行分解,但是,现在很多高速芯片对时钟的抖动要求都在1ps以下甚至fs级。这就需要借助于其它的测量方法,比如相位噪声(phase noise)的测量方法。

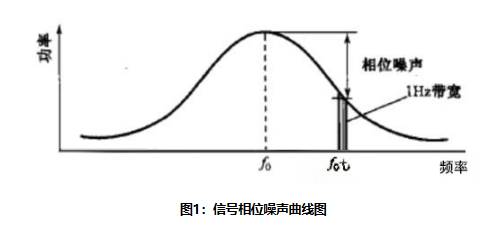

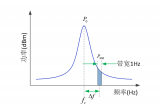

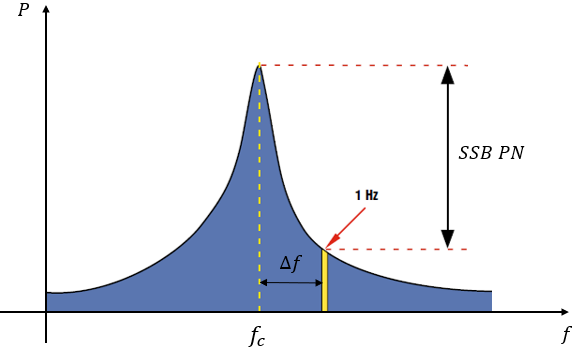

相位噪声:在频域上,数据偏移量用相位噪声来定义。对于频率为f0的时钟信号而言,如果信号上不含抖动,则信号的所有功率应集中在频率点f0处,由于任何信号都存在抖动,这些抖动有些是随机的,有些是确定的,分布于相当广的频带上,因此抖动的出现将使信号功率被扩展到这些频带上。信号的相位噪声,就是信号在某一特定频率处的功率分量,将这些分量连接成的曲线就是相位噪声曲线。相位噪声通常定义为在某一给定偏移处的dBc/Hz值,其中dBc是以dB为单位的该功率处功率与总功率的比值。如一个振荡器在某一偏移频率处的相位噪声定义为在该频率处1Hz带宽内的信号功率与信号总功率的比值,即在fm频率处1Hz范围内的面积与整个噪声频率下的所有面积之比。

从相位噪声曲线图1可知,绝大多数抖动都集中在频率f0附近,距离f0越远的频段,抖动能量越小。

以下面的例子为例,说明对时钟输入的要求:

RMS JPER(12kHz~20MHz):0.5ps

相位噪声(10~100kHz):-120dBc/Hz

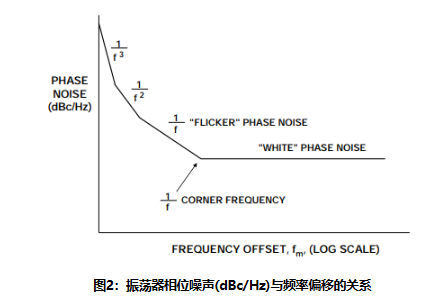

通常用单边带相位噪声来描述振荡器的特性,如图2的相位噪声(dBc/Hz)与频率偏移fm的关系曲线所示,其中频率轴采用对数刻度。注意,实际的曲线由多个区域拟合而成,各区域的斜率为1/fx,x=0对应于“白色”相位噪声区域(斜率=0dB/10倍),x=1对应于“闪烁”相位噪声区域(斜率=–20dB/10倍)还存在x=2、3、4的区域,这些区域依次出现,愈来愈接近载波频率。

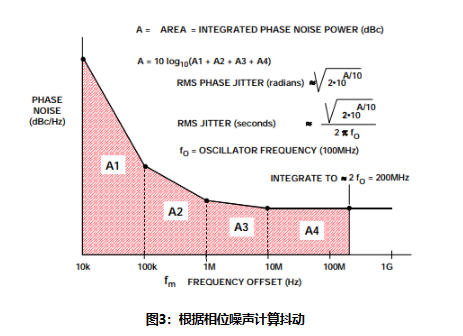

我们已经看到,振荡器通常用相位噪声来描述性能,但为了将相位噪声与ADC的性能关联起来,必须将相位噪声转换为抖动。为将该曲线与现代ADC应用关联起来,选择100MHz 的振荡器频率(采样频率)以便于讨论,典型曲线如图3所示。请注意,相位噪声曲线由多条线段拟合而成,各线段的端点由数据点定义。

计算等效rms抖动的第一步是获得目标频率范围(即曲线区域A)内的积分相位噪声功率。该曲线被分为多个独立区域(A1、A2、A3、A4),各区域由两个数据点定义。一般而言,假设振荡器与ADC输入端之间无滤波,则积分频率范围的上限应为采样频率的2倍,这近似于ADC采样时钟输入的带宽。

积分频率范围下限的选择也需要一定的斟酌。理论上,它应尽可能低,以便获得真实的rms抖动。但实际上,制造商一般不会给出偏移频率小于10Hz时的振荡器特性,不过这在计算中已经能够得出足够精度的结果。多数情况下,如果提供了100Hz时的特性,则选择100Hz作为积分频率下限是合理的。否则,可以使用1kHz或10kHz数据点。

还应考虑,“近载波”相位噪声会影响系统的频谱分辨率,而宽带噪声则会影响整体系统信噪比。最明智的方法或许是对各区域分别积分,并检查各区域的抖动贡献幅度。如果使用晶体振荡器,则低频贡献与宽带贡献相比,可能可以忽略不计。其它类型的振荡器在低频区域可能具有相当大的抖动贡献,必须确定其对整体系统频率分辨率的重要性。

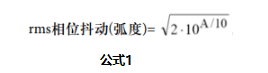

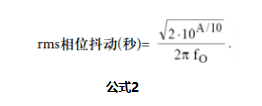

各区域的积分产生个别功率比,然后将各功率比相加,并转换回dBc。一旦知道积分相位噪声功率,便可通过下式计算rms相位抖动(单位为弧度)

以上结果除以2πfO,便可将用弧度表示的抖动转换为用秒表示的抖动。

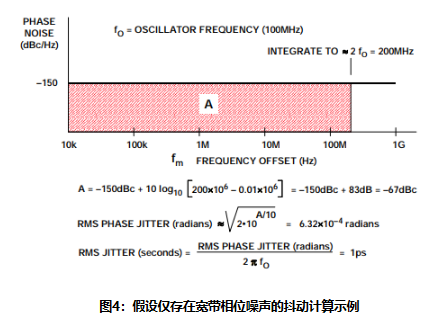

图4给出了一个计算示例,它假设仅存在宽带相位噪声。所选的–150dBc/Hz宽带相位噪声代表了良好信号发生器的特性,由此获得的抖动值可以代表实际情况。–150dBc/Hz的相位噪声(用比值表示)乘以积分带宽(200MHz),得到–67dBc的积分相位噪声。请注意,该乘法相当于把10log10[200MHz–0.01MHz]的量与相位噪声(dBc/Hz)相加。实际上,计算中可以丢弃0.01MHz的频率下限,因为它不会对最终结果产生重大影响。利用公式2可知, 总rms抖动约为1ps。

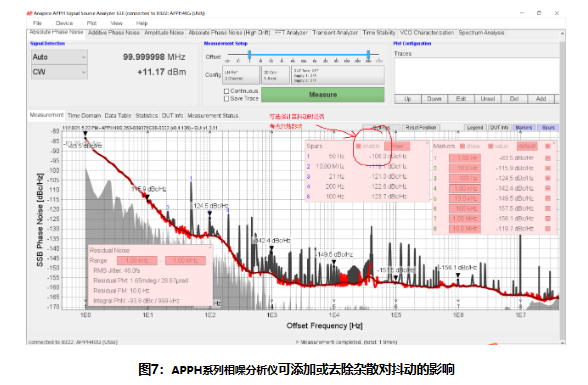

在实际测试中,抖动值的来源除了相位噪声还要包含信号杂散,因此实际换算时必须把所有因素考虑进去。AnaPico的APPH系列相位噪声分析仪可以进行绝对相位噪声测试时将这些因素综合考虑或单独考虑。

结论:相位噪声和抖动是对同一种现象的两种不同的定量方式(描述)。抖动是一个时域概念,单位是ps或fs。相位噪声是频率域的概念,相位噪声是用偏移频率fm处1Hz带宽内的矩形的面积, 与整个功率谱曲线下包含的面积之比表示的,单位为-dBc/Hz。随着现代数字系统的时钟频率越来越高,对高速芯片对时钟的抖动要求都在1ps以下甚至fs级。示波器已经无法满足相关的测试要求,因此必须采用灵敏度更高的相位噪声分析仪。AnaPico公司的APPH系列相噪分析仪以-190dBc/Hz的本底噪声和小于5fs本底抖动而具有极高的灵敏度,能够以高于时域抖动的灵敏度测量频域中的相位噪声并及其便利的转换为对应的抖动数值。

-

芯片

+关注

关注

455文章

50757浏览量

423359 -

相位噪声测量

+关注

关注

0文章

3浏览量

6003

发布评论请先 登录

相关推荐

数字振荡器的相位噪声是多少

高速信号传输中的抖动和眼图挑战

应对高速芯片从相位噪声到时间抖动的挑战

应对高速芯片从相位噪声到时间抖动的挑战

评论