大模型时代已经到来,AI大模型威廉希尔官方网站 快速成熟,进入万亿参数时代,对于AI算力性能要求越来越高,表现为计算系统的节点内卡间互联与节点间的网络互联,高速互联的底层是PCIe,对于PCIe的威廉希尔官方网站 迭代和落地迫切。

一、PCIe 5.0 /6.0威廉希尔官方网站 升级

1)信号速率方面

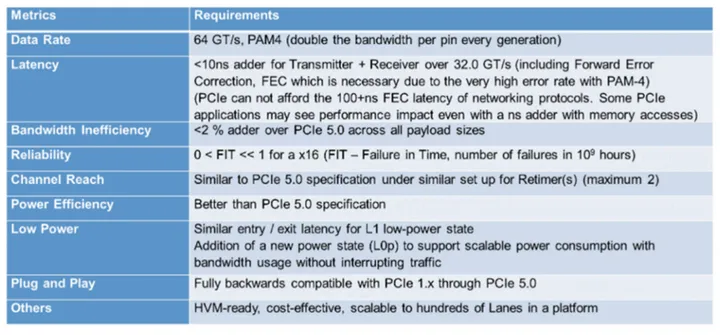

从PCIe 3.0、4.0、5.0 到 6.0,数据速率翻倍递增,6.0支持64GT/s,16路双向传输带宽可达256GB/s。

图1:PCIe威廉希尔官方网站 变化2)调制格式方面

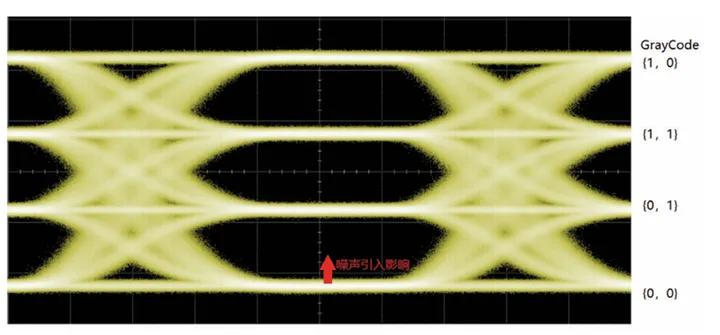

PCIe 3.0-5.0 都采用NRZ调制格式,在PCIe 6.0时首次采用高阶调制格式PAM4,在信号幅度相同的情况下信噪比天然会下降约9.5dB,因此对噪声更加敏感(比如电源噪声、串扰、反射等),为降低该影响,采用了格雷码映射(MSB,LSB),如下展示了格雷码映射的PAM4眼图,在噪声影响下,低比特LSB更易引起反转导致出错,若噪声幅度较高,也会引起2bit反转,但概率较低。

图2:PAM4 眼图

3)收发架构方面

为支持PAM4调制格式,通常采用DAC产生信号,ADC接收信号,发送侧为克服传输链路影响,通常会用多抽头的FIR实现,PCIe 6.0采用4抽头的FIR,接收侧为补偿高频损耗和多比特码间干扰会用到CTLE+DFE,当前架构会利用DSP威廉希尔官方网站 根据ADC模数转换的数据点实现数字域处理,该威廉希尔官方网站 也可以有效克服PVT的变化对信号带来的影响。

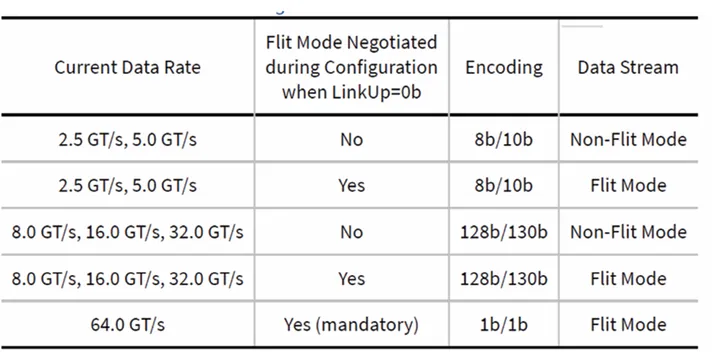

4)编码与数据流方面PCIe 3.0-5.0 均采用128b/130b编码方式,相比PCIe 1.0-2.0 降低了开销提高了编码效率,默认支持Non-Flit流模式,PCIe 6.0采用1b/1b编码并且必须支持Flip流模式。Non-Flit模式支持可变大小TLP、4字节CRC用于TLP、2字节CRC用于DLLP。而Flit模式则支持256字节固定长度包括235字节TLP、6字节DLP、8字节CRC 和6字节FEC,没有Sync Header/Framing Token,TLP 和DLLP 没有独立的CRC,通过这些开销的优化相对提高了带宽利用率。

图3:PCIe速率、Flit、编码等特点

5)互连通道及连接器方面

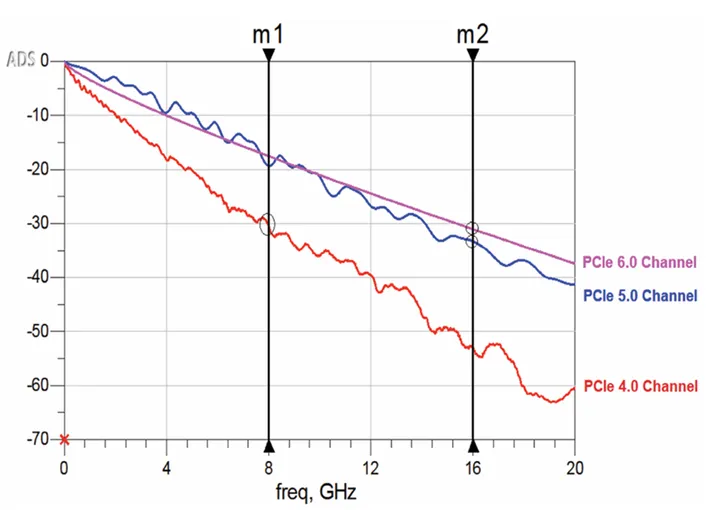

PCIe 5.0~6.0 相比PCIe 1.0~4.0 速率高,SI、PI 要求也有提高。电源方面,插卡最大功耗可提升至600W,将 在 6.0 CEM中更新;信号方面为保证信号完整性要求使用表贴连接器;互连通道方面,与PCIe 5.0类似,要求主板支持约12 inch,插卡支持约3-4 inch,可以想象下,如果PCIe 6.0仍旧采用NRZ调制格式,64GT/s速率奈奎斯特频点在32GHz,那 么 通 道 IL将小于-60dB(参考下图通道仿真结果),很难通过现有威廉希尔官方网站 实现该信号的高频补偿,考虑实现成本和威廉希尔官方网站 复杂度,采用高阶调制PAM4是种不错选择,相比PCIe 5.0奈奎斯特频率不变,当前可用板材下可传输相似距离。

图4:不同信道插损仿真图

6)误码率方面PCIe 3.0~5.0 均要满足1E-12,PCIe 6.0 由于采用PAM4,对噪声和反射更敏感,结合格雷码映射特点(易发生单bit 错 误 ), 接 收 侧 会 关 注 first bit error,规范会用FBER衡量。由于链路接收机会用到DFE均衡,若有单bit出错,它这会引起后续接连出错。如果造成误码的源是共有的,比如电源噪声,那么也会引起其他lane出错,系统BER依赖于FBER和lane间的错误相关性。规范定义了FBER是1E-6,那么为什么是1E-6呢?能否放宽至1E-4, 满足PCIe 5.0通常的传输距离或IL目标呢?答案是否定的。参考以太网标准放宽至1E-4,需要使用复杂RS-FEC 纠错,延时将增加到约100ns量级,这对负载和存储等对时延敏感的应用是一个很大的挑战。一旦确定FEC威廉希尔官方网站 将应用至整个PCIe 6.0的生命周期,传输通道优化还有其他更多手段,比如更新板材,更复杂信号调理等。为满足FBER=1E-6目标,PCIe 6.0引入轻量级FEC和鲁棒性强的CRC算法实现修正和错误检测。相比100G/400G以太网标准中经常用到的RS(544,514), 该 FEC实现相对简单,在固定包长度Flit模式下,6字节的FEC“保护”242字节Payload和8字节CRC,2字节1组实现FEC Group通过交织方式抵抗突发错误。如果FEC解码完成,但CRC仍检测到错误,那么接收侧会发送NAK启动重传,为提高效率,该模式下不会重传NOP-only TLP 包。通过上述FEC、CRC适配FBER=1E-6 要求,同时保证出错情况下重传概率在5E-6、带宽额外消耗约0.05%、FIT接近0。

图5:展示PCIe 6.0的重要变化

二、PCIe 6.0 测试测量挑战

1)PCIe 6.0 规范状态

当前PCIe 6.0 Base spec v1.0 已经发布,CEM Spec 和Phy Test Spec 还在讨论中。

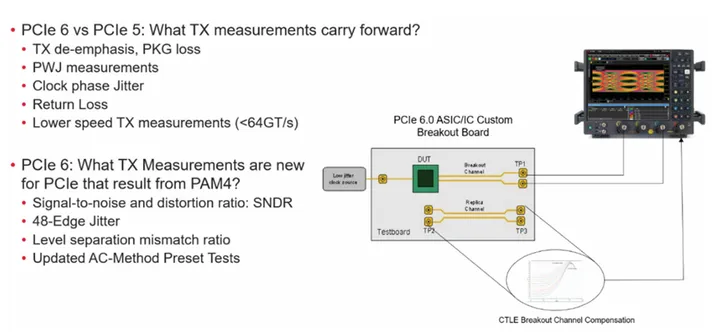

2)Tx 信号完整性方面

相比PCIe 5.0,PCIe 6.0新增了SNDR、RLM、JnU、Jrms 和Preset 测试。

图6 PCIe 6.0 Tx 测试参数变化

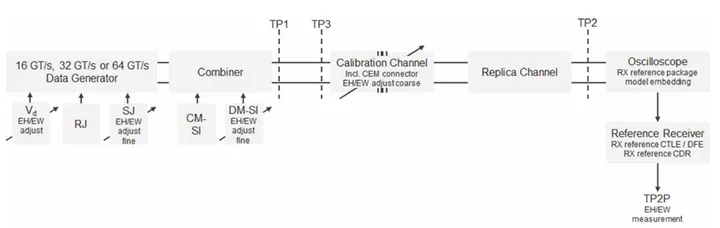

3)Rx接收误码率方面在16G、32G和64GT/s接收校准时RJ不再是主要调节目标EH/EW的参数,通过信道自身插损调节实现粗调,SJ/DMSI 实现细调,综合实现目标EH/EW。Rx Reference Package的S参数模型是嵌在示波器中实现的,通过TP2端面信号测量和嵌入S参数的计算并结合参考的CTLE+DFE/CDR得到TP2P EH和EW。这里的EH和EW是目标PAM4眼图的Top Eye 参 数( 6mV EH / 0.1 UI EW @1e-6 BER)。目 前Sigtest 还未发布,校准时采用seasim 作为数据处理工具。

图7:PCIe 6.0芯片Rx校准

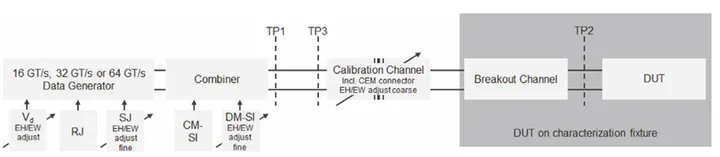

64GT/s 接收测试时,无论是芯片还是 CEM,通常需要进行链路训练进入loopback,才能完成误码率测试。能 否支持更高速率切换、能否支持对噪声敏感的NRZ/PAM4格式切换都是挑战,另外是否支持SSC和FEC解码 挑战更大。为消除环回channel对误码率影响,可以利用外置Redriver及内部自适应均衡配合实现。

图8:PCIe 6.0芯片Rx测试

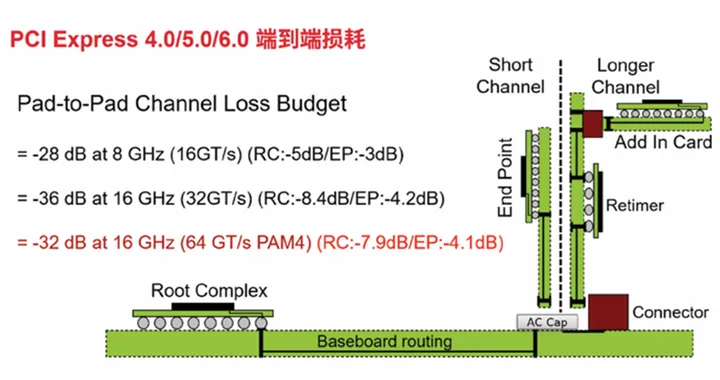

4)互连通道方面端到端链路包括封装、PCB布线、连接器、过孔、耦合电容等,和PCIe 5.0相比有所变化,参考下图,其一体现在端到端IL限制到了-32dB,其二体现在RC 的IL限制到了-7.9dB,EP的IL限制到-4.1dB,链路相关插损仍旧需要使用20GHz网分实现标定。

图9:PCIe 5.0/6.0 端到端损耗比较

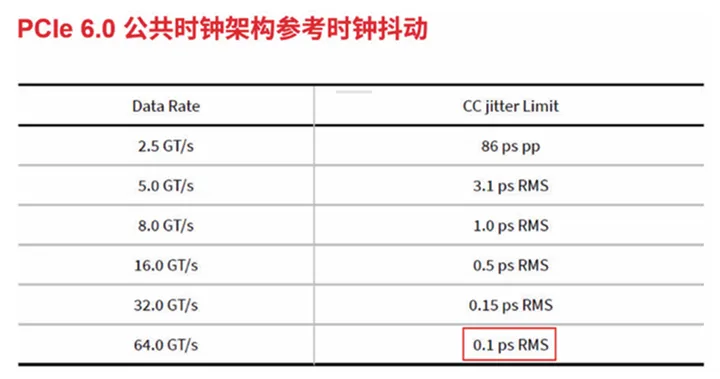

5)参考时钟方面共时钟架构下PCIe 6.0参考时钟抖动在100fs(rms),相比PCIe 5.0参考时钟抖动limit下降了67%,这对测试测量带来挑战,要求仪器固有抖动不能太高。在信道仿真时考虑实际系统噪声影响,抖动limit可放宽至0.15ps(rms)。

图10:参考时钟抖动要求

三、PCIe 6.0 测试方案

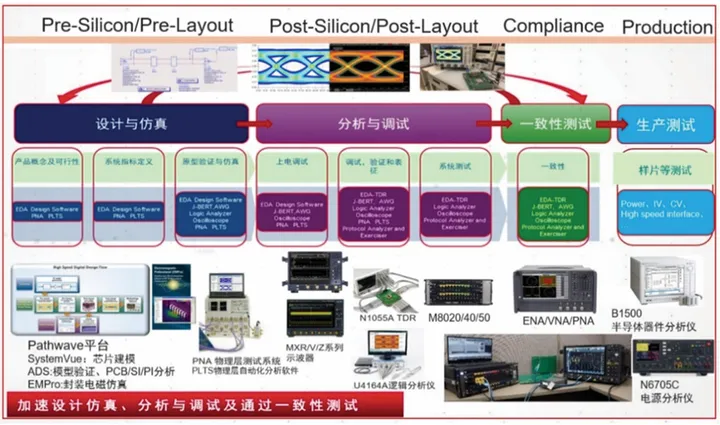

是德科技可以提芯片、板卡和产品的整体测试方案。包括仿真、调试和一致性测试等。

图11:整体测试方案

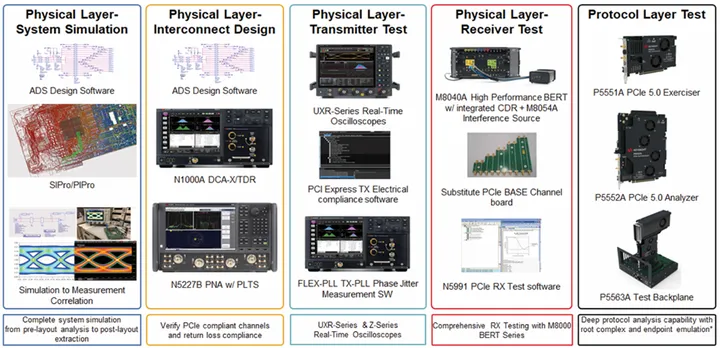

1) 物理层方面

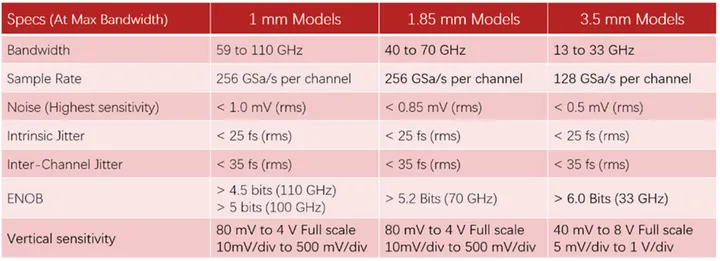

参考PCIe 6.0 Base spec v1.0,要求使用 33GHz 带 宽( Bessel滤波器)进行发送一致性测试, 等效最大平坦度 响应带宽是50GHz,这里推荐UXR0504A示波器。UXR系列示波器集成了InP材料HB2C工艺实现的前置放 大 器( 可达 110GHz)、 10 bit 高性能ADC和硬件加速功能的ASIC芯片,实现了4通带全带宽。通过工艺、芯 片和封装威廉希尔官方网站 使得UXR具备低本底噪声、低固有抖动/通道间抖动和高耐压。它无需外接衰减器就可以实现 PCIe 6.0 serdes 信号高保真度测试。

图12:UXR示波器主要型号和参数

2)协议层方面

芯片回片或板卡回板后完成bring up,除物理电气子层测试还外,还需验证逻辑子层LTSSM链路状态机以及数据 链 路 层 、事 务 层 等 业 务 是 否 正 常 及 合 规 性 ,那 么 还 需 要 借 助 协 议 分 析 仪 或 训 练 器 。当 前 已 经 发 布 了 支 持 PCIe 5.0的P5551A和P5552A的训练器和分析仪产品,支持不同link宽度,该产品集成interposer采集和数据处理功能于一体,无需一堆外部长线缆将信号传给主机处理,保证了信号完整性。分析仪注重协议解析、链路监控及数据过滤等,训练器重点在于interwetten与威廉的赔率体系 对端EP或RC完成数据通信、支持注错和重播等,未来有计划通过升级支持PCIe 6.0、CXL、NVMe等协议。

总之,是德科技可以提供基于ADS仿真、PLTS信号测量、物理层收发、插卡环路带宽分析及协议分析等综合解决方案。

图13:PCIe 6.0 仿真、互连、物理层一致性和协议分析方案

文章来源:是德科技

审核编辑 黄宇

-

AI

+关注

关注

87文章

30746浏览量

268896 -

是德科技

+关注

关注

20文章

875浏览量

81766 -

PCIe5.0

+关注

关注

0文章

17浏览量

1375 -

大模型

+关注

关注

2文章

2425浏览量

2645

发布评论请先 登录

相关推荐

pcie 4.0与pcie 5.0的区别

意法半导体下一代汽车微控制器的战略部署

下一代机器人威廉希尔官方网站 :工业自动化的五大趋势

PCIe 5.0 SerDes 测试

IaaS+on+DPU(IoD)+下一代高性能算力底座威廉希尔官方网站 白皮书

DS320PR410支持PCIe5.0、CXL 2.0的四通道线性转接驱动器数据表

24芯M16插头在下一代威廉希尔官方网站 中的潜力

使用NVIDIA Holoscan for Media构建下一代直播媒体应用

烽火通信在MWC 2024展示基于下一代PON和Wi-Fi7的全光接入网

M31推出PCI-SIG的官方认证PCIe5.0 PHY IP 携手SSD存储芯片公司InnoGrit推进PCIe5.0新世代

下一代PCIe5.0 /6.0威廉希尔官方网站

热潮趋势与测试挑战

下一代PCIe5.0 /6.0威廉希尔官方网站

热潮趋势与测试挑战

评论