AI与EDA的融合在高频高速领域具有重要意义。它可以帮助提高设计的准确性、优化信号完整性、加速故障诊断和修复,以及自动化设计流程,从而提高设计效率和质量。

在本次研讨会中,我们将重点分享AI威廉希尔官方网站 在射频设计、SERDES设计、内存设计以及半导体器件建模中的应用。同时,随着威廉希尔官方网站 的推动,multi-die威廉希尔官方网站 逐渐普及,其中涉及的UCIe接口设计也有一些需要特别关注的地方,我们将为您提供相关解读。

随着人工智能与机器学习的飞速发展,它们已经渗透到了电子设计自动化 (EDA) 的每一个角落。我们将深入探讨如何通过这些尖端威廉希尔官方网站 优化和创新EDA的流程。具体讲解在包括ADS,SystemVue以及器件建模等平台中如何使用AI/ML提高生产力。

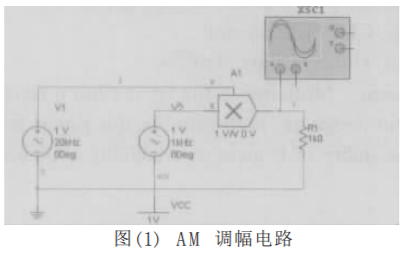

基于AI/ML和测量的功放设计

功放设计通常需要得到实测load pull数据支持,ADS可以引导您完成导入、清理和可视化测得的Load Pull数据,并通过这些数据优化功放设计的关键指标,例如PAE、EVM、ACLR等。通过实际示例,您将学习如何通过Load Pull数据来提高功率放大器的性能,了解如何使用这些数据来定制非线性仿真的人工神经网络(ANN)模型。

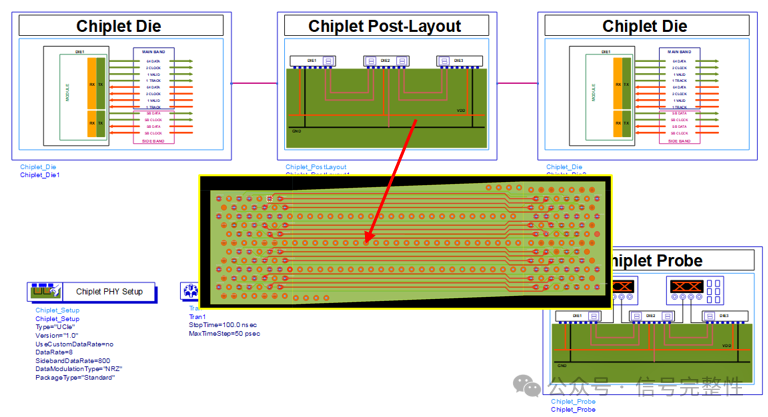

UCIe通用小芯片互连接口威廉希尔官方网站 仿真

高性能计算是Multi-Die系统兴起的重要推动力。利用Multi-Die系统能实现异构集成,并且利用较小Chiplet实现更高良率,更小的外形尺寸和紧凑的封装,降低系统的功耗和成本,不仅可以解决AI领域性能需求每两年增长800倍的需求,还可以解决多个行业对速度更快、功耗更低带宽更高的半导体的巨大需求。Die之间使用UCIe标准进行通信,在本次演示中,您将深入了解chiplet的高速通信标准以及如何进行仿真,此外,我们还将探讨如何利用智能设计环境轻松计算和优化眼图、误码率(BER)、等高线和电压传输函数(VTF)等。

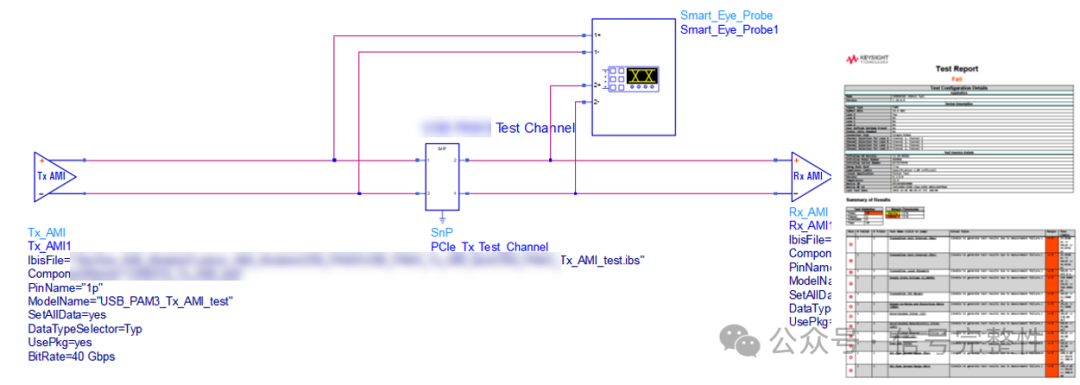

全新的SerDes和内存设计流程

AI/ML、5G 和物联网设备的飞速发展不断推动对内存威廉希尔官方网站 的迭代。更高的存取速度使得内存设计和验证变得更加困难。内存接口信号完整性可能会受到串扰、反射和噪声的影响。时间预算变得更加紧张,误差边界变窄。而功耗上升,则可能引起影响可靠性的热问题。在这个演示中,您将了解到针对 SerDes 和内存设计的最新工作流解决方案,从而帮助您缩短从概念到interwetten与威廉的赔率体系 和验证的时间。

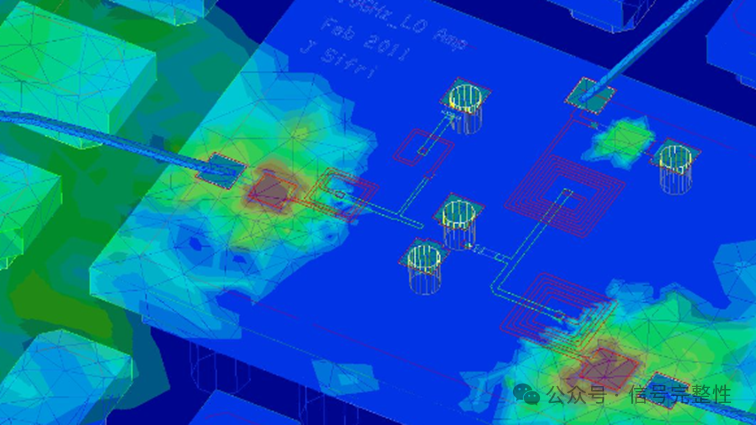

快速电磁-电路协同设计

射频工程师使用PCB板和模块来以比定制集成电路设计更低的成本实现系统功能。随着威廉希尔官方网站 的进步,模块内的芯片、封装和三维组件拥有更复杂的工艺和威廉希尔官方网站 。这使得电路电磁协同设计更加困难,我们将介绍一种新的方法来应对这些挑战,以帮助射频工程师在几秒钟或几分钟内进行模块集成。

审核编辑:黄飞

-

AI

+关注

关注

87文章

30818浏览量

268969 -

人工智能

+关注

关注

1791文章

47239浏览量

238353 -

高速电路

+关注

关注

8文章

158浏览量

24243 -

机器学习

+关注

关注

66文章

8414浏览量

132601 -

UCIe

+关注

关注

0文章

46浏览量

1632

原文标题:[北京|西安]AI如何加速高频高速电路仿真设计

文章出处:【微信号:SI_PI_EMC,微信公众号:信号完整性】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

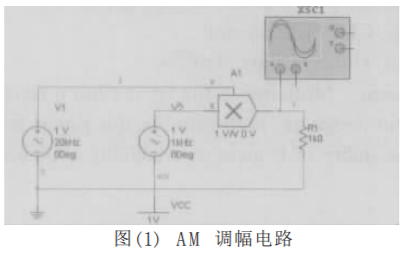

基于NI Multisim 10. 0的高频电路仿真与分析

经典威廉希尔官方网站 指南合集:电路仿真和PCB设计

【下载】ADI 威廉希尔官方网站 指南合集-电路仿真和PCB设计

电容式高频振荡电路仿真失败。。。场管

PSPICE在高频电路仿真分析中的应用

Multisim使用教程之基于Multisim 8的高频电路仿真研究

Multisim使用教程之基于Multisim 8的高频电路仿真研究

AI威廉希尔官方网站

助力北京与西安:高频高速电路仿真设计的新速度

AI威廉希尔官方网站

助力北京与西安:高频高速电路仿真设计的新速度

评论