几乎所有电子设备的制造过程都使用焊料,通过焊料将电子元器件与PCB连接起来。在以前,通常选用的都是有焊料,但是目前,最受欢迎的应该是无铅焊料。

这里就介绍一下:PCB 设计中的串扰以及如何减少 PCB 设计中的串扰。

一、串扰是什么意思?

串扰是 PCB 的走线之间产生的不需要的噪声(电磁耦合)。

串扰是 PCB 可能遇到的最隐蔽和最难解决的问题之一。最难搞的是,串扰一般都会发生在项目的最后阶段,而且通常以断断续续或不易重现的方式发生,对于工程师来说,尽早解决 PCB 上串扰发生的所有原因非常重要。

串扰会对时钟信号、周期和控制信号、数据传输线和 I/O 产生不良影响。通常来讲,串扰是无法完全消除的,只能尽量减少串扰。

二、串扰的机制

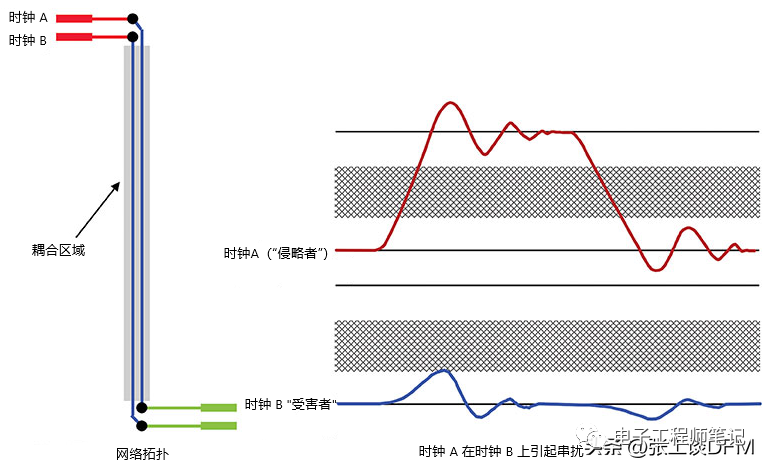

01 耦合

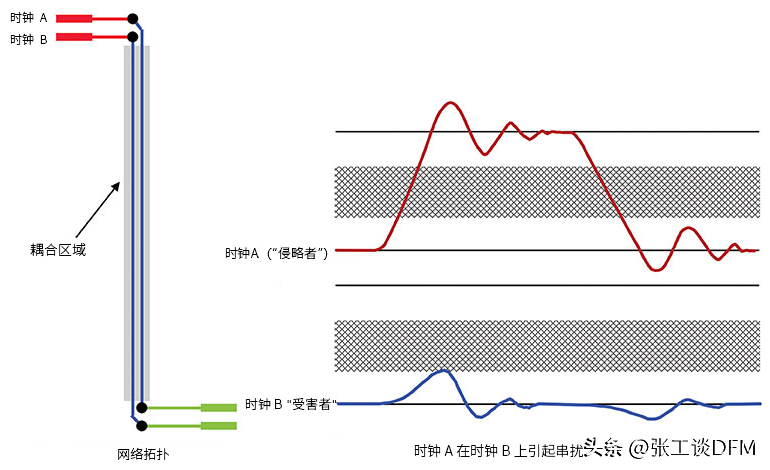

影响一条走线的过大电压或电流会对另一条走线产生不良影响,但是这两条走线之间没有物理接触,每当两个网络彼此相邻运行任何显著长度时,都可能出现这种耦合。当信号在其中一条线上驱动时,它产生的电场和磁场会导致意外信号也出现在附近的线上,如下图所示:

当两条或更多条相邻迹线耦合在一起时会发生串扰

02 电容耦合

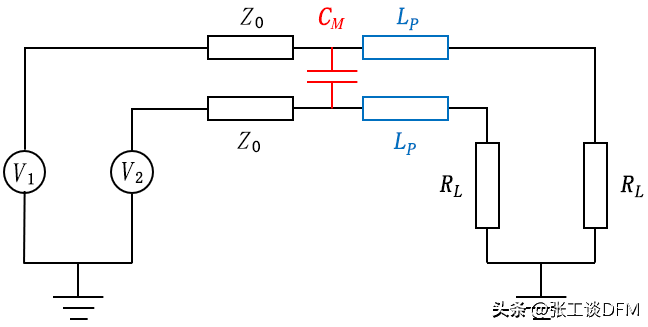

下面的电路图显示了如何使用电路理论来interwetten与威廉的赔率体系 不同类型的串扰。在该图中,两条迹线之间存在一些寄生电容,这是由于迹线之间的宽边耦合而存在的。因为每条迹线都是一个导体环路,所以每条迹线就像一个电感器并具有一些寄生电感。两个并联电感具有一定的互感,它定义了两条走线之间的电感耦合强度。

电路图显示了描述 PCB 中不同类型串扰的经典电路模型

电容耦合不仅仅意味着显示由走线边缘产生的等效电容,尽管这确实有助于互电容。每条迹线的本机电容和宽边电容相结合得出总互电容;它们全部串联并耦合回地平面。

当串扰发生并被观察为时域中的快照时,很难区分电容和电感对串扰的贡献。

03 “攻击者”信号或走线切换

串扰是一种特别难以预测和控制的现象,除非它是模拟的,因为几乎没有办法直观地知道由于给定的耦合会产生多少串扰电压和电流。

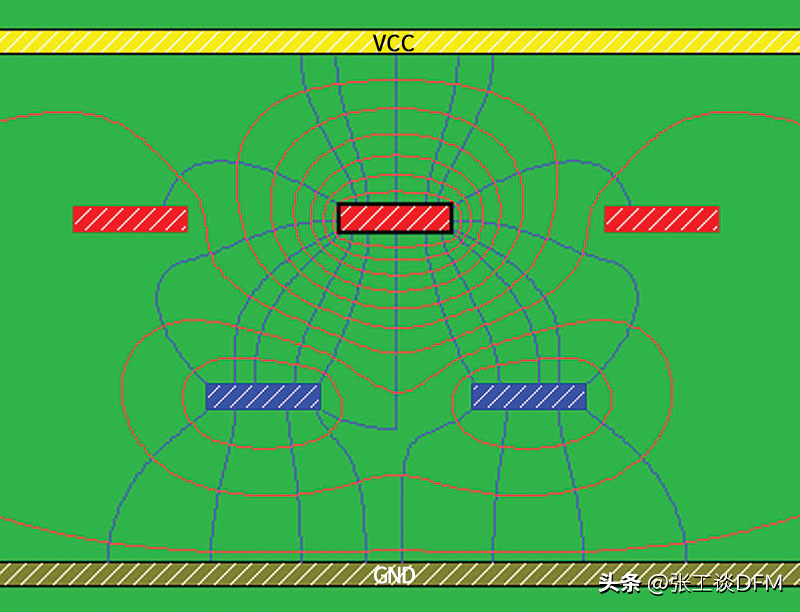

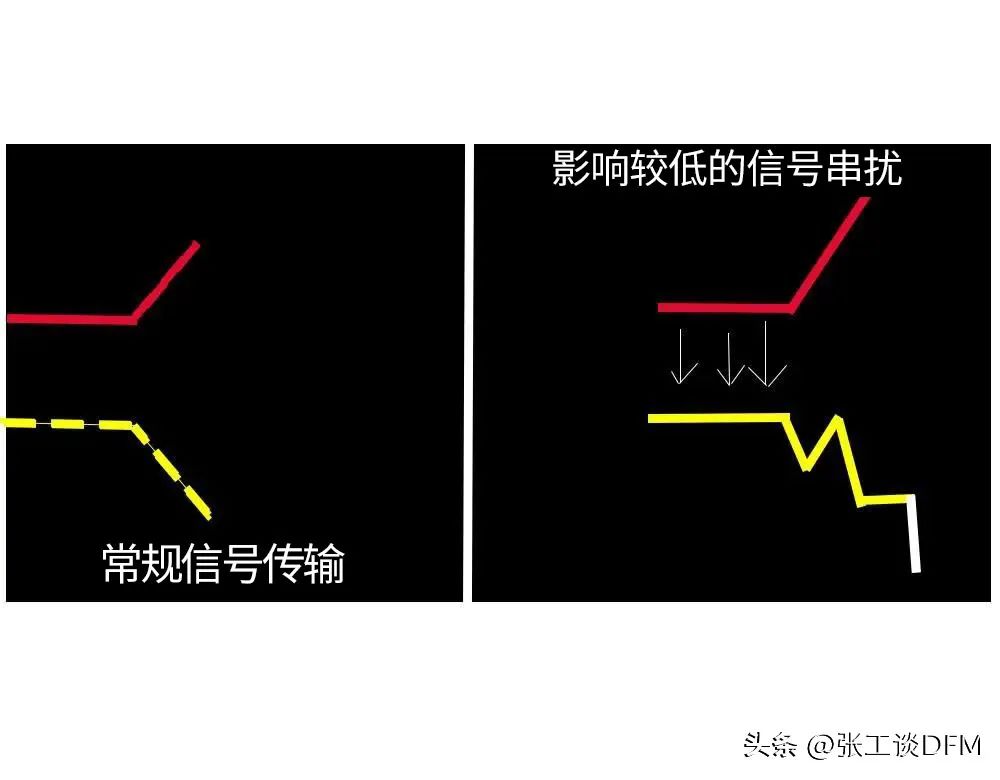

用串扰的说法,“攻击者”信号或迹线切换并导致串扰。“受害者”信号或轨迹通过产生一个意外信号来做出响应。效果本质上是三维的。受害者可以在同一层相邻,也可以在攻击者的上方或下方(下图)。

受害者网络可以位于攻击者网络的上方、下方或附近

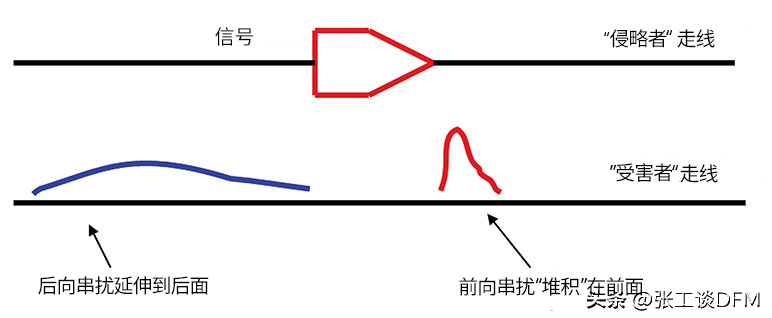

04 前向和后向串扰

实际上,有两个耦合信号加在受害网络上:一个前向信号和一个后向信号。“前向”脉冲与干扰信号一起传播,而“后向”脉冲从干扰信号返回。受害远端的串扰称为“远端串扰”或 FEXT,近端的耦合电压称为“近端串扰”(NEXT)。下图显示了前向和后向串扰。

受害迹线上的前向和后向串扰示意图

三、串扰的原因

01 电容和电感耦合

电容耦合是由于寄生电容,而电感耦合是由于互感。

02 传播速度差异

传播速度的差异,可能串扰

03 PCB 过孔

带有短截线的 PCB 过孔会产生反射,从而产生振铃,从而产生串扰。

04 增加的数据速率

随着数据速率的增加,上升时间也会增加。根据法拉第定律,随着上升时间的增加,串扰也会增加。

05 板尺寸

随着 PCB 板尺寸的增加,走线长度也会增加,这些走线就像天线一样。

四、减少PCB设计中串扰的技巧

01 检查靠近 I/O 网络的关键网络

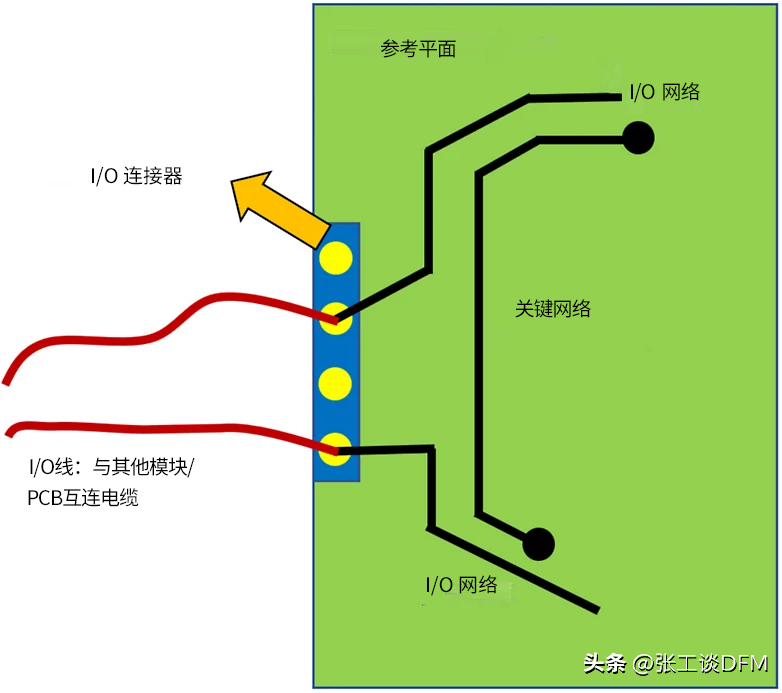

查看与 I/O 线相关的关键网络的布线非常重要,因为噪声很容易通过这些 I/O 线离开或进入电路板(如下图)并将 PCB 连接到电路板上或电路板外耦合。外部世界与系统中的其他 PCB 或模块。

关键网络和I/O 网络彼此靠近布线的场景示意图

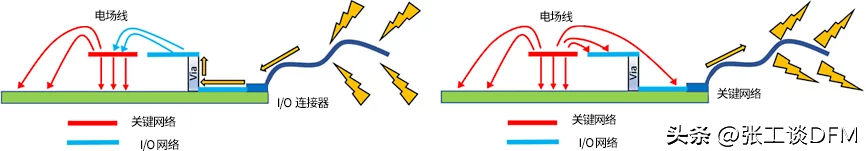

通过 I/O 线进入电路板的任何噪声都有可能耦合到承载重要数据/时钟信号的关键网络,这基本上是 PCB 的抗扰性方面(下图左)。以类似的方式,任何由关键网络传输的高速信号都可以耦合到 I/O 网络,最终通过从板上出来的 I/O 线到达外部世界并进入其他模块在系统中。原则上,这将是 PCB 的排放方面(下图右)。

关键网络和 I/O 网络接近导致的潜在 EMI/EMC 问题

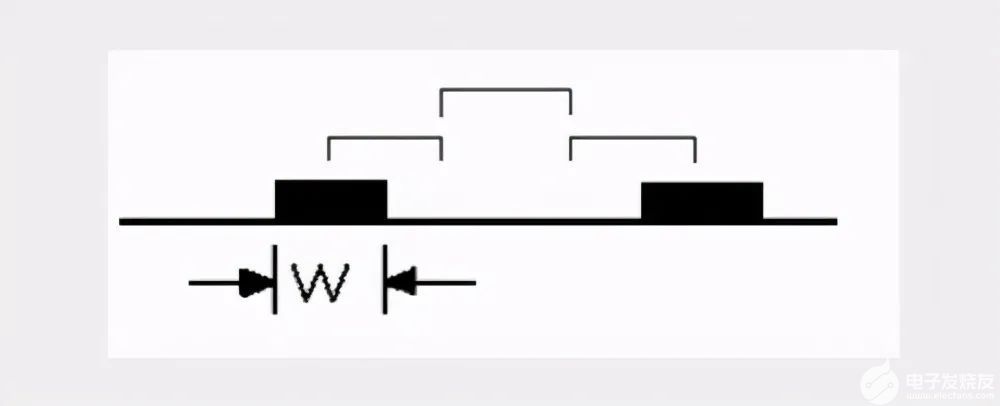

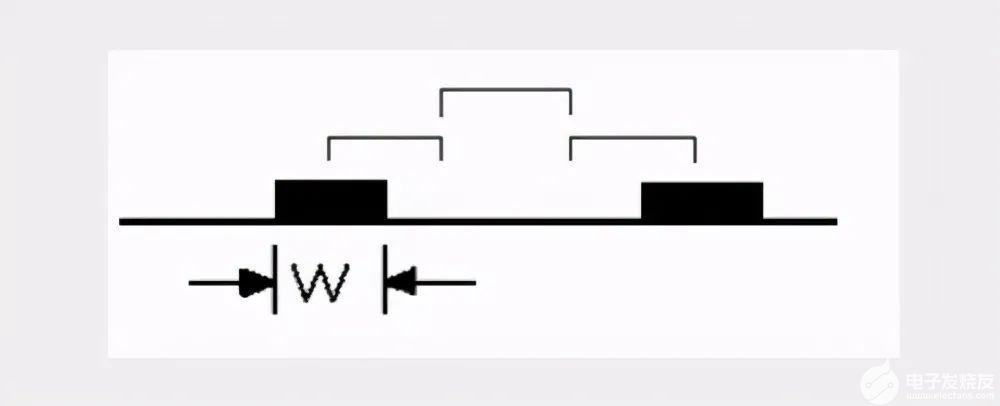

02 走线间的最小宽度

在定义 PCB 布局时,可以在使用的 CAD 工具中设置一些规则,例如两条走线之间的最小距离以及每条走线与板上存在的组件之间的最小距离。还可以设置与特定网表或网表将在其中布线的区域相关的不同距离值。

PCB 设计软件应用程序通常包含可以指定差分信号对的宽度和距离的功能,或者可以在哪些 PCB 层上布线网表以及走线可以采用的首选方向。

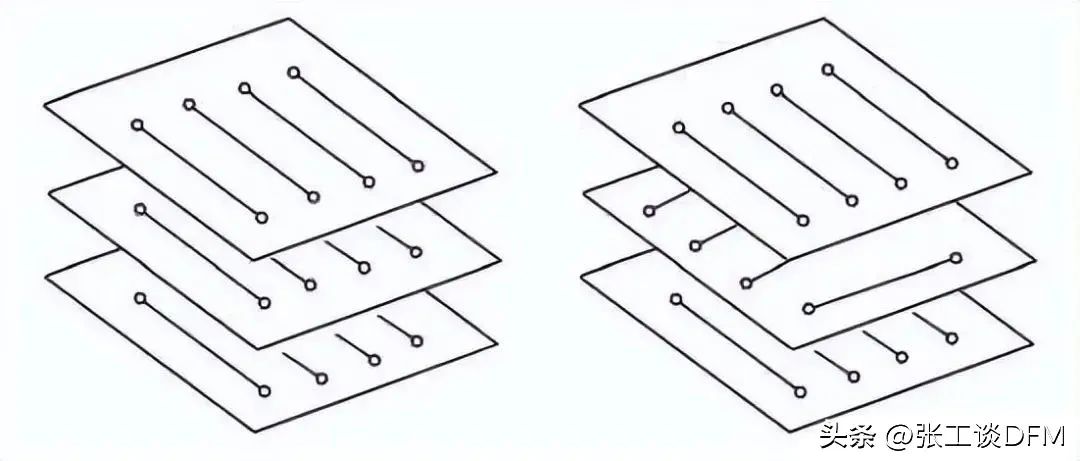

03 保持相邻层的走线垂直

PCB 层的配置应使穿过相邻层的信号具有相互垂直的方向,绝对避免它们的走线平行。也有人说,如果一层走线是“从北到南”,那么在它旁边的一层走线应该是“从东到西”。这个简单的预防措施可以让你将宽边耦合的影响降至最低。

具体如下图所示:左侧是要避免的布局,右侧是要应用的布局。

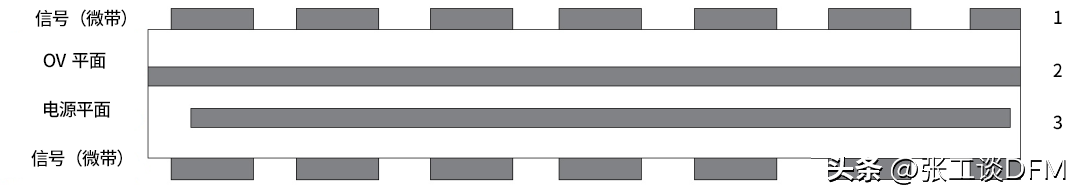

04 使用接地层

在两个相邻的信号层之间,最好插入一个接地层(或者,一个电源层),这样做进一步降低了发生宽边耦合的可能性。

该解决方案具有双重优势,即增加了层之间的距离,并为信号层提供了更好的接地返回路径。在下图,我们可以看到一个经典的四层 PCB,分为两个信号层(外部),一个用于接地层(0V)的内部层和一个用于电源的内部层。

多层 PCB 示例

05 利用接地返回路径

虽然这和前面说的有点矛盾,但是可用于减少串扰的替代威廉希尔官方网站 恰恰在于利用走线之间存在的并行性,将接地返回路径与高频信号耦合。

事实上,由于接地返回路径相对于信号具有相同的幅度但方向相反,因此可以消除影响,从而减少串扰。

06 使用差分信号

另一种保证信号完整性、最小化串扰产生的影响的方法是使用差分信号,即两条幅度相同但极性相反的信号线形成一个单一的高速信号。由于在接收时,信号是作为两条信号线的电压之差获得的,并且由于电磁噪声对两条线的影响相同。

因此即使存在明显的外部噪声,信号也能保持高度的完整性。建议是在差分信号对和其他 PCB 走线之间保持尽可能大的距离。经验法则是选择至少是轨道宽度三倍的距离。

07 减小平行走线的宽度

在所有无法避免走线之间平行的情况下,都需要保证它们的宽度尽可能的短,从而减少耦合程度。

带走线的 PCB

08 将高频信号与其他走线隔离

高频信号(例如时钟)必须尽可能远离承载其他信号的走线。即使在这种情况下,也可以应用经验法则,选择最小距离等于走线宽度的三倍。

串扰影响信号传输

09 尽可能缩短暴露的关键跟踪长度

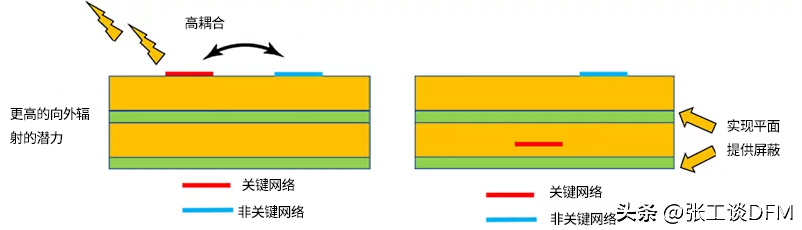

在波长较短的高速 PCB (> 100MHz) 上,任何关键网络(参见下图左)的电气长度都足以使其成为高效的辐射器,尤其是当暴露在顶层或底层时,这种不需要的辐射可以耦合到任何相邻的迹线,甚至耦合到靠近迹线的组件中存在的电缆。

建议将关键网络埋在 PCB 内层的实心平面之间,如下图右 所示。这有助于控制走线中的场,并避免串扰或 EMI 形式的任何无意耦合。如果暴露关键网络是不可避免的,请尽可能缩短暴露部分的长度。这是因为裸露迹线的较短长度将具有较小的辐射趋势,因为如果它们的电气尺寸很小,它们将是低效的天线。

在实心平面之间暴露或掩埋关键网络的图示

10 隔离异步信号

异步信号,如复位或中断线,应使用尽可能远离高频信号的走线。异步信号经常被放置在靠近电源线或控制开关的信号附近,因为这些信号仅用于电路操作的某些阶段而不是连续使用。

11 背钻过孔

过孔短截线会降低信号完整性,因此会增加串扰,这可以通过实施背钻来减少。

12 选择差分对布线

紧密耦合的差分布线消除了串扰,因为来自干扰源的噪声均等地耦合到差分对的两个分支中,从而产生共模噪声。差分对抑制有助于减少串扰的共模噪声。

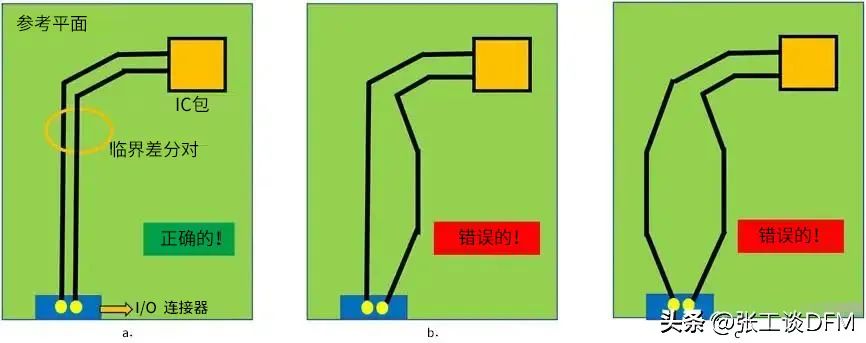

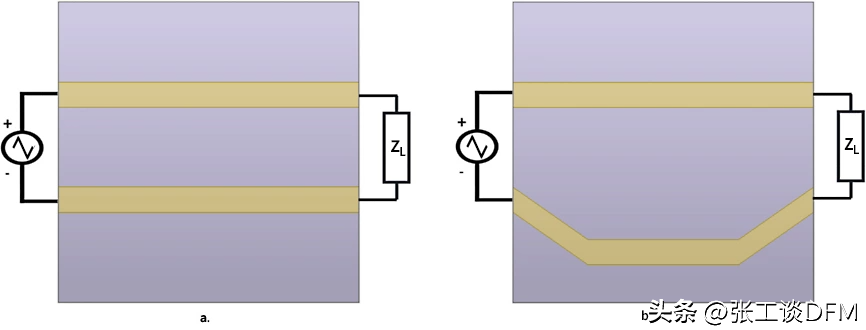

理论上,差分对承载大小相等但极性相反的信号,因为该信号产生的 EMI 可以抵消或可以忽略不计。但是,这仅在线对中的走线长度相等并且尽可能对称地彼此靠近时才有效。

违反其中任何一项都会产生共模噪声和 EMI 问题,尤其是对于承载高频关键信号的差分网络,因为 EMI 会增加所承载信号的频率。

下图显示了在 IC 封装和电路板上的出口点(连接器)之间路由关键差分对的正确/错误方法的几个示例。

参考平面存在分裂时的返回电流路径

关键差分网络匹配:模拟和与实际测试要求的关系

在下图 PCB 示例中,这里有一个简单的差分对在 PCB 上以两种不同方式布线的情况:分别是对称的和不对称的。在这两种情况下,它们的一端由差分电压源激励,另一端由负载端接。

在 PCB 上布线的差分对示例

13 使用保护走线

保护走线用于控制传输线之间的电容串扰。但是需要谨慎使用,因为使用保护走线会影响。

审核编辑:刘清

-

PCB设计

+关注

关注

394文章

4680浏览量

85456 -

寄生电感

+关注

关注

1文章

155浏览量

14595 -

电磁场

+关注

关注

0文章

791浏览量

47255 -

时钟信号

+关注

关注

4文章

448浏览量

28537 -

PCB走线

+关注

关注

3文章

133浏览量

13910

原文标题:从细节入手,减少PCB设计中的串扰,轻松化解“干扰”危机!

文章出处:【微信号:gh_454737165c13,微信公众号:Torex产品资讯】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

PCB设计中的串扰是什么意思?如何减少PCB设计中的串扰呢?

PCB设计中的串扰是什么意思?如何减少PCB设计中的串扰呢?

评论