锁相环路锁定状态应满足什么条件

锁相环(PLL)在锁定状态时应满足以下条件:

1. 相位同步:锁定状态下,输出信号的相位应与参考信号的相位保持固定的相对关系。这意味着输出信号的相位与输入信号的相位之间存在稳定的相移。

2. 频率同步:锁定状态下,输出信号的频率应与参考信号的频率相等或非常接近。这意味着输出信号的频率应与参考信号的频率保持稳定的比例关系。

3. 稳定性:锁定状态下,PLL应能够保持较高的频率和相位稳定性。即使在存在噪声、干扰或其他外部变化的情况下,输出信号的频率和相位也应保持相对稳定。

4. 误差最小化:锁定状态下,PLL应尽量最小化输出信号与参考信号之间的相位差或频率偏差。通过精确调整PLL参数和输入信号,可以尽可能地减小误差。

通常需要合适的PLL设计和参数设置。例如,选择合适的参考信号频率、合理设置环路滤波器带宽和参数、调整环路稳定器的增益和阻尼系数等。

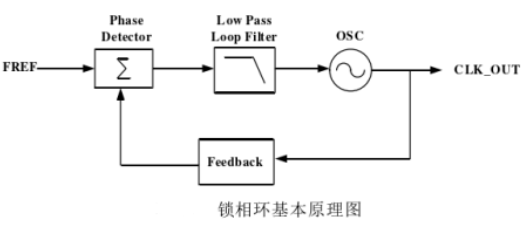

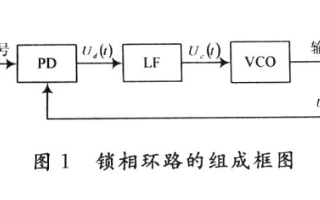

锁相环是一个典型的负反馈系统。振荡器Q负责产生振荡时钟信号,振荡器的输出时钟信号被反馈环路采样后与输入参考时钟信号经由相位检测器进行比较,生成相位误差信号,经过滤波器滤波后,反馈给振荡器对输出时钟信号的频率进行调节。

低通滤波器主要是对相位误差信号的高频噪声分量进行滤波,除去杂散信号。相位检测器对输出时钟信号与输入参考时钟信号的频率和相位进行比较生成相位误差信号。

锁相环的类型有哪些

锁相环(PLL)有多种类型,适用于不同的应用场景。以下是一些常见的锁相环类型:

1. 基本锁相环(Basic PLL):基本锁相环通常由锁相检测器(Phase Detector)、低通滤波器(Loop Filter)和令牌圈振荡器(VCO)组成。它是最简单的锁相环形式,用于频率和相位同步。

2. 延迟锁相环(Delay-Locked Loop,DLL):延迟锁相环主要用于对齐信号之间的时间延迟。它通过控制延迟线的长度来调整信号的相对延迟。常用于高速通信和数据存储系统。

3. 频率锁定环(Frequency-Locked Loop,FLL):频率锁定环用于频率同步,其相位追踪能力较弱。它可以通过调整VCO的频率来跟踪输入信号的频率变化。

4. 相频锁定环(Phase-Frequency Locked Loop,PFL):相频锁定环是频率锁定环和相位锁定环的组合形式,可以同时实现频率和相位同步。它在通信系统和时钟同步中广泛应用。

5. 多路复用锁定环(Multiphase Locked Loop,MPLL):多路复用锁定环是一种特殊的PLL,用于信号的多路复用和解复用。它将多个输入信号分配到不同的相位状态,实现信号的并行处理。

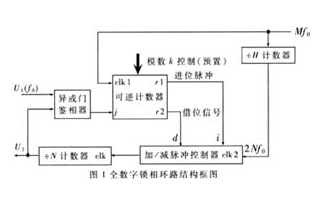

6. 数字锁相环(Digital PLL,DPLL):数字锁相环使用数字化的信号处理威廉希尔官方网站 ,可以实现高精度的频率和相位同步,并具有较强的抗干扰能力。它在通信、数字信号处理和时钟恢复等领域得到广泛应用。

审核编辑:黄飞

-

锁相环

+关注

关注

35文章

584浏览量

87749 -

低通滤波器

+关注

关注

14文章

474浏览量

47397 -

pll

+关注

关注

6文章

776浏览量

135144 -

稳定器

+关注

关注

0文章

54浏览量

13586

发布评论请先 登录

相关推荐

高频锁相环路LMX2430电子资料

锁相环路是什么?有何特点

用锁相环路实现任意频率变换威廉希尔官方网站

基于FPGA的全数字锁相环路的设计

锁相环路跟踪特性的测量方法

采用Spartan2系列FPGA器件实现全数字锁相环路的设计和仿真验证

锁相环路的组成、的基本特性和应用分析

锁相环路的工作原理

锁相环路锁定状态的条件及类型

锁相环路锁定状态的条件及类型

评论