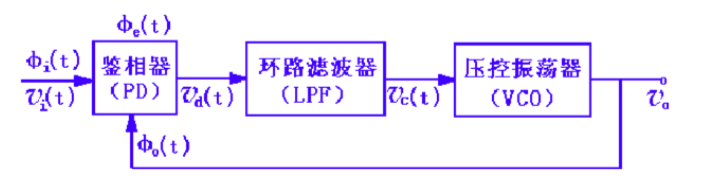

所谓锁相环路,实际是指自动相位控制电路〔APC) ,它是利用两个电信号的相位误差,通过环路自身调整作用,实现频率准确跟踪的系统,称该系统为锁相环路,简称环路,通常用PLL表示。

锁相环路是由鉴相器《简称PD》、还路滤波器〔(简称LPF或LE和压控振荡器(简称VCO〕三个部件组成闭合系统。这是一个基本环路,其各种形式均由它变化而来。

锁相环锁定时间取决于哪些因素

锁相环(PLL)锁定时间取决于多个因素。以下是一些主要因素:

1. 参考信号频率稳定度:参考信号的频率稳定度越高,PLL锁定时间就越短。如果参考信号频率出现较大的漂移或噪声,PLL需要更长的时间来稳定。

2. 目标频率与参考频率之间的差异:如果目标频率与参考频率之间的差异较小,PLL可以更快地锁定。当两者之间的差异较大时,PLL需要更长的时间来捕捉到目标频率。

3. 系统的带宽:PLL的带宽决定了系统对频率变化的响应速度。较高的带宽可以加快锁定时间,但可能会引入噪声和干扰。

4. 系统的阻尼系数:阻尼系数是衡量PLL响应速度和稳定性之间的折中因素。较高的阻尼系数可以增加稳定性,但可能会减慢锁定时间。

5. 可用的控制电压或电流:PLL中的控制电压或电流的范围和精度也会影响锁定时间。更大的控制范围可以更快地调整频率,更高的控制精度可以提供更好的锁定性能。

锁相环锁定状态和失锁状态的特点是什么

锁相环(PLL)有两种主要状态:锁定状态和失锁状态。它们具有不同的特点:

1. 锁定状态:

- 频率同步:当PLL处于锁定状态时,输出信号的频率与参考信号的频率是相等的,即它们保持同步。

- 相位同步:锁定状态还意味着输出信号相位与参考信号相位具有固定的相对关系。

- 滤波效应:在锁定状态下,PLL的滤波器将对输入信号进行滤波,以减小噪声和干扰的影响。

- 稳定性:一旦PLL锁定,它能够保持较高的频率和相位稳定性。

2. 失锁状态:

- 频率偏差:失锁状态下,输出信号的频率与参考信号的频率之间存在偏差,即它们不再同步。

- 相位偏差:失锁状态下,输出信号的相位与参考信号的相位之间存在不确定的相对关系。

- 不稳定性:失锁状态下,输出信号的频率和相位可能会受到噪声、干扰和其他外部因素的影响,从而产生不稳定的变化。

失锁状态通常是由于以下情况之一引起的:

- 环路滤波器参数不正确或环路带宽设置不合适。

- 参考信号频率发生了较大的漂移或噪声。

- 环路中的噪声或干扰过大,超过了PLL的稳定范围。

- PLL输入信号存在较大的干扰或失真。

特定PLL系统的锁定状态和失锁状态可能会有一些变化。在实际应用中,根据要求进行调整和优化以实现所需的性能和稳定性。

审核编辑:黄飞

-

锁相环

+关注

关注

35文章

584浏览量

87749 -

滤波器

+关注

关注

161文章

7802浏览量

178054 -

pll

+关注

关注

6文章

776浏览量

135144 -

压控振荡器

+关注

关注

10文章

133浏览量

29291 -

控制电压

+关注

关注

0文章

35浏览量

16075

发布评论请先 登录

相关推荐

电荷泵锁相环电路锁定检测的基本原理,影响锁相环数字锁定电路的关键因子是什么?

高频锁相环的可测性设计,不看肯定后悔

一种实现快速锁定的锁相环的研究

锁相环验证通行及锁定的建立

详解FPGA数字锁相环平台

利用开关的控制加速锁相环锁定的设计方法

锁相环锁定时间取决于哪些因素

锁相环锁定时间取决于哪些因素

评论