在模块划分时,我们通常会考虑解耦合,即尽量减少模块间的交互,让模块间的接口尽量简单。

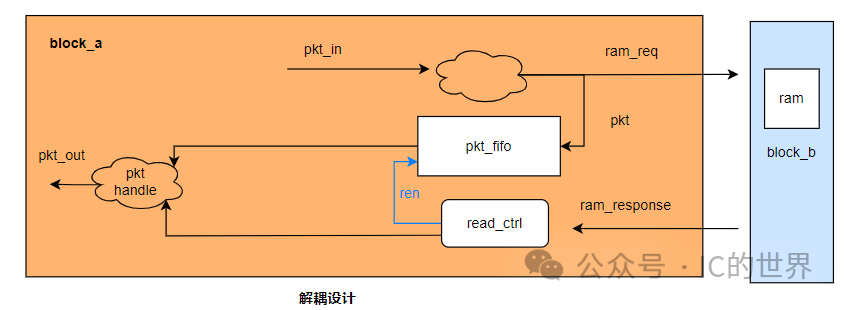

在包处理过程中,因为数据处理的需求,需要读取某些信息(配置信息,状态信息),如图中读取block_b中的ram,根据读返回的结果后对数据包进行处理。为了解耦合,我们可以采用一个fifo(pkt_fifo)存储与ram请求(ram_req)无关的信息(数据包以及数据包的相关描述信息),等待response返回后,再从pkt_fifo读取相应的数据包信息对,从而对数据包进行处理。

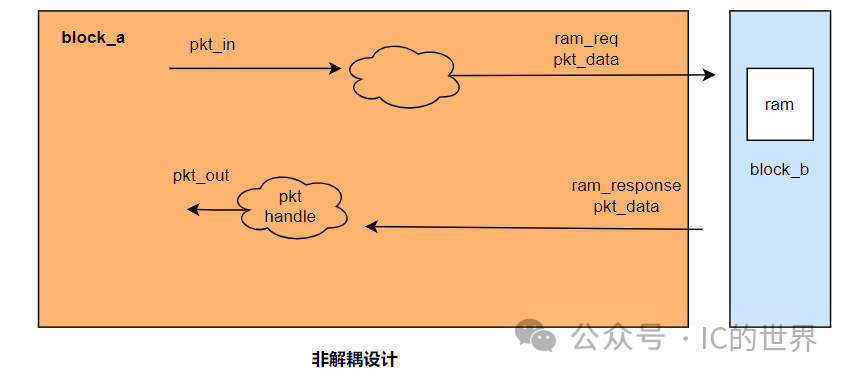

如果不采用pkt_fifo存储包信息,那么会怎么设计呢?如非解耦设计图所示,不需要额外的fifo,将包信息(pkt_data)与访问请求(ram_req)一同传递给block_b模块,再由block_b将包信息(pkt_data)和访问响应(ram_response)一同送到block_a模块。

案例中的解耦合设计还有一个优点:节约资源和功耗。如果从发起ram_req到返回ram_reponse的流水比较长,例如需要几十甚至上百个时钟周期,在非解耦设计中,就需要使用寄存器对pkt_data进行打拍,而解耦设计中采用fifo存储pkt_data,虽然从存储bit角度计算两种设计需要的bit位几乎相同,但是fifo(用ram实现)面积更小,功耗更低。

-

接口

+关注

关注

33文章

8580浏览量

151030 -

IC设计

+关注

关注

38文章

1295浏览量

103921 -

RAM

+关注

关注

8文章

1368浏览量

114650 -

解耦

+关注

关注

0文章

40浏览量

11895

原文标题:IC设计:ram的应用-一种常见的解耦设计

文章出处:【微信号:处芯积律,微信公众号:处芯积律】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

永磁同步电机偏差解耦和电流前馈解耦控制比较

常用的解耦设计方法

一种基于PID神经网络的解耦控制方法的研究

一种新的PI调节器在交流解耦控制系统中的应用

基于补偿器的解耦控制方法的研究

电容解耦如何放置

永磁同步电机控制之反馈解耦及复矢量解耦

一种常见的解耦设计

一种常见的解耦设计

评论