1. 简介

在高速并行接口(例如DDR接口)中,由于工作环境的变化,可能会导致Data bus与时钟信号之间的skew相差比较大,从而使得本来就小的采样窗口变得更加紧张,严重的话会导致采样失败。在这种情况下,一个可以调节skew的玩意是十分有必要的。而由于interwetten与威廉的赔率体系 DLL个头比较大,容易增大面积,从而加大成本。所以领导可能会要求你去用数字逻辑搭一个delayline,用于把输入信号延迟输出,且延迟的时间在总量程范围内可调节。

本文提出一种delay_line的设计方案,希望读者能够带着以下问题去进行阅读:

如何减小delay_line档位之间的误差?

如何使得每一档之间的delay呈线性关系?

如何优化delay_line的动态功耗?

如何减小delay_line对输出clk的占空比的影响?

如何减小default值(档位为0时的延时)?

2. 方案描述

2.1. 档位说明

本方案中,delay_line的档位分为两类:fine_dly(高精度档)和coarse_dly(大幅值档)。

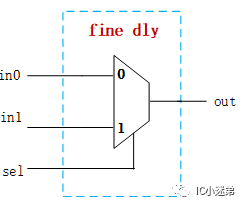

2.1.1. fine_dly档

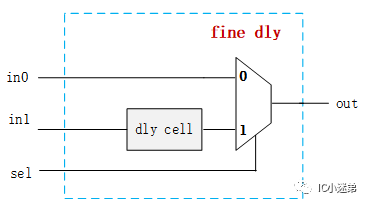

fine_dly的延时决定了delay_line的最小调节步长,需要根据实际所使用的工艺节点来选择dly cell,可以是CLK-BUF、CLK-INV pairs、CLK-MUX以及专门的DLYCELL。记CLK-MUX的delay为T_mux,dly cell的delay为T_dcell,则有:

为便于下文书写简化,记 T_fine(sel=0) = T_f(0), T_fine(sel=1) = T_f(1).

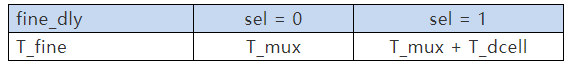

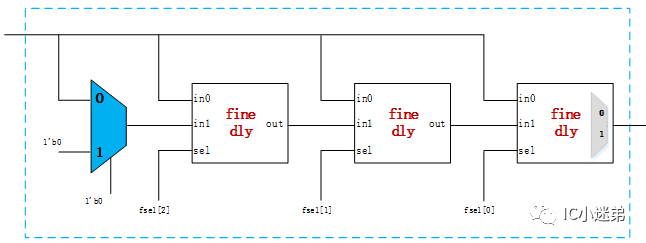

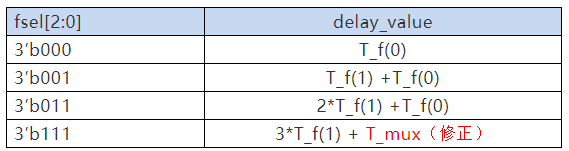

在delay_line的fine_dly链部分,需要增加一个CLK-MUX来修正delay_value,如下图中所示标蓝色的CLK-MUX。

上图的delay_value与档位的对应关系如下:

本方案建议fine_dly仅使用一级CLK-MUX即可,见下图。

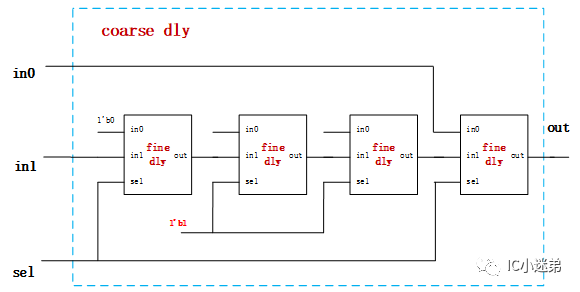

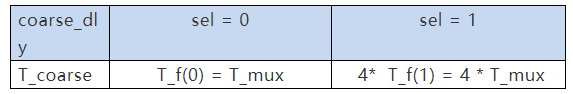

2.1.2. coarse_dly档

coarse_dly与fine_dly二者延时的关系决定了delay_line各档位间的误差,因此coarse_dly需要用fine_dly级联来实现,以减小该误差。记CLK-MUX的delay为T_mux,则有:

为便于下文书写简化,记 T_coarse(sel=0) = T_c(0), T_coarse(sel=1) = T_c(1).

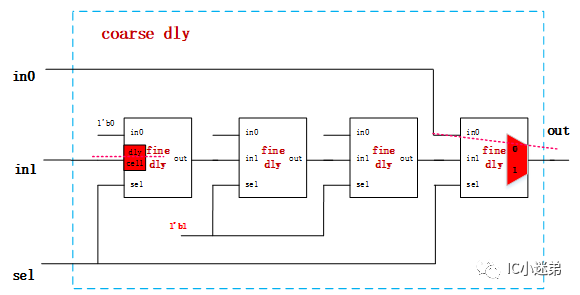

2.2. 动态功耗优化

由于clk在高速翻转,对于delay_line中未被选中的档位,需要把输入固定成高电平或低电平,以减小动态功耗。本方案仅考虑对coarse_dly档做功耗优化,fine_dly档本身要实现小delay_value,std_cell数量较少,暂不做优化处理。

如下图电路中,当 sel = 0 时,只有标红色的两部分有clk输入,其它std_cell的输入都是固定电平,动态功耗(指switch power)可降到最低。

2.3. 占空比优化

由于std_cell的上升时间和下降时间存在差别(CMOS器件特性,本文不做解释),因此clk在经过std_cell之后,占空比会被改变,且经过的std_cell越多(延时越大),占空比的改变会越明显。

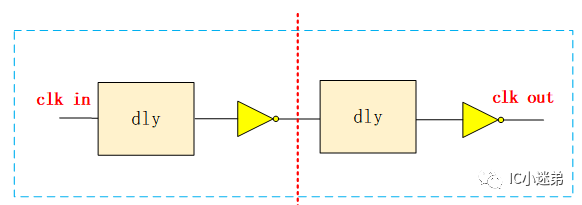

考虑下图所示电路结构,clk在经过Part_A之后会被取反,再经过Part_B之后会被还原,因为Part_A与Part_B两部分电路完全对称,所以Part_B电路会对Part_A电路的信号传播时间做补偿,理论上可以把上升时间和下降时间对占空比的影响降到很低。

2.4. 方案原理图

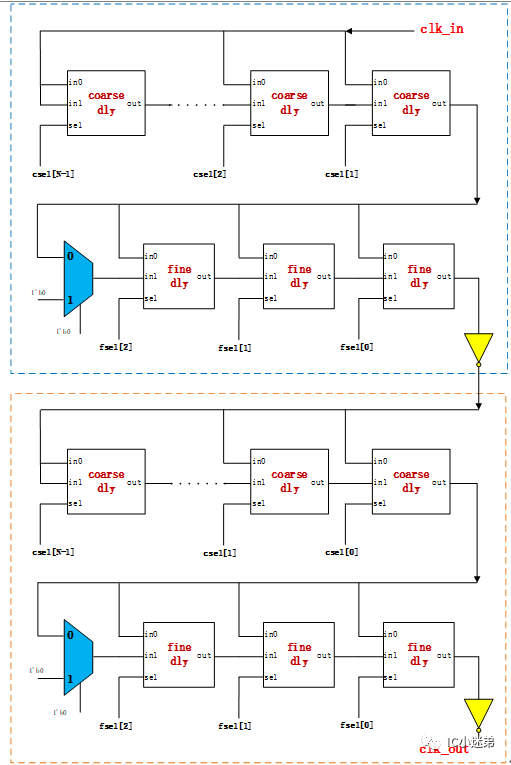

综合2.1~2.3小节的描述,本文给出一种delay_line原理图如下:

记CLK-INV的delay为T_inv,则delay_value(T_dly)的计算公式如下:

T_dly = 2( CT_c(1) + F * T_f(1) ) + T_default ;

其中:

T_default = 2 * ( T_c(0) + T_f(0) + T_inv ) ;

“C”表示选中coarse_dly的档位数,取值为0,1,2,3….N (N取决于使用者);

“F”表示选中coarse_dly的档位数,取值为0,1,2,3;

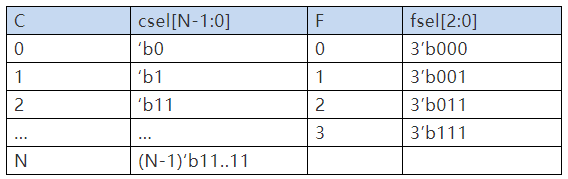

“C”、”F”对应的csel、fsel的转换关系如下表:

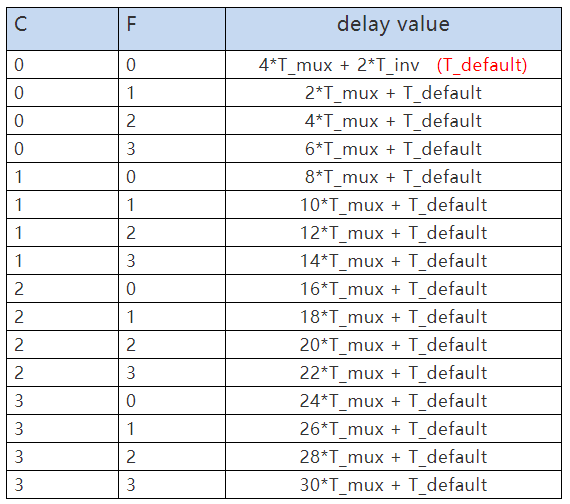

以N=3举例,每个档位对应的delay value关系表如下:

-

接口

+关注

关注

33文章

8588浏览量

151103 -

DDR

+关注

关注

11文章

712浏览量

65326 -

时钟信号

+关注

关注

4文章

448浏览量

28559

原文标题:2. 方案描述

文章出处:【微信号:数字芯片实验室,微信公众号:数字芯片实验室】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

求一种数字信道化IFM接收机的高效实现方案

如何设计并仿真一种数字误差校正威廉希尔官方网站 ?

求一种数字微波设备监控系统的设计

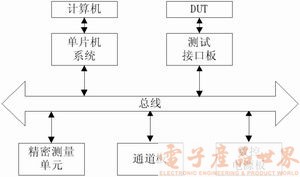

一种数字IC测试系统的设计

实现一种数字可调的升压型开关电源的设计方案

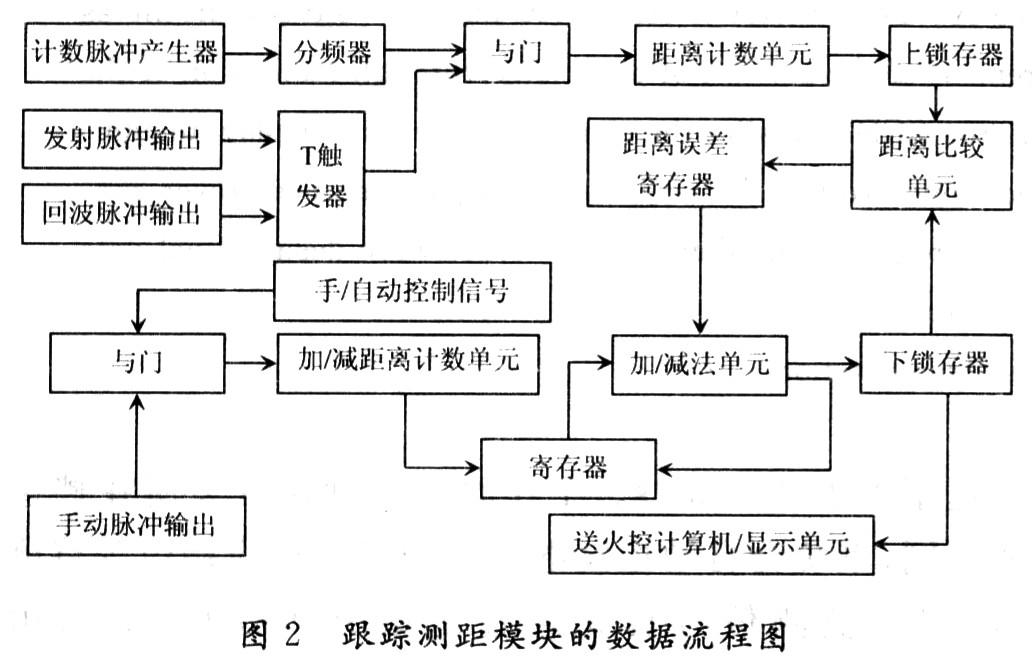

一种数字跟踪测距模块的设计与实现

一种数字图像接收测试系统的设计与实现

一种数字delayline的设计方案

一种数字delayline的设计方案

评论