一RZ/T、RZ/N系列MPU

芯片启动注意事项

RZ/T、RZ/N系列MPU有3路电源域,在启动时,外围设备也需要进行不同电源域的配置,所以电源时序,复位信号,以及系统管脚的配置都会影响芯片的启动流程,如果不能正确配置,芯片则有可能启动不正常,以下为芯片启动时需要注意的配置介绍。

二启动系统介绍

1电源

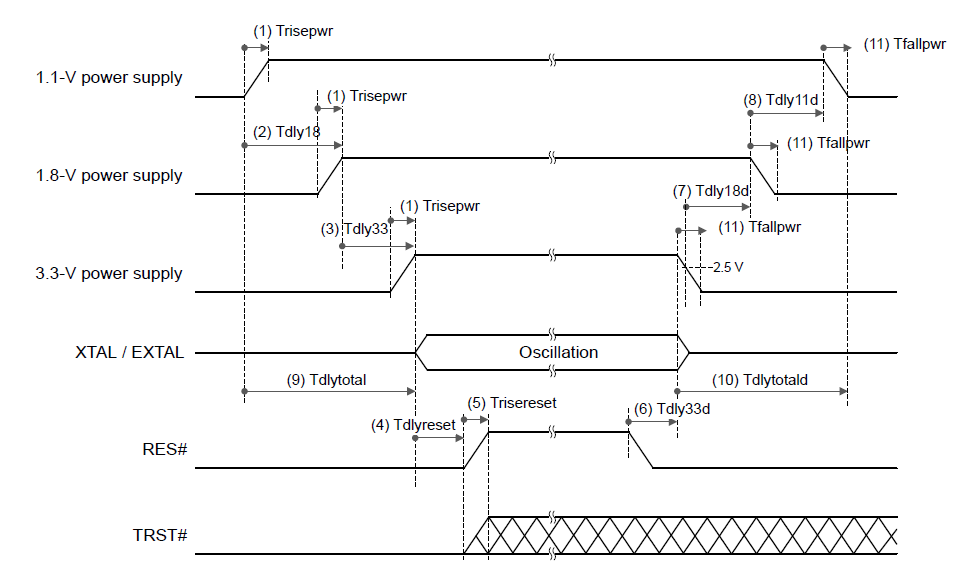

上下电时序要求:

芯片对于上下电有明确的时序要求,具体要求详见user manual(用户手册)>>Electrical Characteristics章节。

由于上电时序十分重要,大部分启动不了的问题都是上电时序不满足导致,所以瑞萨有匹配的电源时序控制方案可直接使用:

① PMIC(DAS9061/DA9080)

② GPARK(SLG46582)

2复位电路

RZT/RZN芯片有2个复位信号:

RES复位除了仿真电路以外的LSI外设,所以仿真器的复位需要连到此信号。

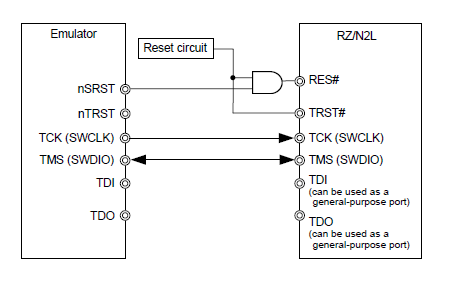

TRST复位TAP(Test Access Port),仿真器复位管脚不能连到此处,否则上电复位时,会直接复位TAP电路,导致不能仿真,此管脚有2种推荐接法:

a.和RES接相同的信号,使用仿真器时,参考接法如下:

b. 不用此管脚时,可通过一个下拉电阻接地,或和RES接相同的信号,注意不能悬空。

仿真器端有2个复位信号:

nSRST系统复位,一定要接,可通过调试器复位系统,方便调试。

nTRSTTAP复位,可不接。

3时钟

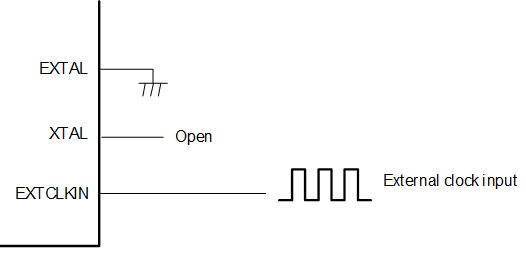

有源晶振

尤其是使用ECAT网络时,推荐使用有源晶振,接到EXTCLKIN,精度要求25ppm以内,EXTAL连接到VSS,XTAL保持开。

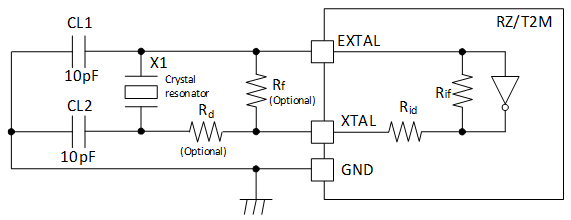

无源晶振

晶振和电容尽可能靠近EXTAL和XTAL引脚,晶体的PCB周围最好用GND包起来,用于屏蔽的GND走线宽度应不小于0.3 mm,与相邻走线之间应保持0.3 mm ~ 2.0 mm的距离。

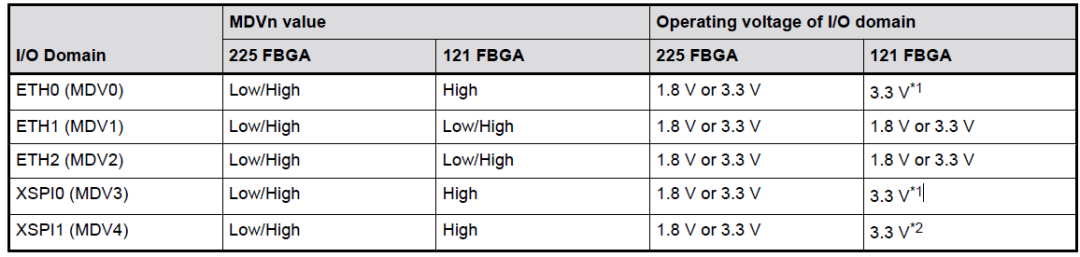

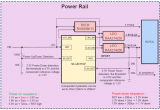

4MDV电源域配置管脚

点击可查看大图

RZT/RZN有不同的电源域配置,根据MDV0~MDV4管脚进行配置:

MDV0~MDV2

对应ETH0~ETH2,根据实际的PHY芯片选择对应的1.8V还是3.3V

MDV3~MDV4

对应XSPI0,XSPI1,根据外部配置的存储芯片类型确定。

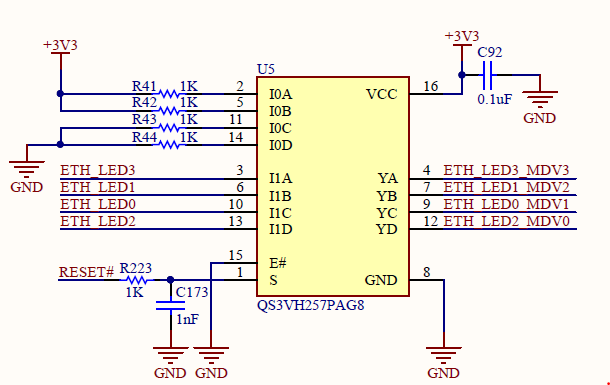

以上管脚只在复位释放时检测,程序正常启动后可以复用为其他功能,以下为参考设计方法,使用一个选通芯片进行选择,复位拉低时,选通固定的高低电平配置,复位拉高后,使用为EtherNET LED功能。

5其他需要特殊处理的系统管脚

MDD (JTAG authentication by hash signal)下拉(正常模式)。

BSCANP (Boundary scan setting)下拉(关闭边界扫描设置)。

MDX系统管脚,固定接下拉。

MDW (ATCM wait cycle select signal)此管脚配置ATCM的访问延时,如果CPU时钟低于或等于400MHz时,为0等待(MDW =0),高于400MHz时,为1个等待(MDW = 1),所以此管脚只在RZT系列才有,RZN系列最高跑在400MHz,不需要此管脚。

NMI (不可屏蔽中断) 上升沿或下降沿都会触发此中断,所以常规接法是将此管脚上拉。

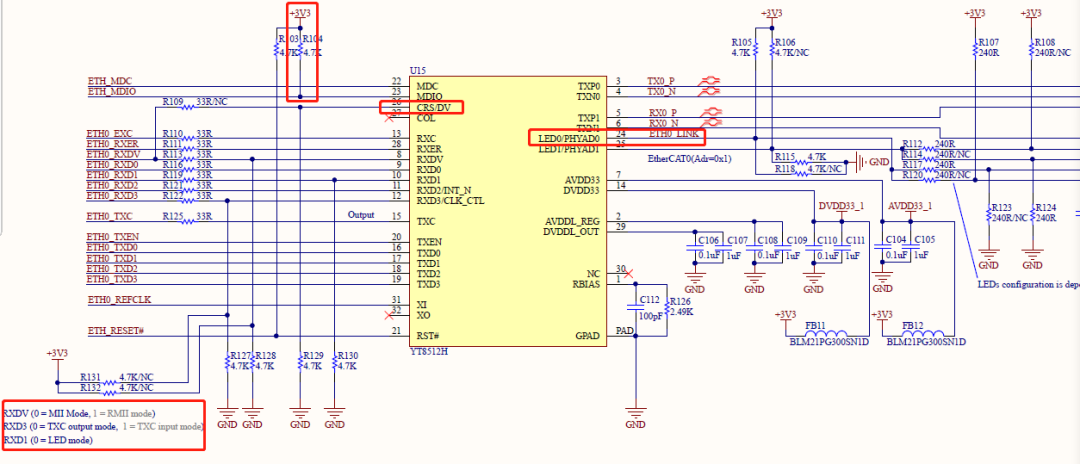

6网络周边 (适配YT8512为例)

ECAT推荐使用MII接口,小地址IN,大地址OUT,地址需要连续,地址0一般不用。

YT8512芯片LED1/PHYAD[1]/ETHn_LINK,3个信号在同一个管脚复用,所以需要做以下操作:

① LED的状态需要保持在稳定状态,即不能做成闪烁状态。(PHY寄存器改成0x30,收发包时,LED亮,down时,LED灭)

LEDO对应的寄存器为ext Reg0x40C0;(上电默认值为0x0311)

LED1对应的寄存器为ext Reg0x40C2;(上电默认值为0x0320)

向这两个寄存器赋不同值,则LED做相应的状态显示,典型几种配置如下:

ext Reg0x40C0/0x40C3 配置值

动作行为

0x0311

link在10M时,LED亮;link在10M且收发包,LED闪

0x0320

link在100M时,LED亮;link在100M且收发包,LED闪

0x30

link或收发包时,LED亮;link down时灭

0x1300

收发包时闪烁;不收发包即灭

② YT8512的LED1内部有自动检测外部上下拉状态的判断LED1有效的功能,需要根据PHY芯片LED1的上下拉状态,来对应配置MPU的link检测状态的极性PHYLNK.CATLNK,否则ECAT网络会反复Link-up,Link-down,以下是YT8512外围的参考设:

1. 硬件设计

●参考25Mhz时钟可以使用外部时钟源,或从芯片直接提供给PHY

●检查MDIO是否需要一个外部上拉电阻,CRS接地

●考虑在信号源附近增加串联终端电阻以减少信号线上的反射

2.PCB走线注意

●RMII/MII的阻抗为50欧姆±10%,大多数布线的正常标准

●所有MII/RMII信号线(数据线、时钟线和其他)应在单层上布线,并具有精确的长度匹

数据线和时钟线的迹长偏差应在10mm以内,应避免通孔

● MII/RMII信号的路径应该尽可能的直,且越短越好。否则,轨迹弯曲不应超过45度

●时钟信号走线硬尽可能短,特殊情况需要等长布线时,要可被地线屏蔽

●在信号层下面或上面放置一个地面层,以便MII/RMII信号的返回电流随时返回

审核编辑:汤梓红

-

电源

+关注

关注

184文章

17706浏览量

249985 -

处理器

+关注

关注

68文章

19265浏览量

229671 -

MPU

+关注

关注

0文章

357浏览量

48776 -

复位信号

+关注

关注

0文章

54浏览量

6315

原文标题:RZ/T2M N2L T2L原理图设计要点

文章出处:【微信号:瑞萨MCU小百科,微信公众号:瑞萨MCU小百科】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

RZ/T2M 组 RZ/T2M 电机解决方案套件启动手册(用于 EtherCAT)

RZ/T2M 组 RZ/T2M 电机解决方案套件启动手册(用于 EtherCAT)

RZ/G1H、RZ/G1M、RZ/G1N和 RZ/G1E Linux启动指南

工业MPU新标杆,多协议工业以太网+运动控制 - 瑞萨RZ/T2H 新产品

RZ/T、RZ/N系列MPU芯片启动注意事项

RZ/T、RZ/N系列MPU芯片启动注意事项

评论