AD9361是一款高性能的射频前端芯片,广泛应用于无线通信系统中。其中一个重要特性是其具有灵活可调的ADC采样率。本文将详细介绍AD9361的ADC采样率设置范围,包括其相关特性、设置方法以及在实际应用中的注意事项等。

- ADC采样率简介

ADC(Analog-to-Digital Converter)即模数转换器,是一种将interwetten与威廉的赔率体系 信号转换为数字信号的设备。在无线通信系统中,ADC常用于将射频信号转换为数字信号,以便进行数字信号处理和分析等操作。ADC的采样率是指每秒钟采集的样本数,通常以Hz为单位。较高的采样率可以提供更准确和详细的信号表示,但同时也需要更大的计算和存储资源。 - AD9361芯片简介

AD9361是ADI(Analog Devices Inc.)推出的一款集成了大量无线通信功能的射频前端芯片。它支持多种无线通信标准,如GSM、WCDMA、LTE等,并且拥有极高的性能和灵活性。在AD9361芯片中,ADC是用于将射频信号转换为数字信号的关键部件。 - AD9361的ADC采样率设置范围

AD9361芯片具有非常灵活的ADC采样率设置范围,可以根据实际需求进行调整。其最小采样率约为520 ksps(千样本每秒),最大采样率约为61.44 Msps(兆样本每秒)。用户可以通过编程配置AD9361的寄存器来设置所需的采样率。具体的设置方法可以参考AD9361的数据手册和编程指南。 - ADC采样率的选择

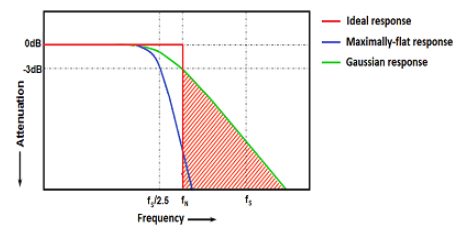

在选择ADC采样率时,需要综合考虑系统的要求和资源限制。较高的采样率可以提供更高的精度和细节,但同时也会增加数据处理和存储的负担。因此,在实际应用中,需要根据信号的带宽和系统的要求来选择合适的采样率。一般来说,采样率应该大于信号带宽的两倍,以满足尼奎斯特定理的要求。 - ADC采样率设置的注意事项

在进行ADC采样率设置时,需要注意以下几个方面:

- AD9361的ADC采样率设置需要与数字信号处理系统的其他参数相匹配,如处理器的计算能力和存储资源等。否则,可能导致数据处理能力不足或者资源浪费。

- 需要根据射频信号的带宽和调制方式来选择合适的ADC采样率。较高的采样率可以提供更好的信号还原效果,但同时也会增加功耗和计算负担。

- 在进行高速采样时,需要注意时钟和同步的稳定性。AD9361对于时钟和同步信号的质量要求比较高,需要采取相应的措施来避免时钟抖动和时钟偏差等问题。

综上所述,AD9361是一款具有灵活可调的ADC采样率的射频前端芯片。其采样率设置范围广泛,用户可以根据实际需求进行配置。在设置时,需要综合考虑系统的要求和资源限制,并注意时钟和同步的稳定性。通过合理设置ADC采样率,可以提高无线通信系统的性能和灵活性。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

芯片

+关注

关注

455文章

50730浏览量

423182 -

adc

+关注

关注

98文章

6496浏览量

544477 -

无线通信

+关注

关注

58文章

4564浏览量

143499 -

射频前端

+关注

关注

5文章

242浏览量

24382

发布评论请先 登录

相关推荐

请问AD9361 ADC的采样率是多少?

把基带接收到的信号存储起来做频谱分析,但不确定数据的采样率是多少?有个122.88MHz,还有个30.72MHz,到底哪个是采样率呢?它们有什么关系?希望有人能回答一下,谢谢!

发表于 09-19 10:08

请问AD9361的DATA_CLK和ADC COLCK RATE的关系是什么?

@@最近在调试AD9361的BBPLL,目前BB PLL 已经锁定。但不知道DATA_CLK这个时钟怎么配置?和ADC 的采样率有什么关系?参考时钟为40MHz,配置的ADC CLK

发表于 10-16 10:28

请问AD9361最大的AD和DA采样率是多少?

从AD9361手册上看到DATA_clock是最大速率是61.44M,但是在的adfcomms2的说明文档overview中显示的是显示着AD采样率是64MSPS。请问AD9361最大的AD和DA

发表于 12-12 09:37

请问AD9361的AD配置需要注意什么?

我在配置A9361的时候被难在了AD采样上面。我按照给的寄存器配置顺序配置的AD9361,发射已经OK。接收可以接收到信号,但是接收在没有信号的时候总是有很大的一个干扰信号在里面。我的基带采样

发表于 03-01 10:10

基于ADI AD9361模块AD-FMCOMMS3-EBZ搭建的AD9361 RF收发测试平台案例

AD9361芯片工作频率范围为70 MHz至6 GHz,涵盖大部分特许执照和免执照频段,通过对AD9361自身可编程改变采样速率、数字滤波器和抽取参数,使该芯片支持的通道带宽

adc采样率和带宽的关系

adc采样率和带宽的关系 ADC(Analog-to-Digital Converter),即模拟转数字转换器,是将模拟信号转换成数字信号的重要器件。其中,采样率和带宽是

如何优化adc的采样率

在数字信号处理领域,ADC是将模拟信号转换为数字信号的关键组件。采样率,即ADC每秒采集样本的次数,对信号的准确性和系统的整体性能有着直接的影响。 ADC

ad9361 ADC采样率设置范围

ad9361 ADC采样率设置范围

评论