R128 模组

针对 R128 芯片,百问科技提供推出了一种型号模块,如下表所示

| 型号 | SoC | CPU0 | CPU1 | DSP | SRAM | LS-PSRAM | HS-PSRAM | Flash | DAC |

|---|---|---|---|---|---|---|---|---|---|

| R128-S2-N16R16 | R128-S2 | Arm Cortex-M33 | C906 RISC-V | HIFI5 DSP | 1MByte | 8Mbyte | 8Mbyte | 16M NOR Flash | 2 Audio DACLINEOUTLP/NLINEOUTRP/N |

| R128-S3-ND128R32 | R128-S3 | Arm Cortex-M33 | C906 RISC-V | HIFI5 DSP | 1MByte | 32Mbyte | 128M NAND Flash | 1 Audio DACLINEOUTLP/N |

详细参数

- XuanTie 64Bit RISC-V [GCV] C906 CPU, Support Vector 0.7

- Arm M33 Star MCU

- HiFi5 Audio DSP Xtensa LX7

- 1MB SRAM

- 8MB SiP OSPI HS_PSRAM@800MHz

- 8MB SiP OSPI LS_PSRAM@AHB Clock with DMA

- 16MB SiP QSPI NOR

- RGB666, i8080, BT656, SPI Display up to 1024x768@60fps

- G2D 2D graphics acceleration

- DVP up to 1920x1088, JPEG encoding 1920x1088, 1024x768@40fps

- 3 Audio ADC, 24Bit, 8kHz-96kHz, Support 4 DMICs

- 2 Audio DAC, 24Bit, 8kHz-384kHZ

- USB2.0 OTG

- 3 * UART, 2 * SPI, 2 * TWI, 8 * PWM, 1 * 12Bit 10 Channels ADC

- IR TX/RX, LEDC up to 1024 * WS2812

- ISO 7816 Card Reader

- Wi-Fi Compatible with IEEE 802.11 b/g/n 2.4GHz

- Bluetooth 5.0 Dual Mode complies with V2.1/4.0/4.2/5.0, Support BR/EDR

- 25.5*18mm, IPEX ANT, ESP32-S3 Compatible Pinout

资源下载

- 硬件工程开源地址:https://oshwhub.com/gloomyghost/r128-module

- 电路原理图:SCH_R128-S2_2023-10-08.pdf

- PCB图:PCB_R128-S2_2023-10-08.pdf

- PCB:ProDocument_R128-S2-N16R16_2023-10-08.epro

- GERBER:SCH_R128-S2_2023-10-08.pdf

- ODB++:odb++_pcb_2023-10-08.zip

- 3D STEP:3D_R128-S2_2023-10-08.zip

- BOM:BOM_R128-S2-N16R16_R128-S2_2023-10-08.xlsx

- 点位图:PickAndPlace_R128-S2_2023-10-08.xlsx)

- 引脚图:R128-S2-N16R16_PINOUT.svg

购买链接

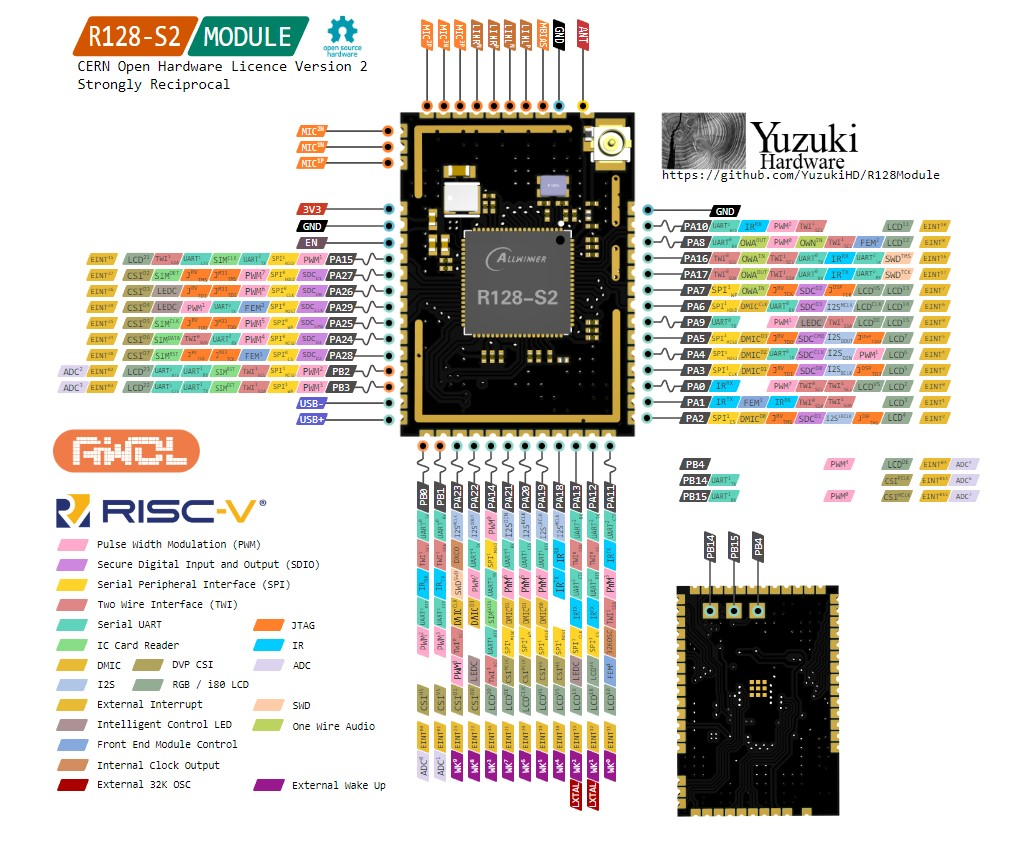

引脚图

高清引脚图:R128-S2-N16R16_PINOUT.svg

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

R128

+关注

关注

0文章

41浏览量

105

发布评论请先 登录

相关推荐

UN/ECE R128解读

UNECER128测试涵盖了根据相关法规进行的一系列测试,用于评估法规中规定的发光二极管(LED)设备类别中的车辆。ECE法规定义了用于建立机动车和机动车零部件的批准或统一批准程序的跨境威廉希尔官方网站

法规

全志R128 Devkit开发板原理图模块介绍及使用说明

针对 R128 模组,百问科技推出了 R128 DevKit 开发板作为快速开发评估工具。

板载 R128-S2-N16R16 模组

板

发表于 01-17 09:45

全志R128 SDK架构与目录结构

R128 S2 是全志提供的一款 M33(ARM)+C906(RISCV-64)+HIFI5(Xtensa) 三核异构 SoC,同时芯片内部 SIP 有 1M SRAM、8M LSPSRAM、8M

发表于 01-05 10:05

全志R128硬件设计指南①

控制功能,可让R128实现上电复位功能。

RESET/CHIP-PWD信号上接下地电容默认为 1nF,用于滤波和增强 ESD 防护能力

为避免 SOC启动时误进入升级状态,PA1/FEL0和 PA2

发表于 01-04 09:23

全志R128入门编写HelloWorld

方案选择r128s2_module_c906

code">$ source envsetup.sh $ lunch_rtos 1

编辑程序打开你喜欢的编辑器

发表于 12-29 09:39

全志R128 DSP开发工具安装教程

下的 dsp_raw.bin 拷贝到 R128 根SDK 下的 board/r128s/xxx/bin/ 下,并重命名为rtos_dsp_sun20iw2p1.fex。

R128 SD

发表于 12-28 17:21

详解全志R128 RTOS安全方案功能

方案来说,Brom 加载并校验 Sboot,再由 Sboot 加载和校验 M33 S‑OS,最后 Uboot 对 M33 N‑OS、RISC‑V OS、DSP OS 进行加载和校验

签名校验R128

发表于 12-28 15:59

DshanMCU-R128s2芯片手册与资料

: Xplorer Software (SDK) Download Xtensa Xplorer 授权申请: Cadence Tensilica Offerings Xtensa Xplorer 试用申请: request an evaluation license 其余手册将在R128芯片正式发布后上传

DshanMCU-R128s2芯片参数

MB LS PSRAM R128 S2)/8 channels (R128 S3) - One LEDC used to control the external intellige

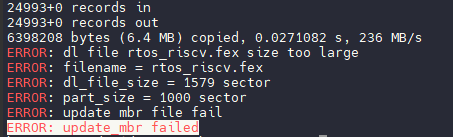

DshanMCU-R128s2常见问题

) copied, 0.0271082 s, 236 MB/sERROR: dl file rtos_riscv.fex size too largeERROR: filename

DshanMCU-R128s2芯片外设支持列表

LCD 显示屏 厂商 分辨率 型号 接口 FPS 100ask 480 x 320 Dshan_Display Module SPI 60 摄像头 Sensor 厂商 分辨率 型号 Size 接口 FPS GalaxyCore VGA, 640 x 480 GC0308 1/6.5 DVP 30 GalaxyCore UXGA, 1616 x 1232 GC2145 1/5 DVP 13

DshanMCU-R128s2硬件设计参考

R128 DevKit 开发板 硬件工程开源地址:https://oshwhub.com/gloomyghost/r128-module 电路图

DshanMCU-R128s2术语表

RISC-V 架构的 64 位元处理器单元 HIFI5 Cadence 推出的 Cadence Tensilica HiFi 5 DSP 32 位处理器单元 R128 全志推出的一款包含

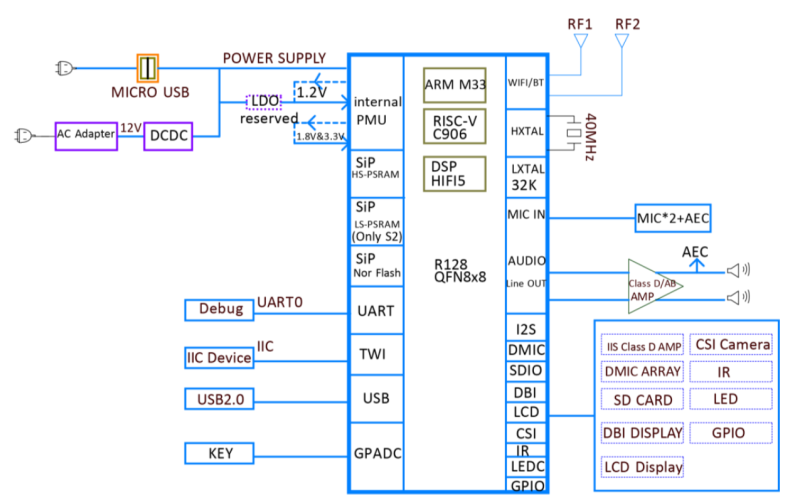

DshanMCU-R128s2硬件设计指南

原理图设计 硬件系统框图 R128是一颗专为“音视频解码”而打造的全新高集成度 SoC,主要应用于智能物联和专用语音交互处理解决方案。 单片集成 MCU+RISCV+DSP+CODEC+WIFI

DshanMCU-R128s2 R128 模组

DshanMCU-R128s2 R128 模组

评论