DDS简介:

DDS 同 DSP(数字信号处理)一样,是一项关键的数字化威廉希尔官方网站 。DDS 是直接数字式频率合成器(Direct Digital Synthesizer)的英文缩写。与传统的频率合成器相比,DDS 具有低成本、低功耗、高分辨率和快速转换时间等优点,广泛使用在电信与电子仪器领域,是实现设备全数字化的一个关键威廉希尔官方网站 。

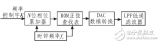

DDS 芯片的功能主要包括频率控制寄存器、高速相位累加器和正弦计算器三个部分。频率控制寄存器可以串行或并行的方式装载并寄存用户输入的频率控制码;而相位累加器根据频率控制码在每个时钟周期内进行相位累加,得到一个相位值;正弦计算器则对该相位值计算数字化正弦波幅度(芯片一般通过查表得到)。

DDS 芯片输出的一般是数字化的正弦波,因此还需经过高速 D/A 转换器和低通滤波器才能得到一个可用的interwetten与威廉的赔率体系 频率信号。关于想了解更多的 DDS 的相关知识, 大家可以到百度直接搜索。

下面主要来给大家介绍FPGA 程序的设计, DDS IP 的配置和调试。

编写 dds_wave 的 verilog 程序

`timescale1ns/1ps ////////////////////////////////////////////////////////////////////////////////// //Company: //Engineer: // //CreateDate:103307/17/2018 //DesignName: //ModuleName:dds_wave //ProjectName: //TargetDevices: //Toolversions: //Description: // //Dependencies: // //Revision: //Revision0.01-FileCreated //AdditionalComments: // ////////////////////////////////////////////////////////////////////////////////// moduledds_wave(clk,key1,data,da_clk ); inputclk,key1; output[7:0]data; outputda_clk; reg[15:0]key1_cout; reg[7:0]data_o; regdds_we; reg[28:0]dds_data; reg[3:0]dds_freq=0; regdds_we_req; wire[7:0]sine; assignsine_reg=sine[6:0]; assignda_clk=clk; assigndata=data_o; //有符号数转化为无符号输出到DA always@(posedgeclk) begin if(sine[7]==1'b1) data_o<= sine - 128; else data_o <= sine + 128; end //控制DDS输出不同 always @(negedge clk) begin dds_we <= dds_we_req; case(dds_freq) 4'd0: dds_data <= 29'd107; //10Hz:(dds_data*2^29/50*1000000) 4'd1: dds_data <= 29'd1074; //100Hz:(dds_data*2^29/50*1000000) 4'd2: dds_data <= 29'd10737; //1kHz:(dds_data*2^29/50*1000000) 4'd3: dds_data <= 29'd53687; //5kHz:(dds_data*2^29/50*1000000) 4'd4: dds_data <= 29'd107374; //10kHz:(dds_data*2^29/50*1000000) 4'd5: dds_data <= 29'd536871; //50kHz:(dds_data*2^29/50*1000000) 4'd6: dds_data <= 29'd1073742; //100Hz:(dds_data*2^29/50*1000000) 4'd7: dds_data <= 29'd5368709; //500Hz:(dds_data*2^29/50*1000000) 4'd8: dds_data <= 29'd10737418; //1mHz:(dds_data*2^29/50*1000000) 4'd9: dds_data <= 29'd21474836; //2mHz:(dds_data*2^29/50*1000000) 4'd10: dds_data <= 29'd32212255; //3mHz:(dds_data*2^29/50*1000000) 4'd11: dds_data <= 29'd42949672; //4mHz:(dds_data*2^29/50*1000000) 4'd12: dds_data <= 29'd53687091; //5mHz:(dds_data*2^29/50*1000000) 4'd13: dds_data <= 29'd64424509; //6mHz:(dds_data*2^29/50*1000000) 4'd14: dds_data <= 29'd75161928; //7mHz:(dds_data*2^29/50*1000000) 4'd15: dds_data <= 29'd85899346; //8mHz:(dds_data*2^29/50*1000000) default: dds_data <= 29'd107; // 1kHz:(dds_data*2^29/50*1000000) endcase end //按钮处理程序,改变DDS的输出频率 always @(posedge clk) begin if(key1 == 1'b0) key1_cout <= 0; else if((key1 == 1'b1) & (key1_cout <= 16'hc350)) key1_cout <= key1_cout + 1'b1; if(key1_cout == 16'hc349) begin dds_freq <=dds_freq + 1'b1; dds_we_req <= 1'b1; end else begin dds_freq <=dds_freq; dds_we_req <= 1'b0; end end //DDS IP产生sin/cos波形 sin_cos sin_cos_inst( .clk(clk), .we(dds_we), .data(dds_data), .cosine(cosine), .sine(sine), .phase_out() ); endmodule

程序通过检测开发板上按键 KEY1 ,如果按键 KEY1 每按下一次,寄存器 dds_freq 的值就会加 1, 程序就会对 DDS IP 写入一个 data 数据来改变相位的增加量,从而改变输出波形的频率。程序中设置了 16 种相位的增加量,所以可以让 DDS 产生 16 个不同频率的正弦波。在本实验的 DDS IP 的配置中,相位增加的数据宽度为 29 位,所以最小的频率输出为50Mhz/2^29, 约 0.093Hz。如果想让 DDS 输出 1Khz 的波形,就需要写入相位增加值10737 。相位增加值和频率的计算公式如下:

相位增加值=( fhz * 2^29 )/( 50 * 1000000)

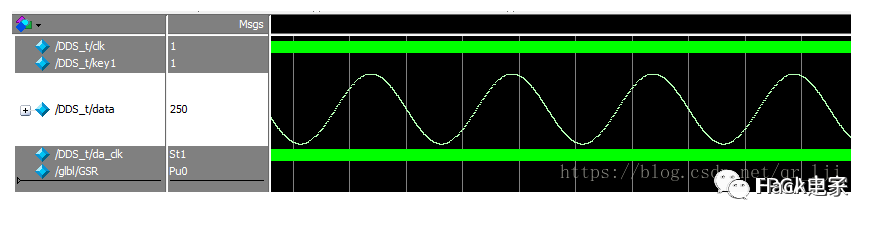

仿真图如下:

审核编辑:汤梓红

-

合成器

+关注

关注

0文章

273浏览量

25356 -

正弦波发生器

+关注

关注

1文章

26浏览量

15658 -

Verilog

+关注

关注

28文章

1351浏览量

110077 -

DDS

+关注

关注

21文章

633浏览量

152631

原文标题:Verilog实现DDS 正弦波发生器

文章出处:【微信号:ZYNQ,微信公众号:ZYNQ】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

基于DDS威廉希尔官方网站 的高频正弦波发生器的设计

基于DDS威廉希尔官方网站 的高频正弦波发生器的设计

基于Verilog实现的DDS任意波形发生器

Verilog实现DDS正弦波发生器

Verilog实现DDS正弦波发生器

评论