文章来源:SiP与先进封装威廉希尔官方网站

原文作者:Suny Li

先进封装是什么以及先进封装相比于传统封装的优势

1.引 言

说起传统封装,大家都会想到日月光ASE,安靠Amkor,长电JCET,华天HT,通富微电TF等这些封装大厂OSAT;说起先进封装,当今业界风头最盛的却是台积电TSMC,英特尔Intel,三星SAMSUNG等这些顶尖的半导体晶圆厂IC Foundry,这是为何呢?

如果你认为这些半导体晶圆大佬们似乎显得有些"不务正业"?那你就大错特错了!

传统封装的功能主要在于芯片保护、尺度放大、电气连接三项功能,先进封装和SiP在此基础上增加了“提升功能密度、缩短互联长度、进行系统重构”三项新功能。

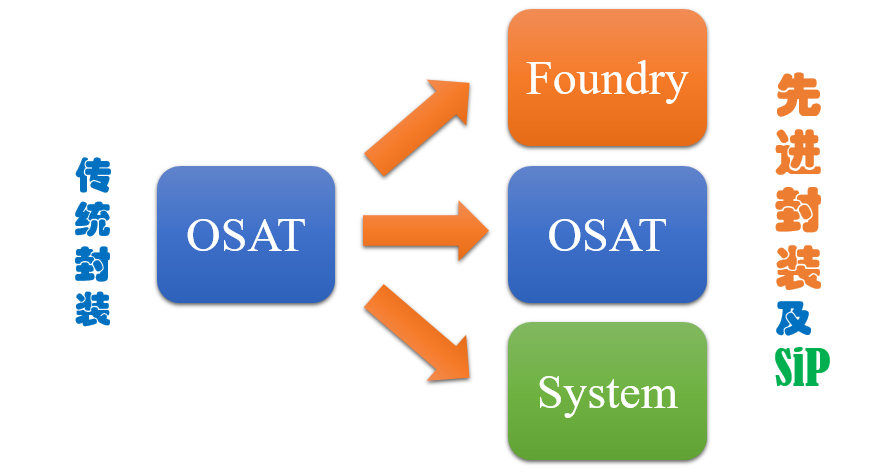

正是由于这些新特点,使得先进封装和SiP的业务从OSAT拓展到了包括Foundry、OSAT和System系统厂商。

Foundry由于其先天具有的工艺优势,在先进封装领域可以独领风骚,系统厂商则是为了在封装内实现系统的功能开始重点关注SiP和先进封装。

那么,先进封装和传统封装的分界点到底在哪里?如何界定先进封装呢?这就是我们这篇文章要重点讨论的问题:先进封装的“四要素”。

2.先进封装的四要素

先进封装的四要素是指:RDL,TSV,Bump,Wafer,任何一款封装,如果具备了四要素中的任意一个,都可以称之为先进封装。

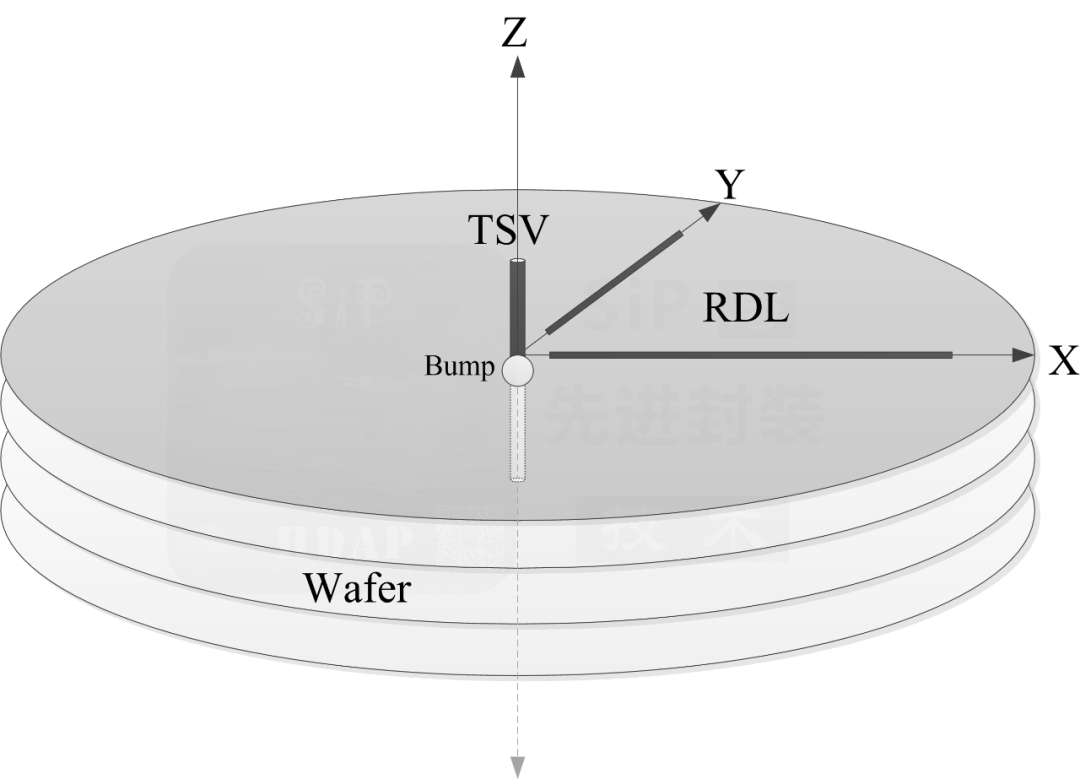

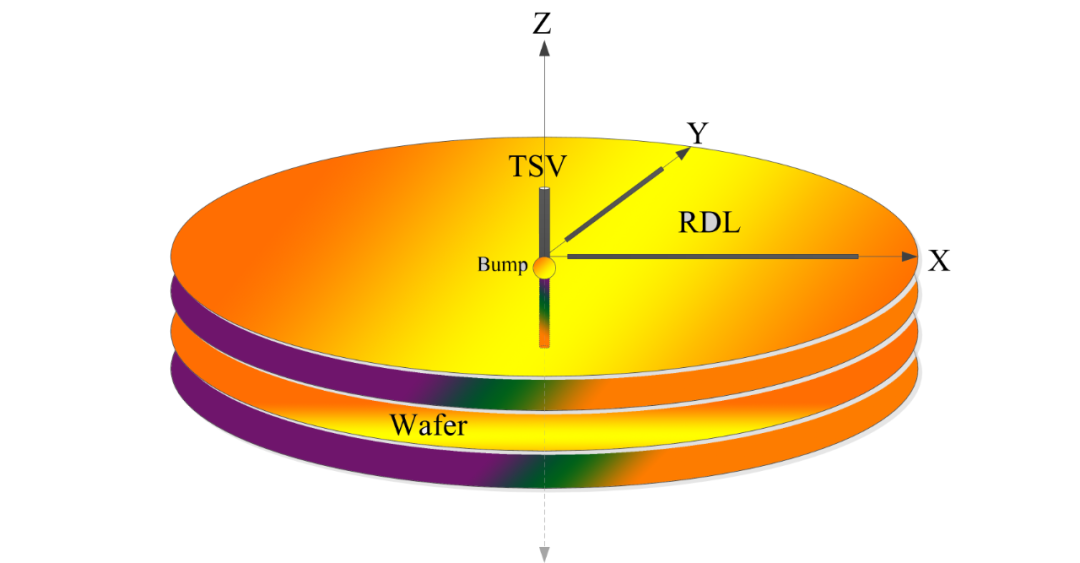

在先进封装的四要素中,RDL起着XY平面电气延伸的作用,TSV起着Z轴电气延伸的作用,Bump起着界面互联和应力缓冲的作用,Wafer则作为集成电路的载体以及RDL和TSV的介质和载体,如下图所示,为先进封装四要素的功能示意图。

先进封装的四要素(原创)

首先,我们要明确,在特定的历史时期,先进封装只是一个相对的概念,现在的先进封装在未来可能就是传统封装。

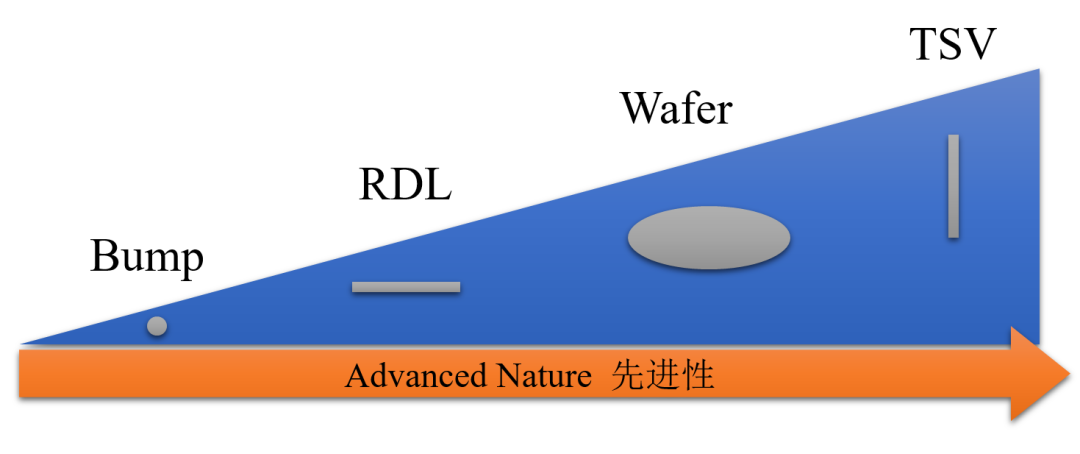

下图是作者根据四要素内在的先进性做了简单排序,大致如下:Bump → RDL → Wafer → TSV。

一般来说,出现的越早的威廉希尔官方网站 其先进性就相对越低,出现越晚的威廉希尔官方网站 其先进性就相对越高。

下面,我们就逐一阐述先进封装的四要素。

3.Bump

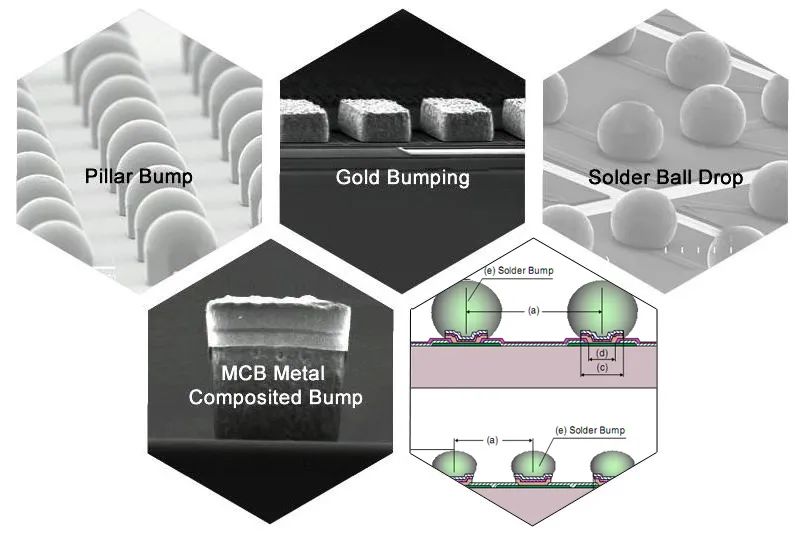

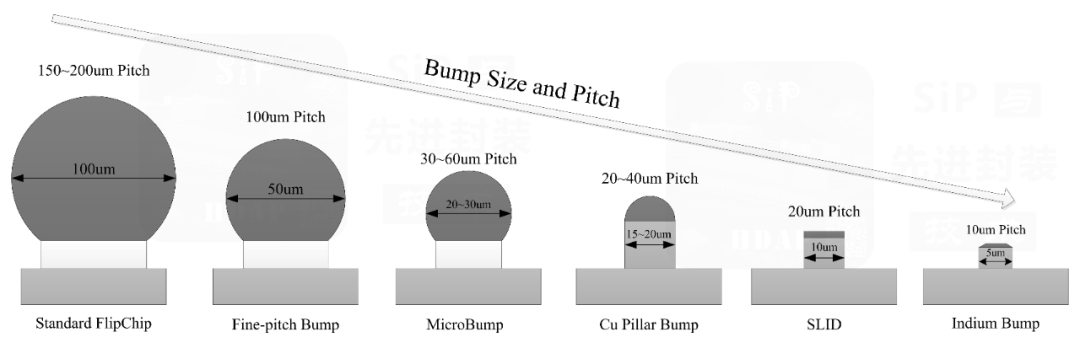

Bump是一种金属凸点,从倒装焊FlipChip出现就开始普遍应用了,Bump的形状也有多种,最常见的为球状和柱状,也有块状等其他形状,下图所示为各种类型的Bump。

Bump起着界面之间的电气互联和应力缓冲的作用,从Bondwire工艺发展到FlipChip工艺的过程中,Bump起到了至关重要的作用。

随着工艺威廉希尔官方网站 的发展,Bump的尺寸也变得越来越小,下图显示的是Bump尺寸的变化趋势。

可以看出, Bump尺寸从最初 Standard FlipChip的100um发展到现在最小的5um。

那么,会不会有一天,Bump小到不再需要了呢?

确实有这种可能,TSMC发布的SoIC威廉希尔官方网站 中,最鲜明的特点是没有凸点(no-Bump)的键合结构,因此,该威廉希尔官方网站 具有有更高的集成密度和更佳的运行性能。

4.RDL

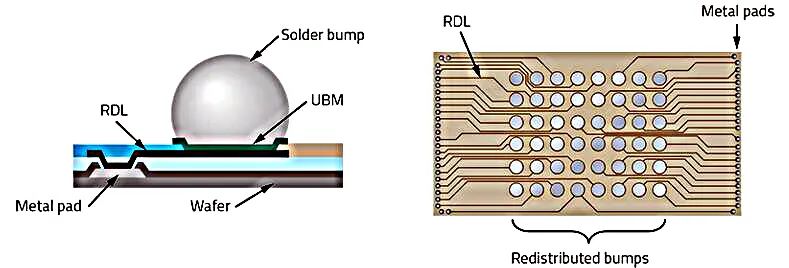

RDL(ReDistribution Layer)重布线层,起着XY平面电气延伸和互联的作用。

在芯片设计和制造时,IO Pad一般分布在芯片的边沿或者四周,这对于Bond Wire工艺来说自然很方便,但对于Flip Chip来说就有些勉为其难了。

因此,RDL就派上用场了,在晶元表面沉积金属层和相应的介质层,并形成金属布线,对IO 端口进行重新布局,将其布局到新的,占位更为宽松的区域,并形成面阵列排布,如下图所示。

在先进封装的FIWLP (Fan-In Wafer Level Package) ,FOWLP (Fan-Out Wafer Level Package) 中,RDL是最为关键的威廉希尔官方网站 ,通过RDL将IO Pad进行扇入Fan-In或者扇出Fan-Out,形成不同类型的晶圆级封装。

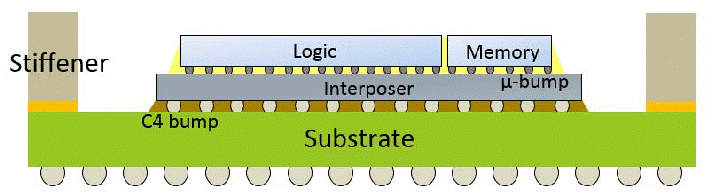

在2.5D IC集成中,除了硅基板上的TSV,RDL同样不可或缺,通过RDL将网络互联并分布到不同的位置,从而将硅基板上方芯片的Bump和基板下方的Bump连接。

在3D IC集成中,对于上下堆叠是同一种芯片,通常TSV就可以直接完成电气互联功能了,而堆叠上下如果是不同类型芯片,则需要通过RDL重布线层将上下层芯片的IO进行对准,从而完成电气互联。

随着工艺威廉希尔官方网站 的发展,通过RDL形成的金属布线的线宽和线间距也会越来越小,从而提供更高的互联密度。

5. Wafer

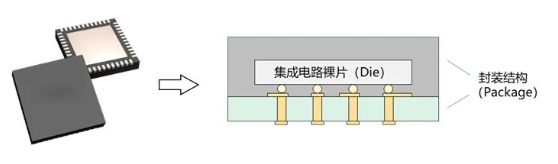

Wafer晶圆在当今半导体行业具有广泛的用途,既可以作为芯片制造的基底,也可以在Wafer上制作硅基板实现2.5D集成,同时可用于WLP晶圆级封装,作为WLP的承载晶圆。

Wafer最初仅用在芯片制造上,作为集成电路生产的载体,在Wafer上进行光刻、刻蚀、气相沉积、离子注入、研磨等工序,反复操作,精密控制,最终制造出集成电路芯片。

随着先进封装威廉希尔官方网站 的快速发展,Wafer的用途也变得越来越广泛。

传统封装是先进行裸芯片的切割分片,然后进行封装,而晶圆级封装WLP是在Wafer基础上先封装,然后切割分片。这就提高了封装效率,节省了成本,从而得到了广泛的应用。

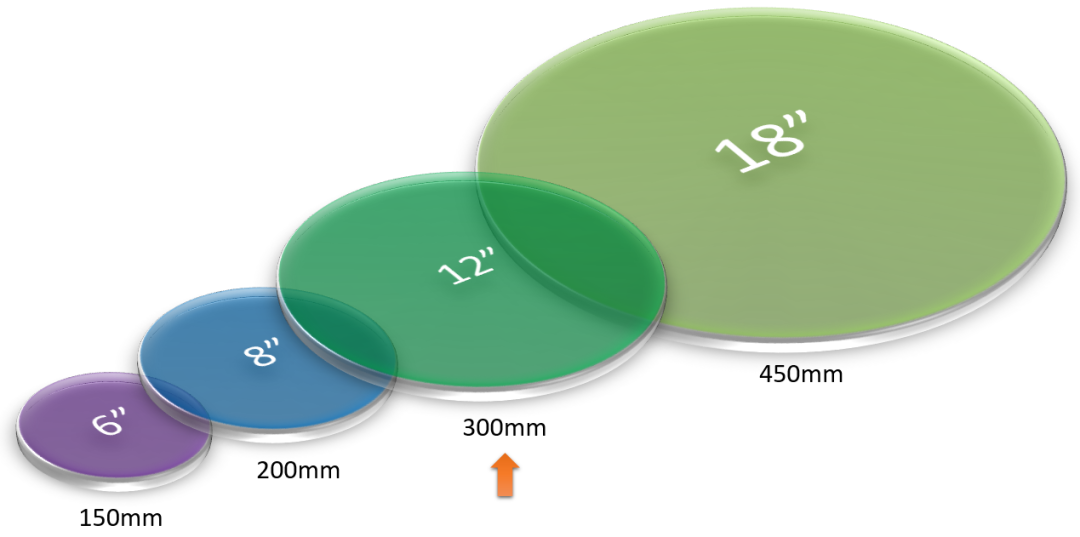

前面,我们讨论了,随着威廉希尔官方网站 的发展,Bump和RDL会变得越来越细小,Bump甚至最终会消失,而Wafer则会变得越来越大,从早先的6英寸到8英寸到现在普遍应用的12英寸以及将来要广泛应用的18英寸,都体现了这样的特点,如下图所示。

晶圆尺寸越大,同一圆片上可生产的IC就越多,可降低成本,提高效率,但对材料威廉希尔官方网站 和生产威廉希尔官方网站 的要求也会更高。

从FIWLP、FOWLP到2.5D集成、3D集成,基本都是在Wafer基础上进行的。

6.TSV

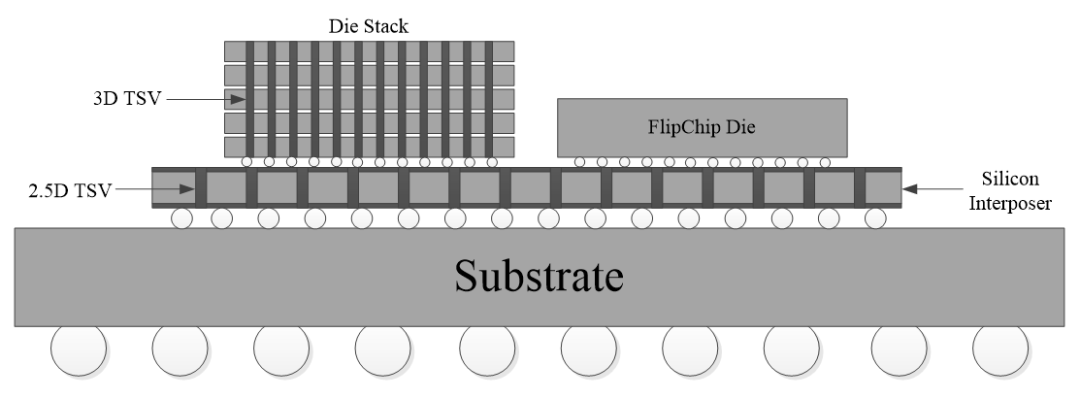

TSV(Through Silicon Via )硅通孔,其主要功能是Z轴电气延伸和互联的作用。

TSV按照集成类型的不同分为2.5D TSV和3D TSV,2.5D TSV是指的位于硅转接板Inteposer上的TSV,3D TSV 是指贯穿芯片体之中,连接上下层芯片的TSV,如下图所示。

下图所示为贯穿芯片体的3D TSV 的立体示意图。

TSV的制作可以集成到生产工艺的不同阶段,通常放在晶元制造阶段的叫 Via-first,放在封装阶段的叫Via-last。

将TSV在晶圆制造过程中完成,此类硅通孔被称作Via-first。Via-first TSV又可分为两种阶段,一种是在Foundry厂前端金属互连之前进行,实现core-to-core的连接。该方案目前在微处理器等高性能器件领域研究较多,主要作为SoC的替代方案。另外一种是在CMOS完成之后再进行TSV的制作,然后完成器件制造和后端的封装。

将TSV放在封装生产阶段,通常被称作Via-last,该方案可以不改变现有集成电路流程和设计。目前,业界已开始在高端的Flash和DRAM领域采用Via-last威廉希尔官方网站 ,即在芯片的周边进行硅通孔TSV制作,然后进行芯片或晶圆的层叠。

TSV的尺寸范围比较大,大的TSV直径可以超过100um,小的TSV直径小于1um。

随着工艺水平的提升,TSV可以做的越来越小,密度也越来越大,目前最先进的TSV工艺,可以在芝麻粒大小的1平方毫米硅片上制作高达10万~100万个TSV。

和Bump以及RDL类似,TSV的尺寸也会随着工艺的提高变得越来越小,从而支撑更高密度的互联。

**7.总结 **

RDL,TSV,Bump,Wafer是先进封装的四要素,任何一款封装,如果具备了四要素中的任意一个,都可以称之为先进封装。

在先进封装四要素中,Wafer是载体和基底,RDL负责XY平面的延伸,TSV负责Z轴的延伸,Bump负责Wafer界面间的连接和应力缓冲。

这四要素中,一大三小,一大是指Wafer,三小是指Bump、RDL、TSV。

随着威廉希尔官方网站 和工艺的发展,大要素会越来越大,而小要素则会越来越小。

审核编辑:汤梓红

-

集成电路

+关注

关注

5387文章

11536浏览量

361659 -

半导体

+关注

关注

334文章

27305浏览量

218155 -

晶圆

+关注

关注

52文章

4895浏览量

127939 -

SiP

+关注

关注

5文章

503浏览量

105315 -

先进封装

+关注

关注

2文章

400浏览量

241

原文标题:先进封装的“四要素”

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

盘点先进封装基本术语

超越芯片表面:探索先进封装威廉希尔官方网站 的七大奥秘

晶振采购需考虑四要素

简述熔断保险丝熔断四要素

简述气体放电管选型四要素

浅谈半导体封装威廉希尔官方网站 和先进封装威廉希尔官方网站 解析

先进封装威廉希尔官方网站 的发展与机遇

先进封装厂关于Bump尺寸的管控

浅析先进封装的四大核心威廉希尔官方网站

什么是先进封装?先进封装威廉希尔官方网站 包括哪些威廉希尔官方网站

浅谈先进封装的四要素

浅谈先进封装的四要素

评论