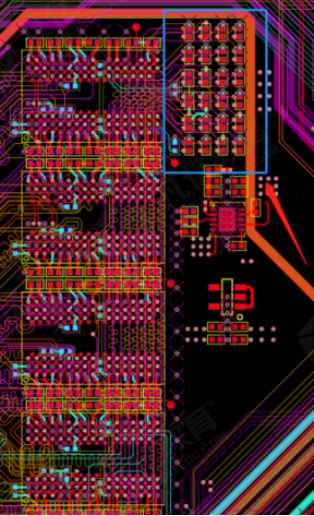

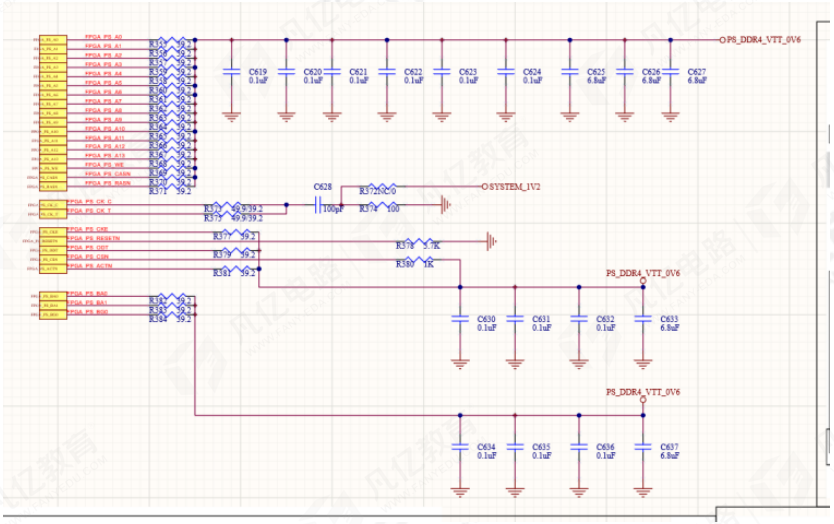

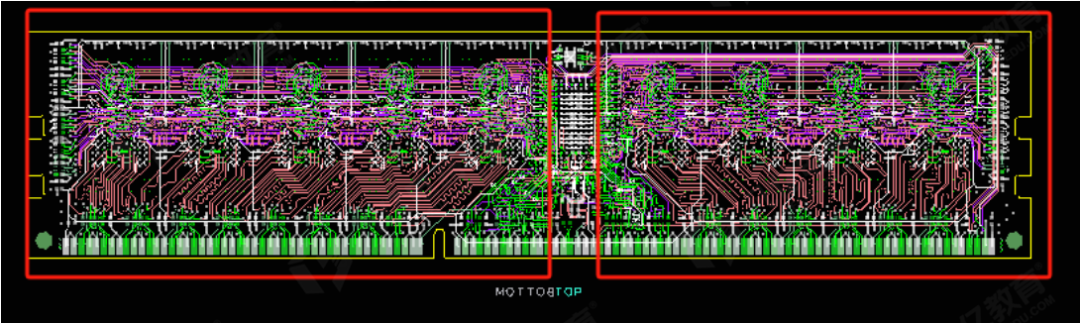

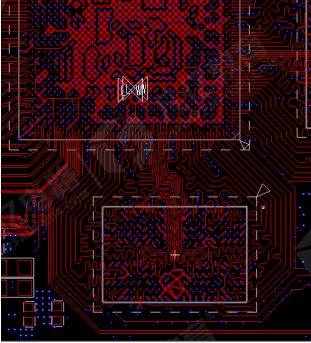

大家如果做过DDR的设计可能会发现在进行多片DDR连线时,通常在信号的末端会放置很多的电阻(如下图所示),那么这些电阻都是起什么作用的呢?

通常在DDR末端的电阻是为了防止信号反射的,起阻抗匹配的作用,之前我们介绍过另一种防止信号反射的解决措施,就是在信号的发送端串联一个电阻,从信号源端把问题解决,我们本次讲的端接方式是从信号的末端入手,消除信号反射!

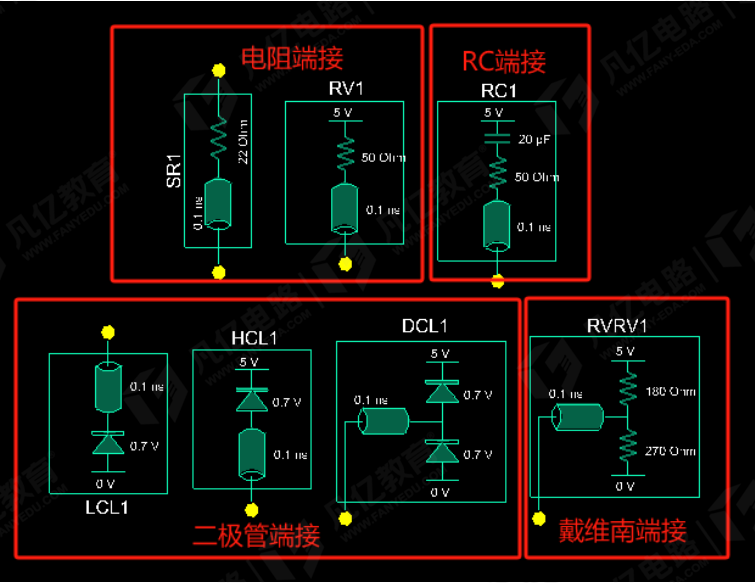

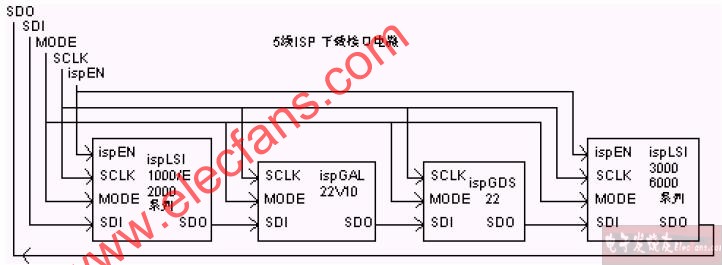

信号末端端接的方式有很多种,基本端接样式式如下图所示:

通常这些端接都可以有效的抑制信号的反射,不同的端接的应用场景也是有点区别的。

终端匹配电阻通过调整传输线末端的阻抗,使得反射信号与原始信号相互抵消。当传输线末端的阻抗与数据线之间的阻抗相匹配时,反射波最小,从而提高信号传输的质量和稳定性。

戴维南端接使用了两个电阻并联的方式,一个电阻下拉到地,一个电阻上拉到电源,其中接电源的电阻可以使驱动器更加容易到达逻辑高电平,接地的电阻可以使驱动器更加容易到达逻辑低电平,这两个并联电阻需要与传输线的阻抗相匹配,比如两个电阻为R1和R2两个电阻的阻值选取需要满足公式Z0=R1*R2/R1+R2。

AC端接是在原有单一电阻端接上加了一个电容,一般采用0.1uF多层陶瓷电容,电容具有隔直流通交流的特性,因此可以有效的降低功率消耗,同时电容容值选取适当可以有效消除信号的过冲和下冲。

肖特基二极管端接是由两个二极管组成,传输线末端任何的信号反射,如果导致接收器输入端上的电压超过VCC和二极管的正向偏值电压,该二极管就会正向导通连接到VCC上。该二极管导通从而将信号的过冲箝位到VCC和二极管的阈值电压的和上。

同样连接到地上的二极管也可以将信号的下冲限制在二极管的正向偏置电压上。然而该二极管不会吸收任何的能量,而仅仅只是将能量导向电源或者是地。该端接能有效减小信号过冲和下冲,但是二极管的开关速度会限制响应时间,所以较高速系统不合适。

端接的方式有很多种,但是其目的都是一样的,都是为了改善信号的质量,我们应该在合适的场景下选择相应的端接方式。同时我们需要注意的是端接电阻需要尽量靠近最后一片DDR颗粒,这样信号的改善效果最好。

审核编辑:刘清

-

二极管

+关注

关注

147文章

9634浏览量

166374 -

驱动器

+关注

关注

52文章

8232浏览量

146282 -

阻抗匹配

+关注

关注

14文章

351浏览量

30798 -

DDR

+关注

关注

11文章

712浏览量

65319 -

陶瓷电容

+关注

关注

3文章

437浏览量

23914

原文标题:为什么多片DDR菊花链拓扑连接时末端需要接很多的电阻

文章出处:【微信号:FANYPCB,微信公众号:凡亿PCB】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

采用菊花链的方式连接多片ADS1299,有的片是内部信号的高电平有的是低电平,如何解决?

多片ADS1298采用哪种方式连接(级联或者菊花链)?

SDRAM的电源系统及拓扑结构

ddr3菊花链拓扑结构是什么

多片DDR菊花链拓扑连接时末端的电阻都是起什么作用的呢?

多片DDR菊花链拓扑连接时末端的电阻都是起什么作用的呢?

评论