RISC-V(发音为“RISC five”)的目标是成为一款通用的指令集架构(Instruction Set Architecture,ISA):

• 它要适合设计各种规模的处理器,包括从最小的嵌入式控制器到最快的高性能计算机。

• 它要兼容各种流行的软件栈和编程语言。

• 它要适用于所有实现威廉希尔官方网站 ,包括 FPGA(Field-Programmable Gate Array,现场可编程逻辑门阵列)、ASIC(Application-Specific Integrated Circuit,专用集成电路)、全定制芯片,甚至未来的制造元件威廉希尔官方网站 。

• 它能用于高效实现所有微体系结构,包括微程序或硬连线控制,顺序、解耦或乱序流水线,单发射或超标量等。

• 它要支持高度定制化,成为定制加速器的基础,以应对摩尔定律的放缓。

• 它要稳定,基础 ISA 不会改变。更重要的是,它不能像以往的公司专有 ISA 那样消亡,包括 AMD 的 Am29000、Digital 的 Alpha 和 VAX、Hewlett Packard1 的 PARISC、Intel 的 i860 和 i960、Motorola 的 88000,以及Zilog 的 Z8000。

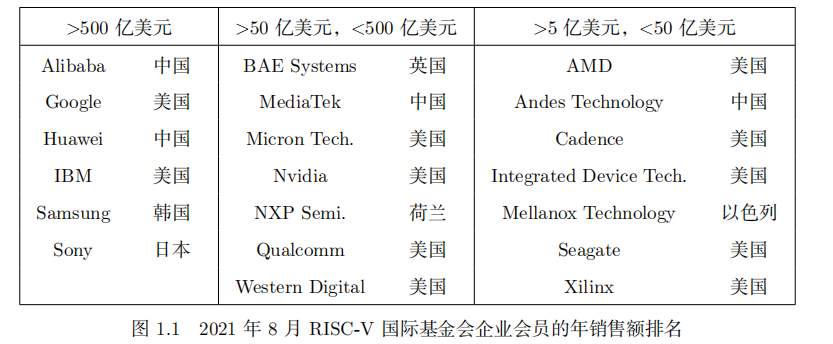

RISC-V 是一款与众不同的 ISA,不仅因为它年轻(它诞生于 2010 年,而其他 ISA 大多诞生于 20 世纪 70 年代或 80年代),而且因为它开放。与过去几乎所有的架构不同,其未来不受任何一家公司的兴衰或心血来潮的决策所影响(过去许多 ISA 因此消亡)。相反,RISC-V 属于一个开放的、非营利性质的基金会。RISC-V 国际基金会的目标是维护 RISC-V 的稳定性,仅出于威廉希尔官方网站 原因而缓慢谨慎地改进 RISC-V,并推动RISC-V 在硬件中流行起来,犹如 Linux 在操作系统中流行一般。图 1.1 列出了 RISC-V 国际基金会最大的企业会员,展示了 RISC-V 的繁荣。

模块化ISA和增量型ISA

Intel 曾将其未来押在高端微处理器上,但这还需要很多年时间。为与 Zilog 公司抗衡,Intel 开发了一款名为8086 的过渡产品。它本该朝生暮死,无任何后续产品,但事实并非如此。高端处理器姗姗来迟,等它最终面世时,性能却不如人意。因此,8086 架构得以延续——它演化为 32 位处理器,最终又演化为 64 位。其名称不断更替(80186、80286、i386、i486、Pentium),但底层指令集丝毫未减。 ——Stephen P. Morse,8086 架构师 (Morse, 2017)

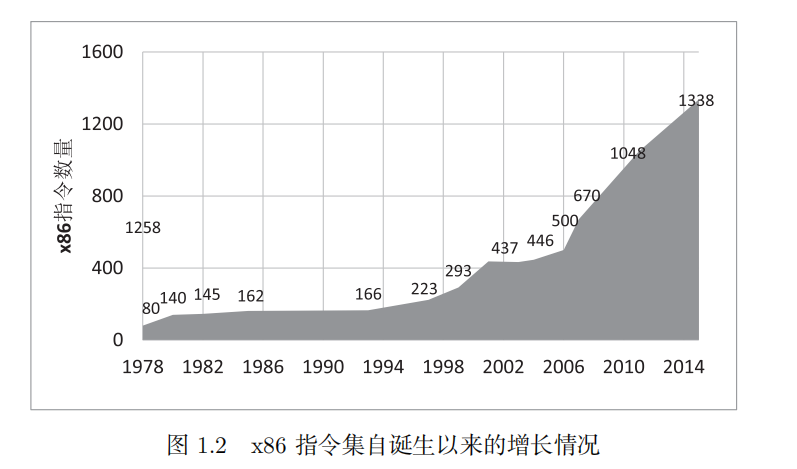

计算机体系结构的传统发展方式是增量型 ISA,这意味着新处理器不仅需要实现新的 ISA 扩展,还必须实现过去的所有扩展。其目的是保持向过去的二进制兼容性,使数十年前的二进制程序仍可在最新处理器上正确运行。出于市场营销的目的,新一代处理器的发布通常伴随着新指令的发布。这两点需求共同导致 ISA 的指令数量随时间流逝而大幅增长。图 1.2 展示了当今主流 ISA x86 的指令数量增长过程。x86 的历史可追溯到 1978 年,在漫长的生命周期中,它每个月大约增加 3 条指令。

x86 在 1978 年诞生时有 80 条指令,2015 年增长到 1 338 条,翻了 16 倍,并且仍在增长。但图中数据仍偏保守。一篇 2015 年的 Intel 博客指出,统计结果为 3600条指令 (Rodgers et al. 2017)。按这个数据,在 1978 年到 2015 年期间,x86 指令平均每 4 天增长 1 条。我们统计的是汇编语言指令,他们统计的也许是机器语言指令。增长的主要原因是 x86 ISA 通过 SIMD 指令实现数据级并行。

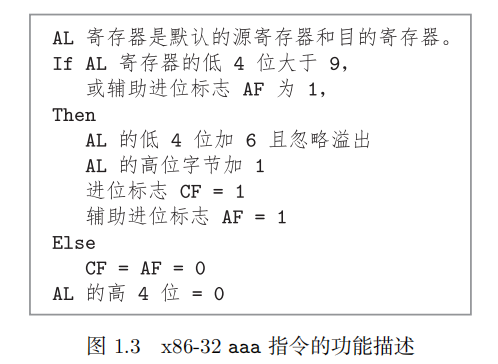

这种约定意味着 x86-32(我们用它表示 32 位地址版本的x86)的每款处理器都必须实现过去扩展的错误设计,即便它们已无意义。例如,图 1.3 列出了 x86 的 aaa(ASCII Adjustafter Addition)指令,该指令早已失去用处。

它以二进制编码十进制数(Binary Coded Decimal,BCD)的形式进行算术运算,但它已化为信息威廉希尔官方网站 的历史尘埃。x86 还有 3 条类似的指令,分别用于减法(aas)、乘法(aam)和除法(aad)。它们都是单字节指令,因此一共占用宝贵操作码空间的 1.6%(4/256)。

打个比方,假设一家餐馆只提供价格固定的套餐,最开始只有汉堡加奶昔的小餐。随着时间的推移,套餐中加入了薯条,然后是冰淇淋圣代,还有沙拉、馅饼、葡萄酒、素食意大利面、牛排、啤酒,无穷无尽,最后变成饕餮盛宴。食客能在这家餐馆找到他们过去吃过的任何一种食物(尽管这样没什么意义)。然而,这对食客来说是一个坏消息,他们每次的餐费将随盛宴加量而不断上涨。

除年轻和开放之外,RISC-V 还是模块化的,这与过去几乎所有 ISA 都不同。其核心是一个名为 RV32I 的基础 ISA,可运行完整的软件栈。RV32I 已冻结,永不改变,这为编译器开发者、操作系统开发者和汇编语言程序员提供了稳定的指令目标。模块化特性源于可选的标准扩展,硬件可根据应用程序的需求决定是否包含它们。利用这种模块化特性能设计出面积小、能耗低的 RISC-V 处理器,这对于嵌入式应用至关重要。RISC-V 编译器得知当前硬件包含哪些扩展后,便可为该硬件生成最优代码。一般约定将扩展对应的字母加到指令集名称之后,以指示包含哪些扩展。例如,RV32IMFD 在必选基础指令集(RV32I)上添加了乘法(RV32M)、单精度浮点(RV32F)和双精度浮点(RV32D)扩展。如果软件使用了一条未实现的可选 RISC-V 扩展指令,硬件将发生自陷,并在软件层执行该指令的功能。此特性属于标准库的一部分。

继续用我们刚才的比方,RISC-V 提供的是一份菜单,而不是一顿应有尽有的自助餐。主厨只需烹饪食客需要的食物,而不是每次都烹饪一顿大餐,食客也只需为他们点单的食物付费。RISC-V 无须仅为市场营销的热闹而添加新指令。RISC-V国际基金会决定何时往菜单中添加新的选择,经过由软硬件专家组成的委员会公开讨论后,他们才会出于必要的威廉希尔官方网站 原因添加指令。即使这些新的选择出现在菜单上,它们仍是可选的,不像增量型 ISA 那样成为未来所有实现的必要组成部分。

审核编辑:黄飞

-

处理器

+关注

关注

68文章

19265浏览量

229670 -

FPGA

+关注

关注

1629文章

21729浏览量

603037 -

加速器

+关注

关注

2文章

799浏览量

37842 -

微处理器

+关注

关注

11文章

2259浏览量

82407 -

RISC-V

+关注

关注

45文章

2271浏览量

46133

原文标题:图灵奖得主David Patterson:为什么要有 RISC-V

文章出处:【微信号:pzh_mcu,微信公众号:痞子衡嵌入式】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

加入全球 RISC-V Advocate 行列,共筑 RISC-V 的未来 !

RISC-V Summit China 2024 青稞RISC-V+接口PHY,赋能RISC-V高效落地

2024 RISC-V 中国峰会:华秋电子助力RISC-V生态!

2024 RISC-V 中国峰会:华秋电子助力RISC-V生态!

risc-v的发展历史

rIsc-v的缺的是什么?

为什么要有RISC-V

为何什么risc-v芯片比arm的效率高

RISC-V有哪些优点和缺点

国产RISC-V MCU推荐

解锁RISC-V威廉希尔官方网站 力量丨曹英杰:RISC-V与大模型探索

什么是RISC-V?RISC-V的关键威廉希尔官方网站

玄铁RISC-V生态大会深圳召开,达摩院引领RISC-V创新应用

RISC-V为何备受欢迎?

RISC-V为何备受欢迎?

评论