一推荐使用独立的上/下电时序管理芯片:SLG7RN46137V

1SLG7RN46137V芯片已经编程烧录完毕,直接贴片使用即可。

2高压伺服、交流伺服、变频器、压力变送器、中压伺服应用中,强烈推荐使用独立的上电时序管理芯片。

因为这类似系统的干扰信号相对比较大,如 “振铃干扰”、“电容退耦”等原因,导致弱电控制部分的控制信号,较容易被高压部分干扰。使用独立的上电/下电管理芯片,可以有效的规避这个问题。

3PLC控制器、PLC耦合器、一网到底PLC-DIDO模块,可以暂时不考虑。

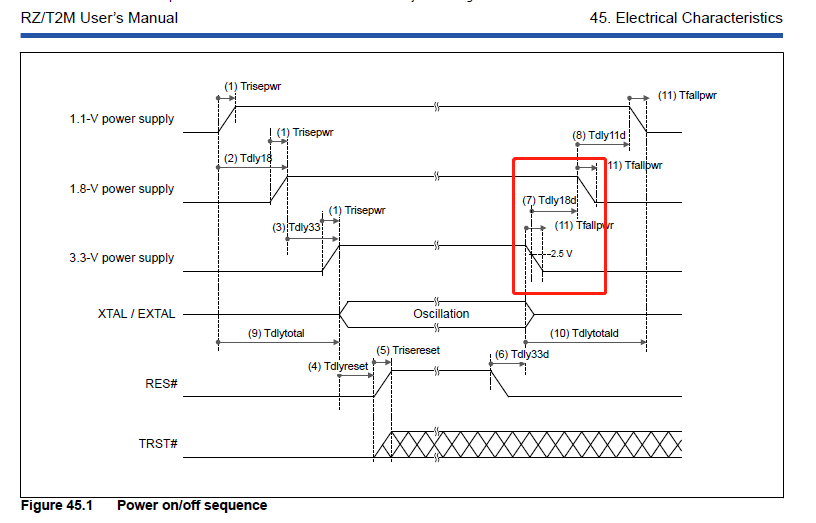

4RZ/T2M、RZ/T2L、RZ/N2L系列,上电和下电管理时序说明如下:

低电压的先上电,高电压的后上电;高电压的先掉电,低电压的后掉电。这样的时序要求其实对于分立式DCDC的供电设计逻辑控制是比较复杂的。

详细的时序图如下:

上图中红框里面的这个时序,是最为关键的。如果1.8v跌落后,3.3v依然持续供电,会导致RZ/T2M、RZ/N2L、RZT2L芯片损坏。

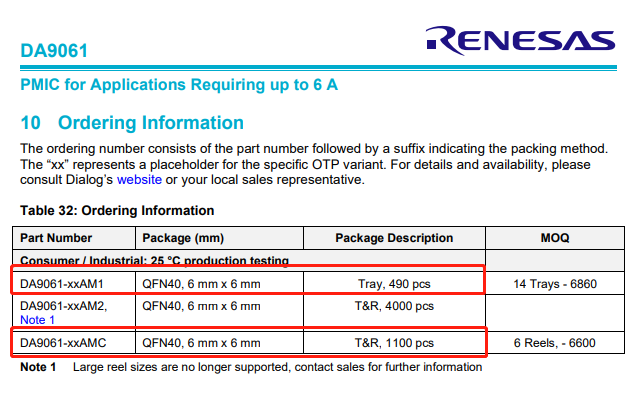

二推荐使用的PMIC:DA9061-16AM1 & DA9061-16AM

1AM1和AMC仅仅是芯片包装方式的不同。芯片本身并未明显不同。

2早期的这份文档(2.7以及之前),此处描述有明显错误。

DA9061-00AMx,为空白片。

DA9061-16AMx,为编程片,无需烧录,购买后直接焊接。上电时序和电源管理逻辑,已经在出厂之前烧录到了芯片内部。

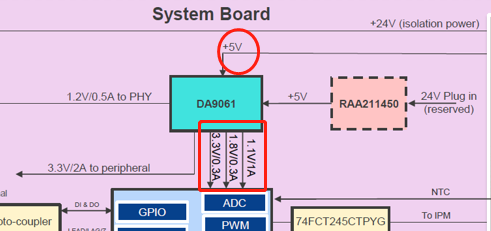

应用细节描述

RZ/T2M和RZ/N2L芯片内部的供电结构的原因,导致3.3v,1.8v,1.2v的上电时序有较为严格的时序要求。

PMIC的上电和掉电时序,是完全可以由内部OTP控制的。目前PMIC的完整料号是DA9061-16AM1,其中16AM1代表这个OTP已经被烧录,并可以支持RZ/T2M、RZ/N2L。

下单和订购样品的时候,直接选择DA9061-16AM1或者DA9061-16AMC即可。不要订购空白片DA9061-00AM1。

此设计已经在瑞萨中国的EVK上进行过验证。不用担心匹配性、稳定性问题。

三IAR编译环境使用小技巧

1IAR打“编译”专用补丁

如您不评估Profinet,请使用IAR 9.30.1或以上,比如9.32.1。官方例程均基于该版本(IAR 9.30.1),可以跳过下面的所有叙述。

a) IAR85和IAR92,无法编译R52 CORE的 RZ/T2M和RZ/N2L。所以需要打补丁。

b) IAR9.3x 版本,可以编译RZT2M和RZN2L。

①如果使用IAR85和IAR92,需要手动打补丁进行编译。

②实测,IAR 8.5.x,IAR 9.2.X系列,打过补丁后,均可正常编译出 可执行文件。

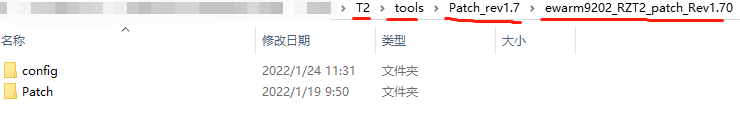

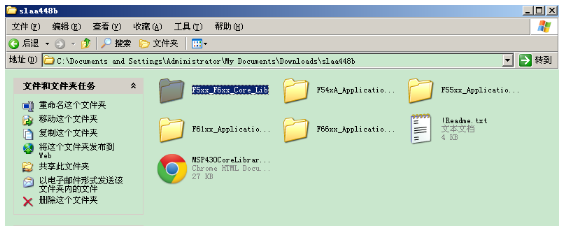

③编译器补丁如下。

④打补丁的方法。

Please copy and overwrite the files of "config" and "Patch" to the

把这两个文件复制到

注意:这个编译补丁,和PN demo的运行补丁,不是同一个概念,请勿混淆。

2编译例程不通过时,请尝试以下修改和对策

● 编译路径太深,或者某一级的目录的名字太长。

●编译的目录中有文中路径。

●把需要编译的目录,复制到某个盘符的根目录,或者桌面。

● ECAT例程,需要按照ecat例程中的pdf文件指导,自己生成ecat源码。

3如何简单的判断是否堆栈溢出

①首先找到工程目录下的startup_ram.asm文件,这个文件在RZT1上是loader_init.asm文件。

②找到下面的类似于clear bss段。这个区域在RZT1上是“loader_bss_init:”部分。

③加入如下代码:给每个stack设置初始值为特定的 0x55,0x66,0x77等。

原理:一旦程序异常复位,并进入“abort handler”或者“hard fault”后,可以立刻查看如下堆栈段,是否有被“撑爆”的情况。即如果堆栈段 顶端出现非“0x55,0x66,0x77”的数据,即可认为栈溢出 出现过。

左右滑动查看完整内容

;-----------------------------------------add stack init to 0x55----------------------------------- cstack_set55: ldr r0, =0x55555555 ldr r1, =SFB(CSTACK) ldr r2, =SFE(CSTACK) cmp r2, r1 beq svcstack_set66 set_loader_cstack: strb r0, [r1], #0 add r1, r1, #1 cmp r2, r1 bne set_loader_cstack dsb ; Ensuring data-changing svcstack_set66: ldr r0, =0x66666666 ldr r1, =SFB(SVC_STACK) ldr r2, =SFE(SVC_STACK) cmp r2, r1 beq IRQSTACK_set77 set_loader_svcstack: strb r0, [r1], #0 add r1, r1, #1 cmp r2, r1 bne set_loader_svcstack dsb ; Ensuring data-changing IRQSTACK_set77: ldr r0, =0x77777777 ldr r1, =SFB(IRQ_STACK) ldr r2, =SFE(IRQ_STACK) cmp r2, r1 beq FIQSTACK_set88 set_loader_irqstack: strb r0, [r1], #0 add r1, r1, #1 cmp r2, r1 bne set_loader_irqstack dsb ; Ensuring data-changing FIQSTACK_set88: ldr r0, =0x88888888 ldr r1, =SFB(FIQ_STACK) ldr r2, =SFE(FIQ_STACK) cmp r2, r1 beq UNDSTACK_set99 set_loader_fiqstack: strb r0, [r1], #0 add r1, r1, #1 cmp r2, r1 bne set_loader_fiqstack dsb ; Ensuring data-changing UNDSTACK_set99: ldr r0, =0x99999999 ldr r1, =SFB(UND_STACK) ldr r2, =SFE(UND_STACK) cmp r2, r1 beq ABTSTACK_setAA set_loader_undstack: strb r0, [r1], #0 add r1, r1, #1 cmp r2, r1 bne set_loader_undstack dsb ; Ensuring data-changing ABTSTACK_setAA: ldr r0, =0xAAAAAAAA ldr r1, =SFB(ABT_STACK) ldr r2, =SFE(ABT_STACK) cmp r2, r1 beq jump_loader_init2 set_loader_abtstack: strb r0, [r1], #0 add r1, r1, #1 cmp r2, r1 bne set_loader_abtstack dsb ; Ensuring data-changing ;---------------------------------------end---------------------------------------

审核编辑:汤梓红

-

控制器

+关注

关注

112文章

16350浏览量

177949 -

变频器

+关注

关注

251文章

6553浏览量

144613 -

IAR

+关注

关注

5文章

351浏览量

36673 -

时序图

+关注

关注

2文章

58浏览量

22443 -

DCDC

+关注

关注

29文章

816浏览量

71280

原文标题:RZ/T2M RZ/N2L RZ/T2L系列应用心得(3-上)

文章出处:【微信号:瑞萨MCU小百科,微信公众号:瑞萨MCU小百科】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

在IAR软件编译环境编译,出现中断标志警告如何解决?

IAR环境配置

如何用IAR6.3编译环境中ucos在msp430上的移植的详细中文资料

IAR ARM集成开发环境学习教程

IAR编译环境使用小技巧(1)

IAR编译环境使用小技巧(1)

评论