接上文提到有没有更简便的方法可以不做那么复杂的弯针模型呢?模型建立越接近真实情况固然越准确,但是耗费时间,准确和效率找到平衡才是智者所为。

打个比方,当学习分数达到一定的程度,每提高一点,都必然要耗费心力。但在这个地方耗费心力,其实是透支未来。这也好比,一天挣100,如果要挣110,要加班3小时。那还不如省下3小时去学习,综合能力提升了自然可以找200一天的工作。

那我们就来看看是否有效率更高的方法。

2.5D仿真

SIWave或者PowerSI这类软件可以解这个问题吗?要找简单方法,当然也要尝试看看。

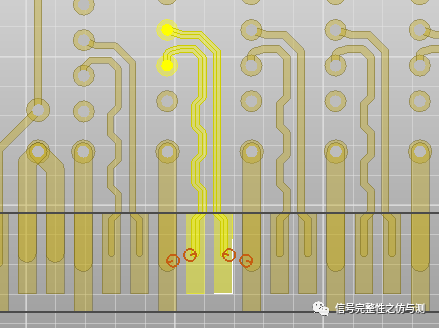

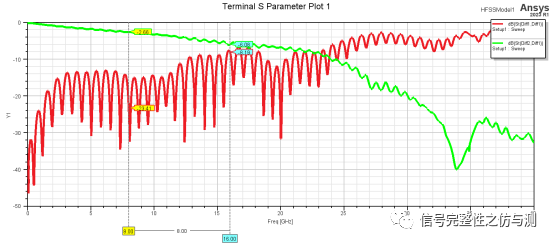

1.SIWave中直接下Port

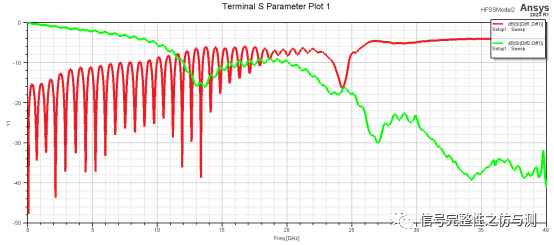

求解用时8分钟,谐振影响非常大,显然结果不可用,方法不可取。

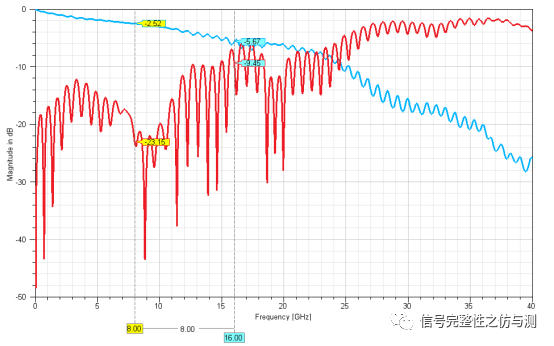

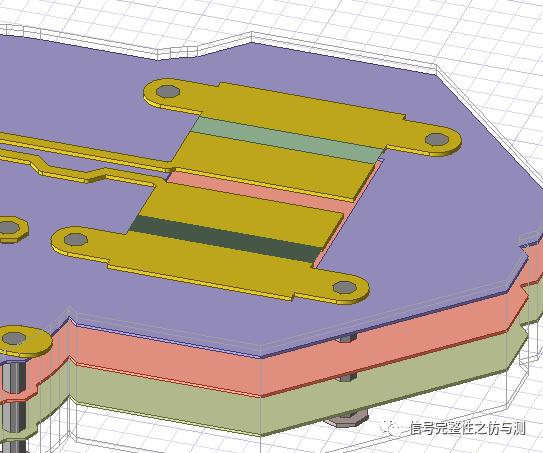

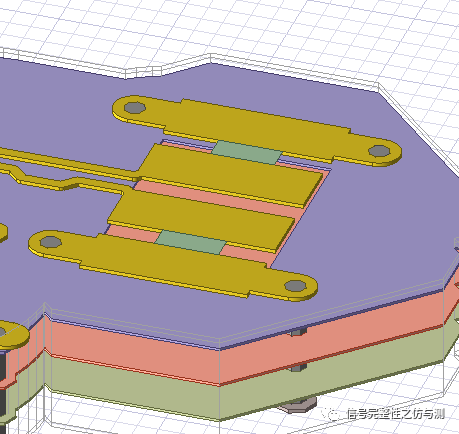

2.GND做Group

S21在10G以内很接近了,10G之后震荡加大,S11差异还是较大。PCIe Gen3以内用此方法还勉强可以接受。

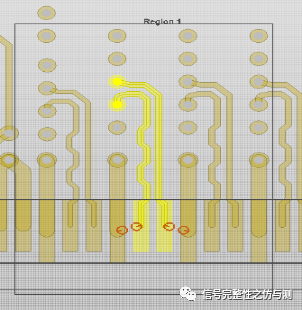

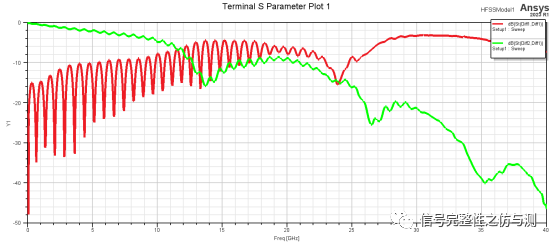

3.SIWave with HFSS Region

看结果有点出乎意料,实则情理之中。SIwave with HFSS Region并不是万金油。解线路中的过孔结构没有问题,但是这种连接器结构,Region部分导入HFSS后Port依然是Circuit Port。

由此可见,2.5D软件解金手指结构并不可取,Port的影响是主要因素。

高速SerDes互连信号中长链路S参数提取的四种方法中也提到过SIWave with HFSS Region在几种方法对比中表现是最差的,并没有官方宣传的那么好,希望是我使用不当造成的,慎用!

HFSS中快速Port验证

①Coax Port

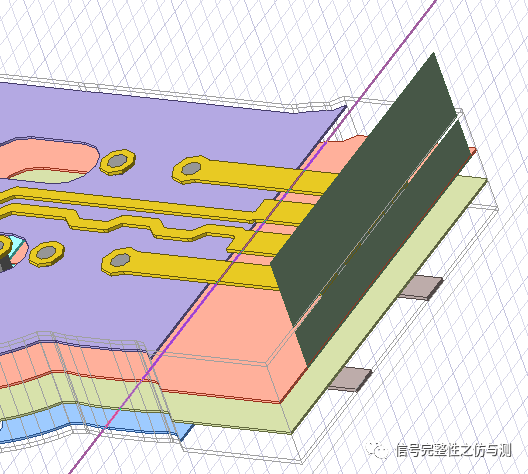

在SIwave中直接长焊球,生成Port,快速简单,再导入HFSS,省去建模的繁琐。

此种解法在35G左右有谐振,整体上比在SIwave中求解靠谱多了。计算时间1.5小时。

②直接下Lumped Port

此解法与SIwave结果类似,不可取。

③减小Lumped Port尺寸

没有改善,因此直接Lumped Port方式可以排除。

④Wave Port

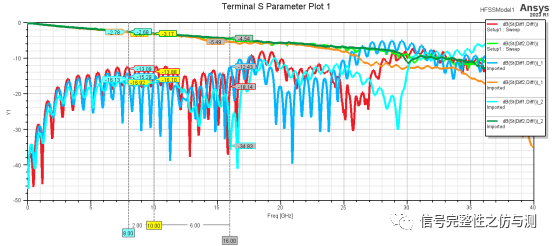

结果符合预期,比实际应用情景略理想一点。

⑤非直接下Port,利用理想PEC建立Lumped Port

对比发现,方案④⑤是最接近真实情况的。放在一起比较,④⑤的S21曲线几乎完全一致。同时⑤的S11也是最接近真实情况的。而且⑤比④操作起来也更简单。

方案①与真实情况对比,20GHz以内没有问题,高频差距较大。

总结:对于PCIe Gen5金手指结构的仿真,要想准确,那就要加入连接器模型,稍微偷偷懒的方案首选⑤,其次④。继续偷懒的话,PCIe Gen4可以选方案①。

如果还要追求速度,PCIe Gen3以内可以使用SIwave GND Group。

刚才也强调,是要在精度和效率上找平衡,方案⑤到底可不可取?仿真的结果说到底还是仿,仿的结果取决于人和软件,测过才知道。

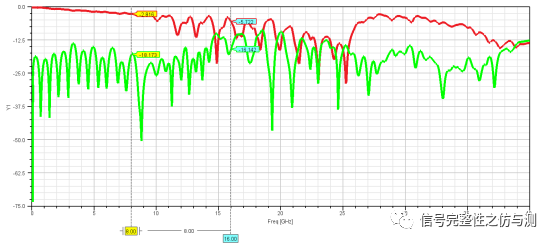

测试验证

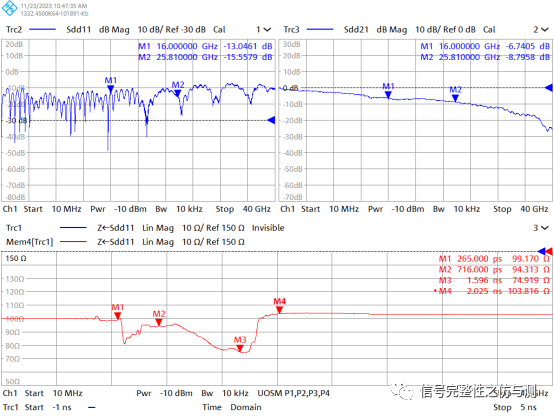

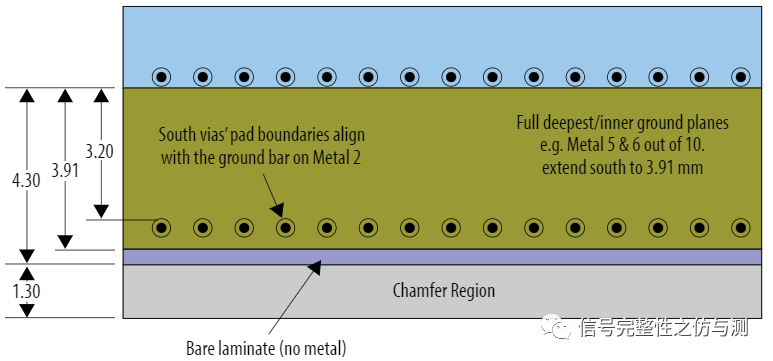

取下子卡上的PCIe连接器,露出焊盘,随机测试一组差分信号。

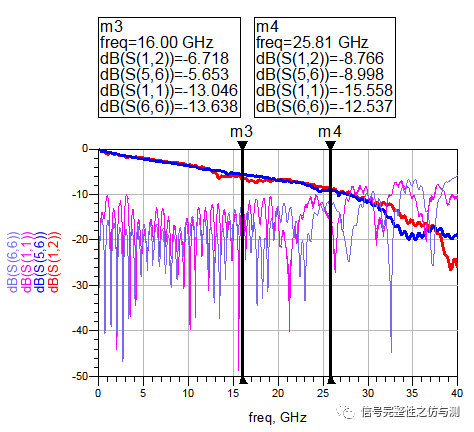

16GHz -6.74dB损耗

使用上述⑤的Port建立方法挑选测试的这对差分信号进行仿真

16GHz -5.65dB损耗

仿真与测试相比,趋势是对得上的,但是还相差了1.1dB,S11也比实际测试的理想很多。

1.1dB什么概率呢,差不多在968的板材上还能走1100mil长度走线,988板材还能走1400mil走线。

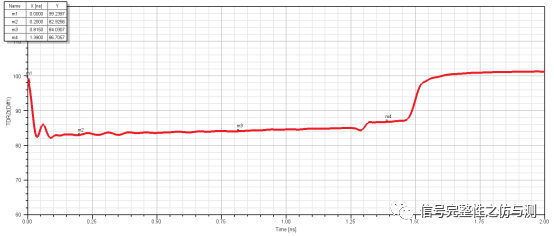

找找原因不难发现,仿真的时候我们默认阻抗都是一致性的,看上图测试结果就会发现PCB板厂加工的阻抗非常差。内层走线能从94一路滑坡到74。实际设计是这样的。

仿测拟合

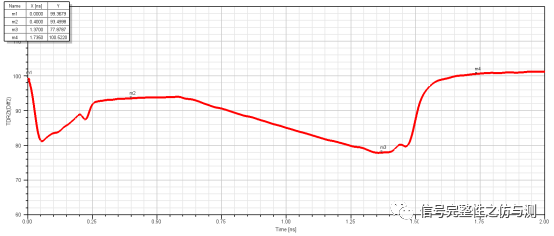

为了证实一下阻抗的影响,故意做了一组接近实测阻抗趋势的同一对走线。

重新按照方法⑤仿真

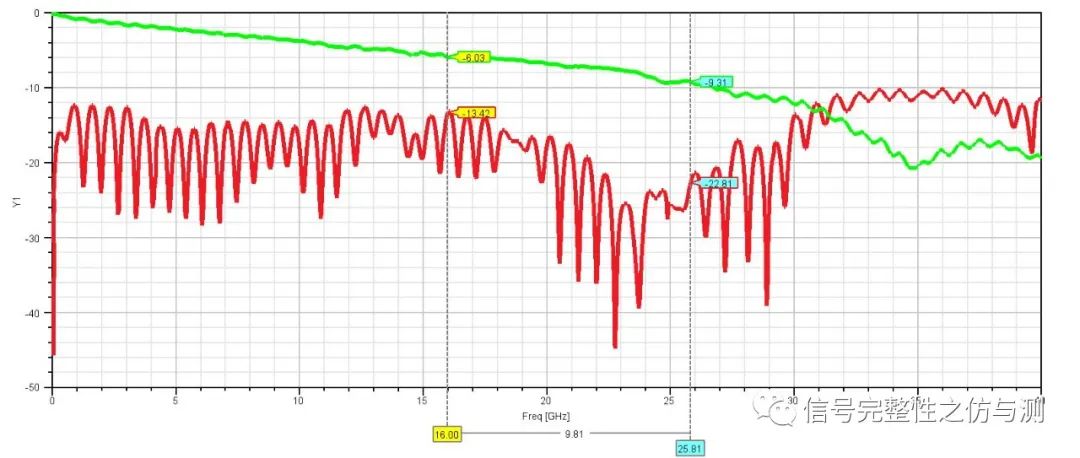

16GHz -6.03dB损耗

16GHz损耗变差了,S11也变差了,更接近实测的结果

较真地问一下为什么还有差别?

影响阻抗的因素有很多,这里也只是仿照测试结果的趋势随便改变了一组参数,具体板厂是怎么加工的偏差尚不知道,因此仿真与测试还有差异很正常。

这里要证明的是仿真总是理想的,结果如何测过才知道。

-

PCIe

+关注

关注

15文章

1239浏览量

82660 -

谐振

+关注

关注

5文章

372浏览量

39588 -

模型

+关注

关注

1文章

3244浏览量

48845 -

金手指

+关注

关注

0文章

37浏览量

11662 -

GND

+关注

关注

2文章

539浏览量

38722

发布评论请先 登录

相关推荐

针对PCIe Gen5 M.2 NVMe SSD的L1.2低功耗测试

PCIe Gen5 Card金手指仿真与设计(上)

为什么PCIe Gen3/Gen4不使用CXL

PCIe Gen5主机更新

思尔芯首款支持PCIe Gen5原型验证EDA工具上市

思尔芯首款支持PCIe Gen5原型验证EDA工具上市,高性能加速AI设计

详细探讨适用PCIe Gen5的PCB材料以及其中的重要作用

三星PCIe Gen5 SSD满足大负荷企业级工作环境

SK海力士首发Gen5 NVMe固态硬盘

HighPoint发布商用PCIe Gen5解决方案,最大可达960TB SSD容量

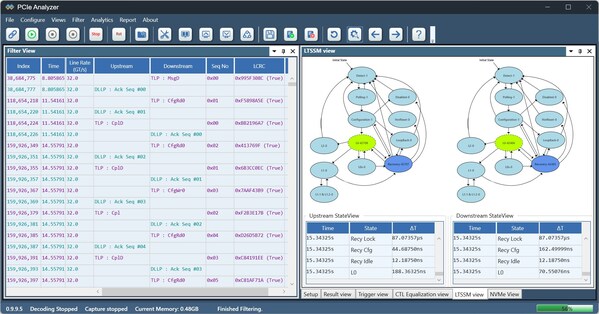

Prodigy Technovations推出功能强大的PCIe Gen5协议分析仪

CDCDB800/803超低附加抖动、8路输出PCIe Gen1至Gen5时钟缓冲器

PCIe Gen5 Card金手指仿真与设计(下)

PCIe Gen5 Card金手指仿真与设计(下)

评论