共读好书

魏红军 谢振民

摘要:

电化学沉积威廉希尔官方网站 ,作为集成电路制造的关键工艺威廉希尔官方网站 之一,它是实现电气互连的基石,主要应用于集成电路制造的大马士革铜互连电镀工艺和后道先进封装 Bump、RDL、TSV 等电镀工艺。受 WLP、2.5D、3D、SIP 等先进封装威廉希尔官方网站 的推动,未来 3 年市场空间可达 15~20 亿美元。

0 引言

电 化 学 沉 积 技 术, 简 称 ECD(Electrical Chemical Deposition)威廉希尔官方网站 ,也是应用于半导体相关威廉希尔官方网站 行业的电镀威廉希尔官方网站 ,作为集成电路制造的关键工艺威廉希尔官方网站 之一,它是实现电气互连的基石。电化学沉积威廉希尔官方网站 主要应用于集成电路制造的大马士革铜互连工艺制程和后道先进封装 Bump、RDL、TSV 等工艺制程,也可应用于化合物、MEMS 中深孔加工、金凸块、金属膜沉积等领域。

1 电化学沉积威廉希尔官方网站 在铜互连中的应用

随着晶体管尺寸不断缩小,进入 130 nm 制程以后,铝互连工艺已经不能满足集成电路集成度、速度和可靠性持续提高的需求。与铝相比,铜的电阻率只有铝的一半左右,较低的电阻率可以减少金属互连的 RC 延时,可以降低器件的功耗,并且铜的电迁移特性远好于铝,因此,铜已逐渐取代铝成为金属互连的主要材料。

由于铜很难进行干法刻蚀,因此传统的金属互连工艺已不再适用,拥有镶嵌工艺的镀铜威廉希尔官方网站 成为铜互连的主要制备工艺,业界也称为大马士革铜互连工艺。

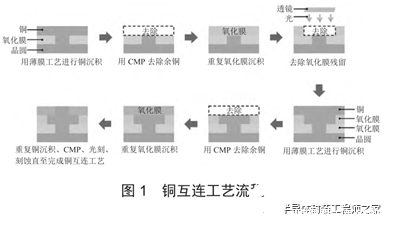

首先沉积阻挡层 TaN/Ta,防止铜原子向介质层扩散,以免降低介质层的绝缘属性;之后在阻挡层上沉积铜种子层,然后进行电镀填充,如图 1 所示 ;填充后多余的铜可以用化学机械抛光(CMP)方法去除 ;完成后沉积氧化膜,多余的氧化膜采用光刻和刻蚀工艺去除;整个过程需要不断重复直至完成铜互连布线为止。目前铜互连层最多可达 15层以上,据台积电报道,在其最先进的 5 nm 芯片中,铜互连线长度可以达到 100 km。

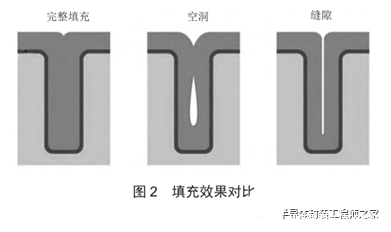

完全填充高深宽比的互连沟槽是大马士革互连工艺最大的挑战,如图 2 所示,如不能很好的控制电镀工艺过程,则会形成空洞或缝隙,降低芯片的电性能和可靠性,并影响芯片制造工艺的产品良率。

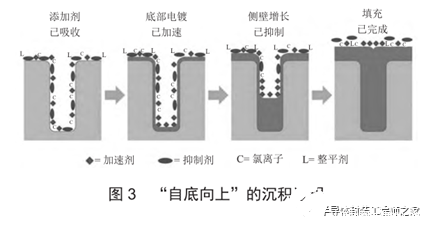

目前铜互连电镀主要采用硫酸铜工艺体系,电镀液成分主要包括硫酸、铜离子、氯离子、加速剂、抑制剂和整平剂等六种组分。如图 3 所示,理想的填充过程是自底向上的沉积过程,这就需要镀铜溶液中抑制剂、加速剂等不同添加剂的合理配比,达到“沟槽内加速、沟槽口抑制”的效果,从而实现低电阻率、无空洞和高可靠性的铜布线结构。

电镀之后的铜晶粒很小,必须通过退火工艺来增加晶粒大小、降低电阻、增加电迁移可靠性以及增加 CMP 的稳定性。但过度的退火会增加 CMP之后的缺陷,所以合适的退火方式将非常重要。

2 电化学沉积威廉希尔官方网站 在先进封装中的应用

随着集成电路工艺尺寸不断缩小,即将接近物理极限,先进封装威廉希尔官方网站 被推向舞台的正中央,WLP、2.5D、3D、SIP 等威廉希尔官方网站 的发展成为延续摩尔定律的最佳选择。实现芯片 Z 方向电气连接的硅通孔威廉希尔官方网站 (TSV),实现倒装或堆叠芯片之间电气连接和应力缓冲的凸点威廉希尔官方网站 (Bump),实现芯片 XY 平面电气延伸和互连的金属层重布线威廉希尔官方网站 (RDL),这三者即是后摩尔时代集成电路先进封装威廉希尔官方网站 的关键要素。

2.1 硅通孔威廉希尔官方网站

TSV(through silicon via)威廉希尔官方网站 是穿透硅通孔威廉希尔官方网站 的英文缩写,简称硅通孔威廉希尔官方网站 ,是三维集成电路中堆叠芯片实现互连的一种威廉希尔官方网站 解决方案。它是在芯片和芯片之间、晶圆和晶圆之间制作垂直导通,通过 Z 方向通孔实现芯片之间的互连。TSV 威廉希尔官方网站 能够使芯片在三维方向堆叠的密度最大,芯片之间的互连线最短,外形尺寸最小,大大改善芯片速度和低功耗的性能。

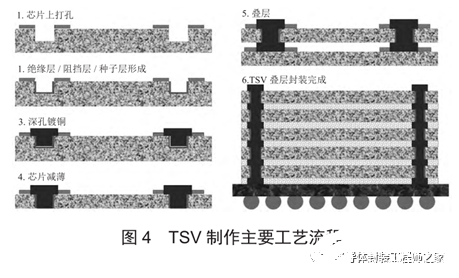

如图 4 所示,TSV 主要工艺流程包括硅通孔的制作,绝缘层、阻挡层、种子层的沉积,铜的电镀填充,通过 CMP 去除多余金属,晶圆减薄,晶圆键合等;在整个 TSV 制造工艺中,硅通孔的镀铜填充是目前的关键威廉希尔官方网站 难点之一,与铜互连电镀相似,同样需要自底向上的沉积过程,但 TSV 电镀的尺寸更大,通常需要更长的沉积时间,更高的电镀速率以及多个工艺步骤。

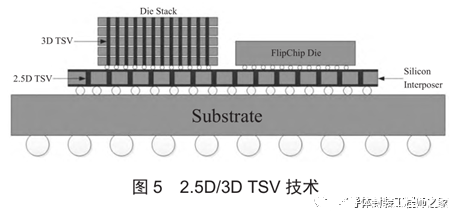

TSV 按照集成类型的不同分为 2.5D TSV 和3D TSV,2.5D TSV 指的是硅转接板上的 TSV,3DTSV 是指芯片上制作硅通孔,连接上下层芯片,如图 5 所示。

TSV 是 3D 系统集成的关键威廉希尔官方网站 和发展趋势,目前已经可以实现深宽比为 10∶1 的 TSV 结构,且向着更高深宽比发展。随着工艺的提升,硅通孔的孔径越来越小,密度越来越大,目前最先进的TSV 工艺,可以在 1 mm 2 的芯片上制作高达 10 万个以上硅通孔,从而支撑更高密度的芯片互连,同样对 TSV 的电镀填充也提出了更高的工艺要求。

2.2 凸点威廉希尔官方网站

作为金属凸点,Bump 对芯片来说起着电气互连和应力缓冲的作用,从 Bondwire 工艺发展到FlipChip 工艺,再到 3D 堆叠芯片工艺,Bump 至关重要。

Bump 形状有很多种,最常见的为球状和柱状,也有块状等其它形状。材料一般为 Cu、Au、Ni、Ag-Sn 等,有单金属的凸点,也有合金凸点,最常用的凸点材料是 Cu 和 Au。

电镀法制作凸点是目前最为普遍且工艺成熟的凸点制作方法,该方法不仅加工工序少,工艺简便易行,适于大批量生产,且可制作各类凸点,IC芯片上的 I/O 数、焊区尺寸大小及凸点节距均不受限。

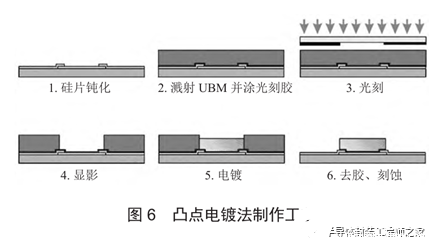

凸点电镀法制作工艺流程如图 6 所示,先将硅片进行钝化,然后蒸发 / 溅射 UBM 凸点下金属层,接下来进行光刻、显影,就形成了所需的电镀窗口,然后进行电镀工艺,最后去除光刻胶、刻蚀 UBM金属层。

2.3 重布线威廉希尔官方网站

重 布 线 技 术, 简 称 RDL(Redistribution Layer),起着 XY 平面电气延伸和互连的作用。RDL 威廉希尔官方网站 的核心是在晶圆表面沉积金属层和介质层并形成相应的金属布线图形,对芯片的 I/O 进行重新布局,根据后续封装工艺需求,将其布局到新的、更为宽松的区域,并可形成面陈列排布。

在 2.5D IC 集成中,除了硅转接板中的 TSV 威廉希尔官方网站 外,RDL 威廉希尔官方网站 同样关键,通过 RDL 将电气连接分布到不同的位置,从而将硅转接板上方芯片的凸点和转接板下方的凸点连接。

在 3D IC 集成中,对于同种芯片来说,上下堆叠直接通过 TSV 就可以完成电气互连,对于异质异构芯片,则需 RDL 将芯片的 I/O 重新布局进行对准,从而完成芯片的互连。

在 FIWLP、FOWLP 先进封装中,RDL 是最为关键的威廉希尔官方网站 ,通过 RDL 将 I/O 进行 Fan-In 或者Fan-Out,形成不同类型的封装形式。Fan-Out 扇出型封装有两大分支:扇出型晶圆级封装和扇出型面板级封装。对于板级封装来说,由于面板的大尺寸和更高的载具使用率,带来远高于晶圆级封装的规模经济效益,作为其核心的 RDL 威廉希尔官方网站 也得到了业界更多的关注。

随着工艺威廉希尔官方网站 的发展,通过 RDL 形成的金属布线的线宽和线间距也越来越小,从而提供更高的互连密度。目前重布线层 RDL 多采用电化学沉积的方式来完成。

3 电化学沉积工艺设备国内外厂商情况及行业前景

国外厂商方面,前道铜互连电镀设备主要被美国 Lam 垄断 ;后道先进封装电镀设备厂商主要包括美国 AMAT、美国 Lam、日本 EEJA、新加坡ASM 等。

国内厂商方面,主要供应商上海盛美,科创板上市公司,电镀设备营业收入从 2018 年 1200 万增至 2021 年 2.74 亿元,2021 年实现量产,交付 20台电镀设备,2022 年截止 5 月获得 31 台批量订单,其中前道铜互连电镀设备最高可以用于 28 nm 工艺节点。

2021 年全球半导体设备销售额突破 1 000 亿美元;其中ECD设备市场约10亿美元,受WLP、2.5D、3D、SIP 等先进封装威廉希尔官方网站 的推动,未来 3 年市场空间可达 15~20 亿美元。

半导体产业发展的决定性因素在于其生产设备,其产业制高点的竞争,归根结底还是装备制造业的竞争,因此有“一代设备、一代工艺、一代产品”之说。装备制造也正是我国半导体产业中最薄弱的环节,作为芯片制造的基石,对我国半导体产业链安全具有重大意义。

近几年以来的全球芯片短缺,引发全球晶圆厂尤其国内掀起扩产潮,对半导体设备的需求再次激增,作为上游的半导体设备行业持续增长,在行业扩容和国产替代的双重作用下,正式步入发展的“黄金时代”。

审核编辑 黄宇

-

芯片

+关注

关注

455文章

50756浏览量

423343 -

集成电路

+关注

关注

5387文章

11540浏览量

361705 -

电化学

+关注

关注

1文章

322浏览量

20596

发布评论请先 登录

相关推荐

电化学沉积威廉希尔官方网站 在集成电路行业有哪些应用呢?

新型铜互连方法—电化学机械抛光威廉希尔官方网站 研究进展

18650锂电池化学电源测试威廉希尔官方网站 的发展历程

基于电化学传感器的Arduino兼容电化学气体检测电路CN0357

电化学传感器的发展怎么样?

一文了解湿法加工中的电化学效应

电化学沉积威廉希尔官方网站 在集成电路行业的应用

电化学沉积威廉希尔官方网站

在集成电路行业的应用

电化学沉积威廉希尔官方网站

在集成电路行业的应用

评论