文章来源:半导体综研

文章作者:关牮 JamesG

导 读

芯片的7nm工艺我们经常能听到,但是7nm是否真的意味着芯片的尺寸只有7nm呢?让我们一起来看看吧!

下图是一张小编从网上找到的一个经典的逻辑芯片的结构剖面图。从图上大家可以看到,半导体芯片/器件的结构非常复杂,是由很多层的结构叠加而成的:

最下面的FOEL(Front End of Line)是晶体管结构部分

其上面的BOEL(Back End of Line)是用金属线(铜线为主)把各个晶体管连接起来的结构部分

最上面的则是把信号、电源管脚引出来的部分。这部分通常不是在晶圆厂加工制造,而是在封装厂进行

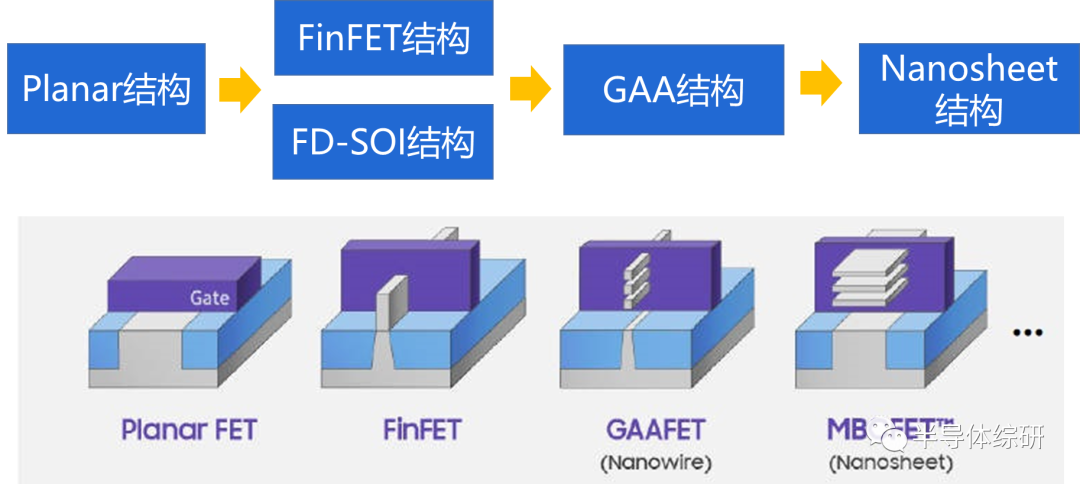

晶体管/MosFET的结构实际上也是在发生变化的。一般而言,到28nm为止,晶体管的结构通常还是下图中的平面结构:Planar结构。而从20nm开始,晶体管进入了立体结构时代,最典型的就是下图中的FinFET结构。而关于晶体管线宽概念的混淆,也是从这里开始的

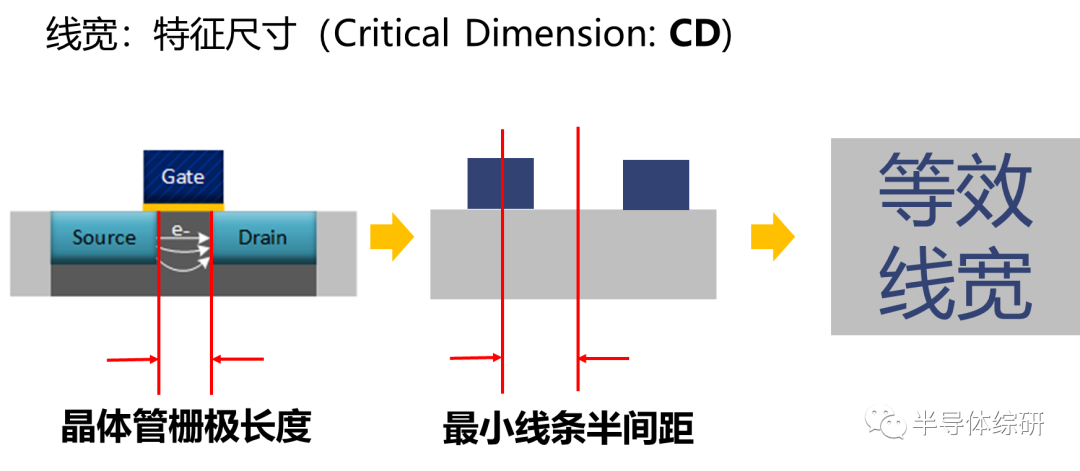

一般所谓线宽,在行业内的标准称谓是CD/Critical Dimention,中文直接翻译就是特征尺寸。它指代的是芯片结构里最小的线条宽度,通常就是栅极的长度(见下图最左)

后来栅极的长度已经不是最小的线宽了,无法准确代表工艺节点。于是行业内开始用最小线宽半间距来代表线宽,也就是所有图形里最小的两根相邻线条中心位置距离的一半。这个数值代表了芯片结构里的最高图形分辨率

目前***的威廉希尔官方网站 参数里的分辨率,其实说的就是这个最小线条的半间距(见下图中间)

但是到了FinFET工艺时代,其实限于***的威廉希尔官方网站 能力。我们能够做到的实际图形分辨率并没有大幅提升,但是晶体管结构变化以后,其实际的密度确实也大幅度提升了。那该如何评价其工艺水平呢?

于是,晶圆厂们“灵机一动”,想出了等效线宽的概念

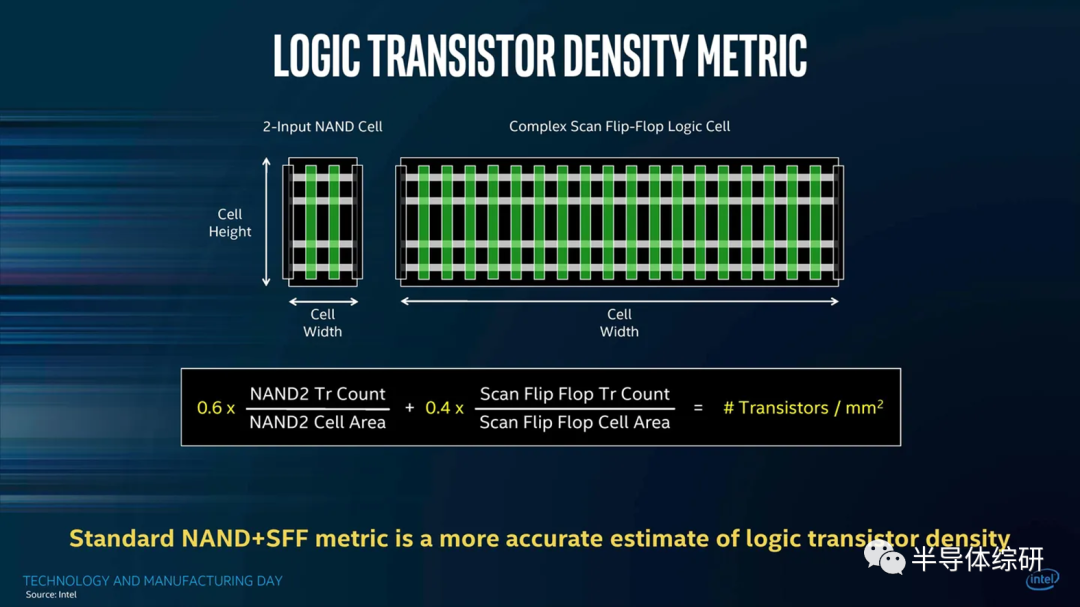

下图是Intel的威廉希尔官方网站 资料上公布的标准晶体管密度的计算方法。简单来说,就是用一个标准的与非门(包含4个晶体管)的面积来计算一次晶体管密度,然后再用一个标准FlipFlop触发器(包含6个与非门)电路计算一次平均晶体管密度。然后将两个密度结果加权平均一下,就可以得到当前工艺威廉希尔官方网站 下在单位面积的晶圆上能做几个晶体管

然后用这个密度值对比平面晶体管的密度,然后计算出等效的线宽值来。所以这样一来,虽然我们不能大幅度缩小实际的图形线宽,但是可以通过器件结构的变化缩小晶体管的面积、提升密度来得到一个等效的“小线宽”

从20nm的 FinFET工艺开始,我们看到的所谓的线宽都是如此

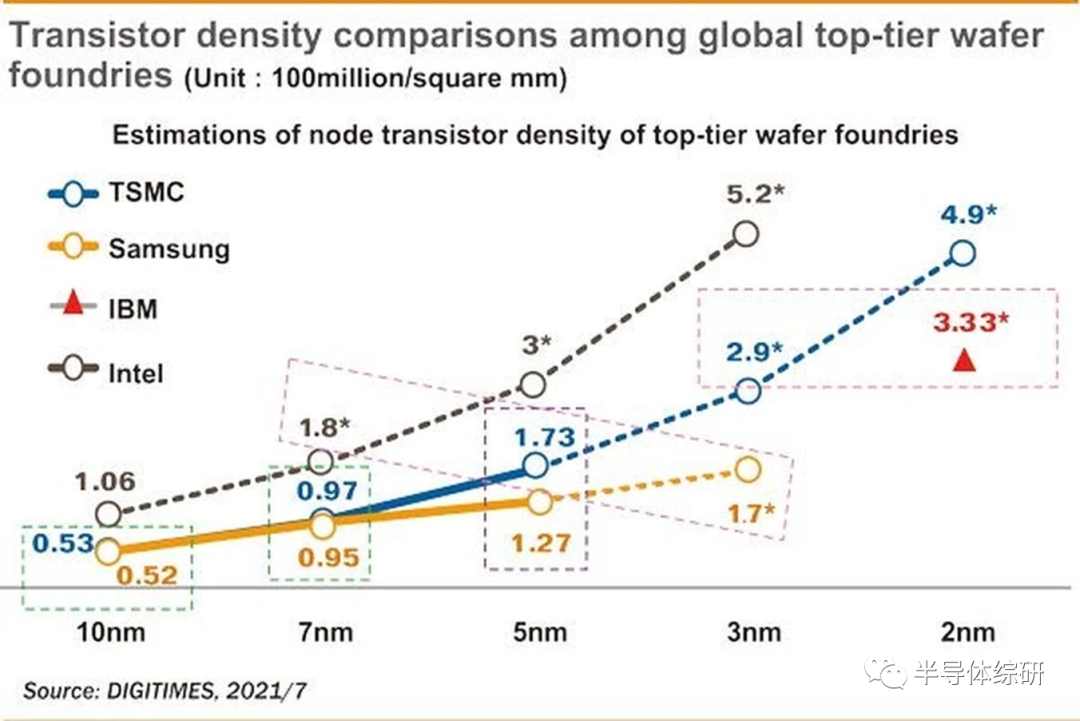

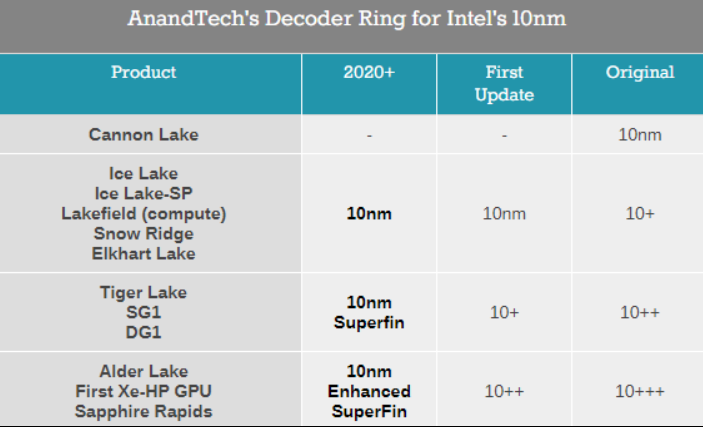

当然,由于采用了等效换算的方法,这就给各个晶圆厂提供了浑水摸鱼的机会。利用算法上的投机取巧耍鸡贼,各家所谓同一工艺节点芯片的实际晶体管密度是有差别的,而且差别还不小

从下图可以看到:虽然同样叫10nm节点,Intel的晶体管密度做到了1.06亿个/平方毫米,而TSMC和三星的密度都只有0.53和0.52,相差几乎一倍

而在之后的7nm5nm节点上,同样情况依旧存在。可见,在取名字上,老实的Intel吃了一个大亏,被另外两家给欺负了

既然工艺节点的命名不靠谱,那行业内是用什么方法来衡量一个具体工艺的水准能力的呢?

事实上,在FinFET工艺中用来判断具体工艺威廉希尔官方网站 的指标很多,不过多数情况下大家记得和理解两个名词就好了:

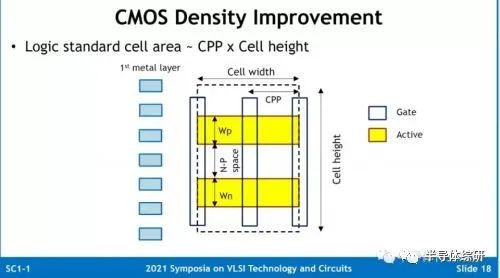

1) CPP:Contacted Poly Pitch 接触孔的多晶硅栅极间距

2) MxP:Metal Pitch 金属线的间距(通常指第一层或第二层的金属线间距)

CPP反映了整个晶体管单元(CELL)的宽度;而MxP是用来衡量晶体管单元高度的单位,通常被称为Track。晶体管的高度是MxP的几倍,就叫几个Track,或者几个T

这两个指标就代表了晶体管的大小,也就等于确定了晶体管的单位面积密度。下图是一个参考:

另外,还有一个指标是鳍片的间距(Fin Pitch)。M2P和Fin Pitch的比例称为Gear Rate

好了,看到这里你大体就对先进工艺里的线宽有一个大体认识了

-

芯片

+关注

关注

455文章

50714浏览量

423147 -

半导体

+关注

关注

334文章

27290浏览量

218086 -

晶圆

+关注

关注

52文章

4890浏览量

127931 -

晶体管

+关注

关注

77文章

9682浏览量

138080 -

7nm

+关注

关注

0文章

267浏览量

35332

原文标题:关于芯片的7nm到底是个啥

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

一文详解芯片的7nm工艺

一文详解芯片的7nm工艺

评论