今天想来聊一下芯片设计中的一个重要macro——PLL,全称Phase lock loop,锁相环。我主要就介绍一下它是什么以及它是如何工作的。

芯片的时钟可以自己产生,可以由几个反相器接在一起构成一个简单的振荡器产生时钟,它的频率可以到很快的速度,但是时钟周期却没那么固定,一会快一会慢的。

而从芯片外面来的晶振一般具有稳定的时钟周期,但频率只能是在兆赫兹的量级。PLL就是利用外部晶振作为参考时钟,来输出一个周期稳定的高频率的时钟,这个时钟供芯片的时序电路使用。

可以说PLL是整个芯片的源头,从PLL出来的时钟我们认为就是干净的、后端可以直接用的时钟了。

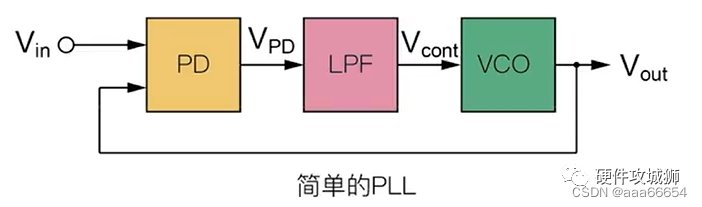

最基本的PLL构成如下:它有一个最主要的元件——压控振荡器VCO,VCO的振荡频率是随着输入电压变化的,它的输出就是整个PLL的输出,也就是我们最终拿到的时钟。

而VCO的输出也会由一个反馈电路接回PLL,经过除频电路得到一个与外部晶振频率差不多的时钟信号,而后比较他们二者的相位。

如果晶振相位稍快,就把VCO输入电压调低,如果晶振相位稍慢,就把VCO输入电压调高,这样就可以根据输入晶振反馈调整VCO的输出,从而得到稳定的高频时钟信号。

这只是PLL基本思想,实际实现起来,需要有一个电荷泵调整VCO的输入,而VCO的输入也需要滤掉谐波,如果不过滤的话反映到最终时钟上就是时钟抖动了。

从上面的简单介绍就可以看出,PLL是一个interwetten与威廉的赔率体系 器件,所以他本质上对噪声和干扰特别敏感,现在做PLL的重要课题之一就是如何减弱噪声影响。

一般后端在物理实现的时候,也会对PLL做额外的特殊照顾,尽量减弱干扰。PLL就类似芯片中的心脏,用以供给跳动的时钟。

但是在数字电路中照顾模拟器件的噪声干扰是十分复杂、困难的一件事,需要考虑很多东西。首先在PLL内部,就需要采用类似差分电路的方法来做VCO,当然这是最基本的,但是更多方法我也不太了解。

在PLL外面,我们也会加很大的blockage,还有加很强壮的shielding等,PG供电也是怎么强怎么来,还有等等一系列额外的QoR检查、ESD检查等。总之一句话,就是会牺牲很大的代价也要把PLL的抗噪声做好。

-

锁相环

+关注

关注

35文章

584浏览量

87744 -

芯片设计

+关注

关注

15文章

1017浏览量

54880 -

VCO

+关注

关注

12文章

190浏览量

69184 -

压控振荡器

+关注

关注

10文章

133浏览量

29291 -

PLL电路

+关注

关注

0文章

92浏览量

6403

发布评论请先 登录

相关推荐

锁相环PLL的噪声分析与优化 锁相环PLL与相位噪声的关系

锁相环PLL在无线电中的应用 锁相环PLL与模拟电路的结合

锁相环PLL与频率合成器的区别

锁相环PLL的工作原理 锁相环PLL应用领域

将 Hercules 锁相环(PLL)咨询SSWFO21#45的影响降至最低

简述锁相环的基本结构

锁相环PLL是什么?它是如何工作的?

锁相环PLL是什么?它是如何工作的?

评论