最近接触到TSMC的后端流程,其中关于基本单元的文件中提到了关于建立时间和保持时间的测量方法,现记录一下自己的理解,目前我还是学生知识储备有限,如果有不对还请同行们指正。

文件提到两种setup/hold测量方式:10% push-up和pass/fail,按照TSMC说法,前者会更乐观一些,因此如果是采用前者(10% push-up)的测量方式得到建立时间和保持时间,需要十份小心时序裕量是否足够,最好人为添加margin。

以下为自己的理解:

10% push-up方式

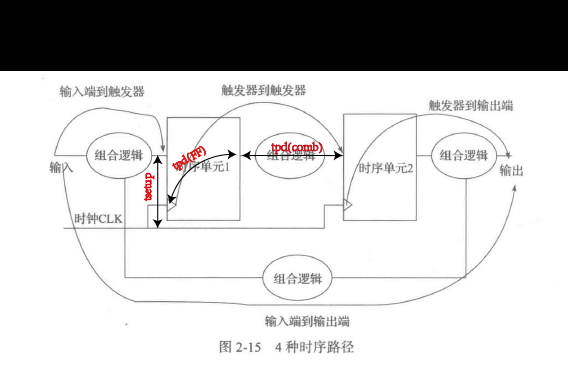

在上图的reg-reg时序路径,关于红色信号: tsetup是为人为控制的值,通过调节该值测量建立保持时间;tpd(FF)为clock到Q的延时,该值会随着D端信号的稳定时间的减小而增加; tpd(comb)是组合逻辑延时,为固定值。三个时间相加就是该路径能运行的最快频率。

tcycle = tpd(FF) + tpd(comb) + tsetup

上图中,x轴为人为控制的tsetup,y轴为clock到Q的延时tpd(FF),当人为给定的tsetup很大时,tpd(FF)时间近似等于STA的时间,随着tsetup时间越来越小,D端的数据稳定时间会“越来越短”,因此tpd(FF)的时间会增加(个人理解是因为亚稳态导致D端的数据不能稳定到固定的值),当tpd(FF)增加到原来的110%时,这时给的tsetup就会被认为是建立时间set up time。

pass/fail方式

而pass/fail是通过调整认为给定的setup/hold,去看输出Q端的电压波动,当电压波动超过10%的临界点,就被认为是建立时间/保持时间。

审核编辑:黄飞

-

TSMC

+关注

关注

3文章

177浏览量

84495 -

组合逻辑

+关注

关注

0文章

47浏览量

10038 -

电压波动

+关注

关注

0文章

51浏览量

8014

发布评论请先 登录

相关推荐

芯片设计进阶之路—从CMOS到建立时间和保持时间

使用采样保持威廉希尔官方网站 实现运算放大器建立时间测定

建立时间和保持时间讨论

保持时间与建立时间

为什么触发器要满足建立时间和保持时间

使用采样保持威廉希尔官方网站 实现运算放大器建立时间测定

PCB传输线建立时间、保持时间、建立时间裕量和保持时间裕量

关于建立时间和保持时间的测量方法

关于建立时间和保持时间的测量方法

评论