数字前端设计人员的目标是使用最小的PA达成要求的PF

时间也是一种消耗(PA)

1.PPA到PA和PF

PPA是数字IC设计逃不开的概念,分别是P(Performance)、P(Power)和A(Area),分别代表芯片的性能、功耗和面积。从产品的角度看来,就是用户基于这块芯片能获得什么(Performance),购买成本是多少(Area),使用成本是多少(Power)。我更倾向于将其拆分为两类,即PF和PA,分别代表功能和消耗:

*PF:即性能(Performance)和功能(Function),这里将原始的Performance拆分为两个部分。功能(Function)是定性的,即这块芯片支持什么功能,性能(Performance)是定量的,表示这块芯片这个功能支持的怎么样,这两个指标用来衡量芯片的能力。

*PA:即功耗(Power)和面积(Area),这里使用的就是原始的P和A概念,这两个指标用来衡量芯片的消耗。

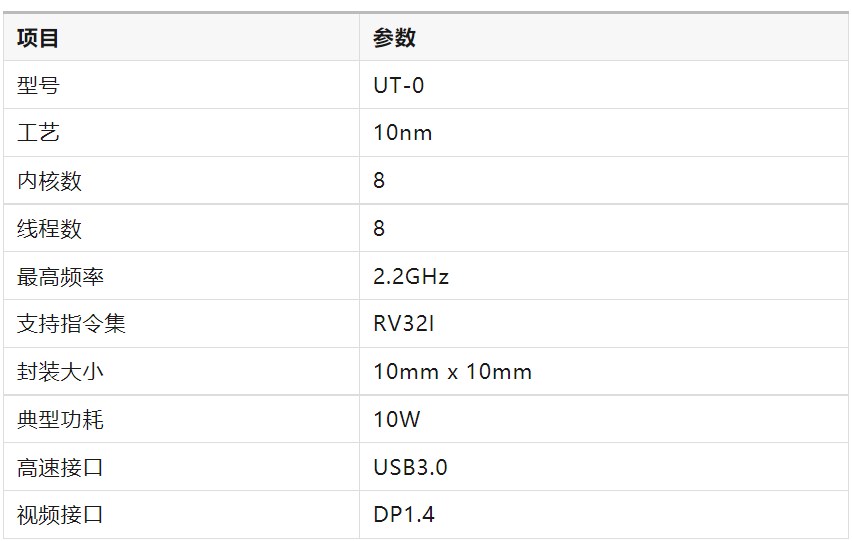

我们简单的来看一下一块虚构CPU的简介,如下表所示:

其中,型号、工艺属于基本信息,而内核数、线程数、频率属于Performance信息,即定量的用于描述性能的信息,以频率为例,在同架构下和核心、线程数下,一般频率高的性能高,最高频率2.2GHz的性能一般高于1.1GHz,但是不影响支持相同的功能,可能仅是运行时间更长。而支持指令集、高速接口、视频接口属于Function信息,以指令集为例,这里就不支持RV32E的指令,RV32E指令在这里无法正常运行。而封装大小属于Area、典型功耗属于Power,这些描述了芯片的消耗,一般来说和售价、散热成本、使用成本挂钩。

2.PA和PF的取舍

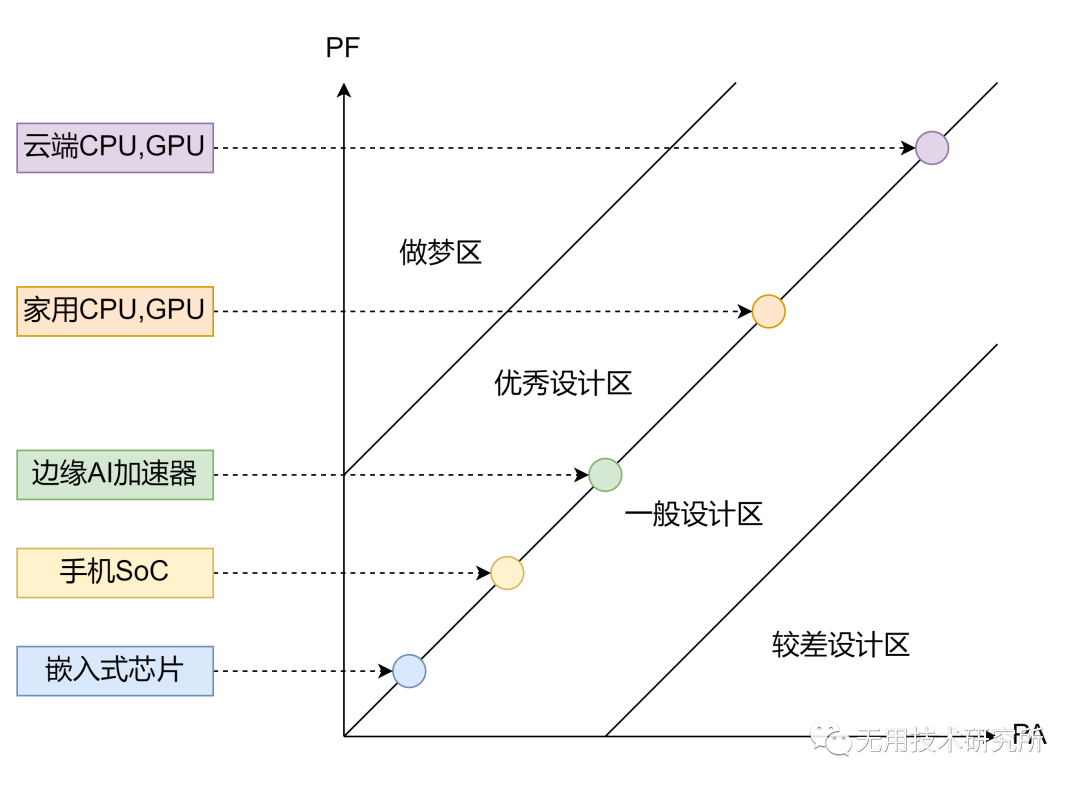

对于PA和PF,不同类型的芯片有不同的取舍,如下图所示:

真正的高性能低功耗芯片是不存在的,性能的提升必定伴随消耗的增加,在前摩尔时代,这些消耗可能被工艺的迭代抵消,但后摩尔时代随着工艺迭代放缓,PA和PF的关系越来越成正相关,甚至线性。因此要求芯片规划人员给出更为精确的需求,确定芯片的使用场景,把功耗花在最需要的功能上。

低PA-低PF的常见场景为嵌入式设备,以乐鑫ESP32-C3为例,该芯片定义为“极低功耗SoC”,提供WIFI和蓝牙解决方案,在Active状态的功耗约为1W,有单核RSIC-V核心,频率160MHz,WIFI支持2.4G。而高PA-高PF的典型场景为云端设备,以英特尔至强W-3365为例,其TDP达到了270W,封装面积为77.5mmx56.5mm,建议售价来到3851美元,而换来的是32核64线程,可支持4TB内存、64条PCIe通道的性能。

3.设计人员眼中的PPA(PAPF)

对于数字前端设计人员,一般会固定PA或PF中的一个进行设计:

*固定PA:给定消耗(例如硅片面积)要求达到最高的性能(例如算力),这种设计模式一般出现在国内科研性质的项目中,尤其常见于MPW模式下的科研性质芯片。在这种模式下每个芯片分到的硅片面积是固定的,一般芯片设计的主导者(一般为教授或研究员)会要求设计人员(一般是学生)在固定的面积下创新架构或微架构,以达到更高的性能。

*固定PF:给定性能(例如支持能力)要求达到最少的消耗(例如功耗),这种设计模式是常规的商业化项目使用的模式。芯片规划者和设计者处于不同的角色,芯片规划者基于当前的市场等多种因素规划芯片的应用场景,再反推出芯片的规格,给设计人员提供需要支持的功能、性能限制和消耗限制。设计人员需要基于芯片需求进行设计,以最小的代价达成需求规划人员给出的各项需求

固定PF的方式我认为是更加合理的方案,所以对于设计人员而言,核心竞争力是使用更少的PA实现规定的PF;对于超出需求的PF,则不是硬需求,超出的PF一般也会带来额外的PA,是否应用也需要由芯片规划人员进行决策。

4.PA的组成和时间消耗

一个芯片的PA由以下几个部分组成:

1.由需求规定的PF引入的PA:这部分是固定需要引入的,优秀的架构、微架构设计和实现方法可以降低固定PF下的PA消耗

2.由于更高PF引入的PA:这部分是否引入需要芯片规划人员进行决策,更高的PF带来的竞争优势可能被PA的增加冲抵

3.物理性PA消耗:由时钟树、复位树、供电部分引入的PA消耗

4.质量性PA消耗:用于提高设计质量的PA,例如DFT、MBIST等标准化测试电路,自定义测试接口,Debug信号,保护电路等用于提升质量带来的PA消耗

5.时间性PA消耗:由于使用IP、代码复用引入的PA消耗,后文会详细描述

6.物理设计PA消耗:由后端人员引入的PA消耗,一般为前端不可见内容,例如由于绕线资源不足产生的额外面积等

对于前端设计人员来说,主要的工作是权衡1、2、4、5四个点。需要注意的是设计时间在广义上也是一种成本,随着摩尔定律放缓,一代架构一代工艺的升级道路已经越来越艰难,对设计的迭代速度也提升了要求,现在流行的先进封装、chiplet、IP、硬件敏捷开发都从不同的角度提升了设计的迭代速度。

以IP为例,对于类似的功能,使用IP和定制代码实现相同的PF,IP消耗的PA一定大于等于定制代码,但是对于一个IP能覆盖的多个类似的功能,如果都使用定制代码开发,会引入额外的时间消耗(包括设计实现消耗和验证时间消耗),因此很多情况下会使用IP以一定的PA为代价,降低硬件的开发时间。

-

IC设计

+关注

关注

38文章

1296浏览量

103959 -

MPW

+关注

关注

0文章

11浏览量

10841 -

PPA

+关注

关注

0文章

21浏览量

7496 -

ESP32

+关注

关注

18文章

971浏览量

17277 -

RSIC-V

+关注

关注

4文章

14浏览量

6537

发布评论请先 登录

相关推荐

弃子争先”与“田忌赛马”:中国数字前端EDA如何加速发展

数字前端生存指南—PPA

数字前端生存指南—PPA

评论