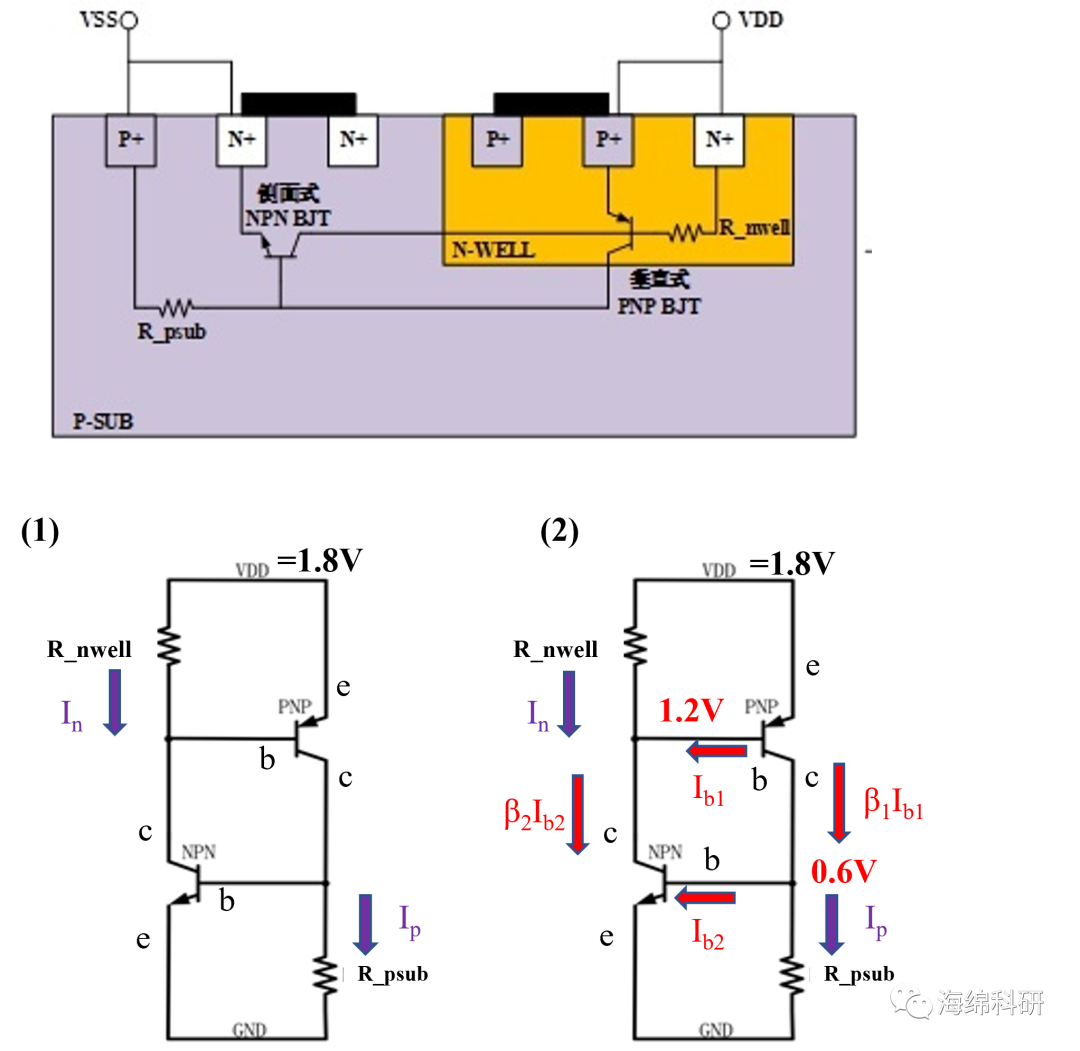

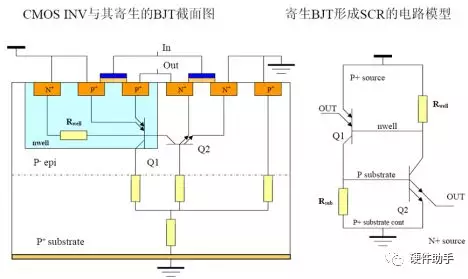

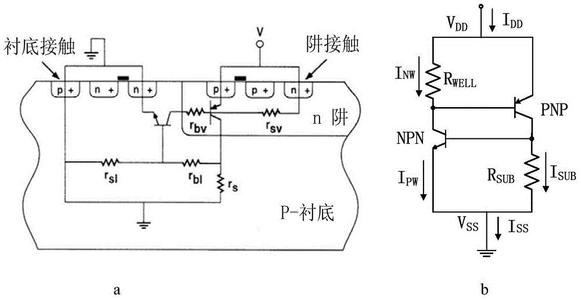

一、闩锁效应:实际上是由于CMOS电路中基极和集电极相互连接的两个BJT管子(下图中,侧面式NPN和垂直式PNP)的回路放大作用形成的,在两个管子的电流放大系数均大于1时,电流在这两个管子构成的回路中不停地被放大,从而导致管子承受的电流过大而烧毁芯片的一种现象。

二、闩锁效应的原理分析:

状态一:假设在N阱或者Psub中由于外界的原因产生了载流子注入,电流分别为In和Ip, 且InR_nwell=0.6,IpR_psub=0.6(假设PN结的导通电压<0.6)。

状态二:在所设压降下,PNP的基极电位为1.2V, 集电极电位为0.6V, NPN的基极电位为0.6V, 集电极电位为1.2V,此时PNP和NPN的发射结都正偏, 集电结都反偏。从而两个BJT管子可进行电流放大,PNP产生了基极电流Ib1, 则集电极电流IC1=β1Ib1, NPN产生了基极电流Ib2, 则集电极电流IC2=β2Ib2。

在近似状态下,Ib1=β2Ib2,Ib2=β1Ib1,因此在后面的循环中,NPN的集电极电流作为PNP新的基极电流进行电流放大,PNP的集电极电流作为NPN新的基极电流进行放大。多次循环之后,电流会被持续放大。

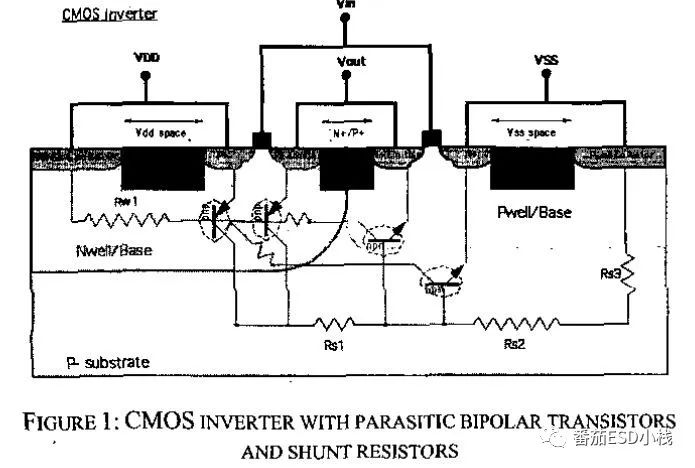

三、闩锁效应的抑制方法(部分方法):

1.拉开NMOS和PMOS的间距:破坏电流循环中的一环,使侧面式NPN BJT管子的基区变厚,载流子的收集变的困难,很难进行电流的放大。

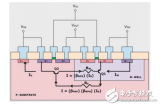

2.使用Guard ring,衬底电位接出的部分采用环形绕线: 降低VDD和Vss的导通电阻,也即降低Rwell和Rsub的阻值,防止BJT的基极和集电极电位相等,破坏BJT导通的条件。

3.Substrate contact和well contact应尽量靠近source: 缩短了Rwell和Rsub的电阻的长度,减小了其电阻值。

-

CMOS电路

+关注

关注

0文章

49浏览量

11507 -

VDD

+关注

关注

1文章

311浏览量

33193 -

闩锁效应

+关注

关注

1文章

29浏览量

9384 -

PNP管

+关注

关注

1文章

28浏览量

7432 -

基极电流

+关注

关注

1文章

31浏览量

3220

发布评论请先 登录

相关推荐

CMOS的闩锁效应:Latch up的原理分析

浅谈IGBT的闩锁效应

什么是闩锁效应?

寄生电路的效应:Latch-Up(锁定)

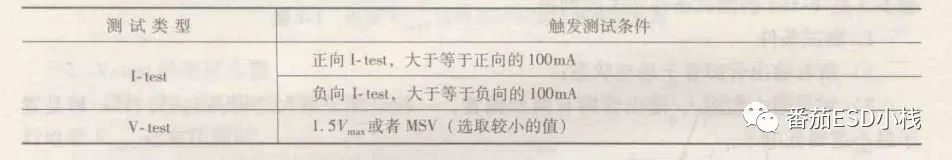

静电放电/过度电性应力/闩锁试验 (ESD/EOS/Latch-up)

ESD/Latch-Up Considerations wi

Latch-Up White Paper

Latch-Up白皮书

避免电路中闩锁效应的3个实用方法!

浅谈Latch-up(二)

闩锁效应(Latch-up)原理及其抑制方法解析

闩锁效应(Latch-up)原理及其抑制方法解析

评论