本文总结和更新了DRAM的产品、发展和威廉希尔官方网站 趋势。

DRAM制造威廉希尔官方网站 进入10nm世代(不到20nm世代)已经过去五年了。过去五年,DRAM威廉希尔官方网站 和产品格局发生了巨大变化。因此,本文总结和更新了DRAM的产品、发展和威廉希尔官方网站 趋势。

DRAM 并不是小型化背后的驱动力

在半导体制造威廉希尔官方网站 的发展中,DRAM在2000年之前一直是小型化的推动力。他们也被称为“流程驱动者”。然而,到了2000年代,情况开始发生变化。NAND闪存(当时的平面存储器)积极推动了制造威廉希尔官方网站 的小型化。微细加工的主导地位将被NAND闪存取代。

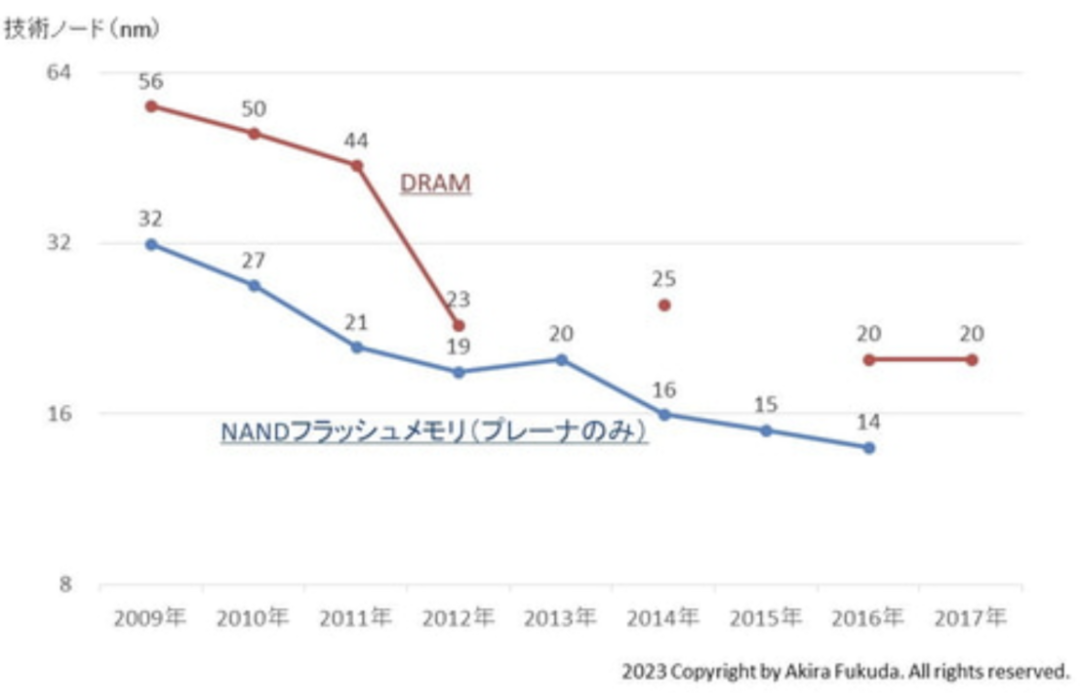

最新的开发成果(原型芯片)在ISSCC(每年二月在美国旧金山举行)上展示,ISSCC是半导体研发界最知名的电路威廉希尔官方网站 国际会议。2009年至2011年,DRAM的威廉希尔官方网站 节点(最小加工尺寸)为56nm至44nm,而NAND闪存(平面型)约为其一半,为32nm至21nm。

DRAM 和 NAND 闪存的威廉希尔官方网站 节点(仅限平面)。

一直处于小型化前沿的NAND闪存在2015年左右达到极限,之后放弃了加工尺寸的小型化,转而采用三维层压。NAND闪存的小型化几乎已经停止,从2010年代后半段开始,DRAM将再次推动小型化。

在半导体逻辑中,“威廉希尔官方网站 节点名称”与物理尺寸不同

然而,在2000年之前,DRAM正在推动整个半导体(半导体存储器和半导体逻辑)的小型化,而在2010年代末到2020年代初,DRAM推动半导体逻辑小型化的进程变得缓慢。主要有两个原因。

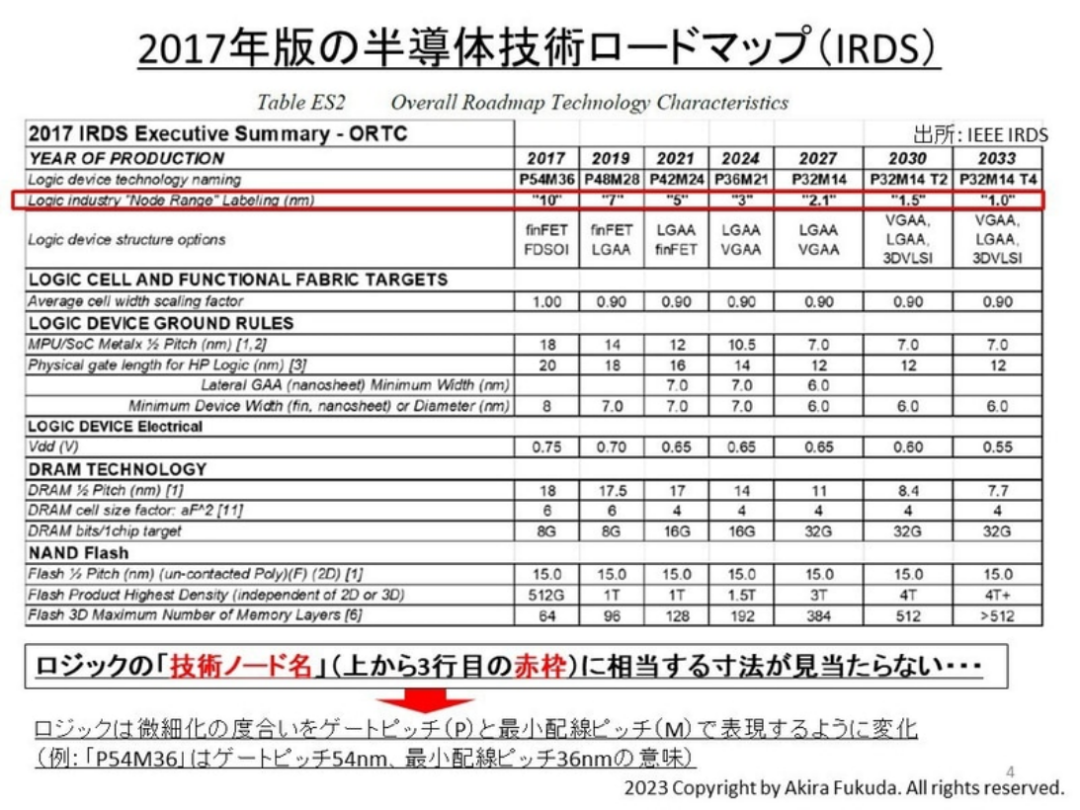

第一个是半导体逻辑中晶体管的三维化。随着MOSFET从平面结构转变为三维FinFET,曾经作为小型化指标的栅极长度(或沟道长度)不再具有任何定义意义。相反,小型化程度主要由标准单元(逻辑单元的最小单位)的栅极节距和最小布线节距决定(严格来说是两者的乘积)。“7nm”、“5nm”等数值,作为尖端逻辑的“威廉希尔官方网站 节点名称”只是一个标签,在硅芯片中并不存在。

半导体威廉希尔官方网站 路线图 (IRDS) 2017 版。从上方预测逻辑、DRAM 和 NAND 闪存的寿命和尺寸。可以看到,找不到半导体逻辑威廉希尔官方网站 节点名称(红框)对应的维度。

另一个问题是半导体逻辑和DRAM的器件和工艺威廉希尔官方网站 已经变得截然不同。每一代半导体逻辑制造工艺都逐渐改变了晶体管的基本威廉希尔官方网站 ,有时甚至是显著改变。其中包括应变硅、HKMG(高介电常数金属栅极)、FinFET 和 COAG(有源栅极上的接触)。对于多层布线,铜(Cu)布线和低介电常数层间绝缘膜的开发和全面采用。

DRAM“威廉希尔官方网站 节点名称”反映实际物理尺寸

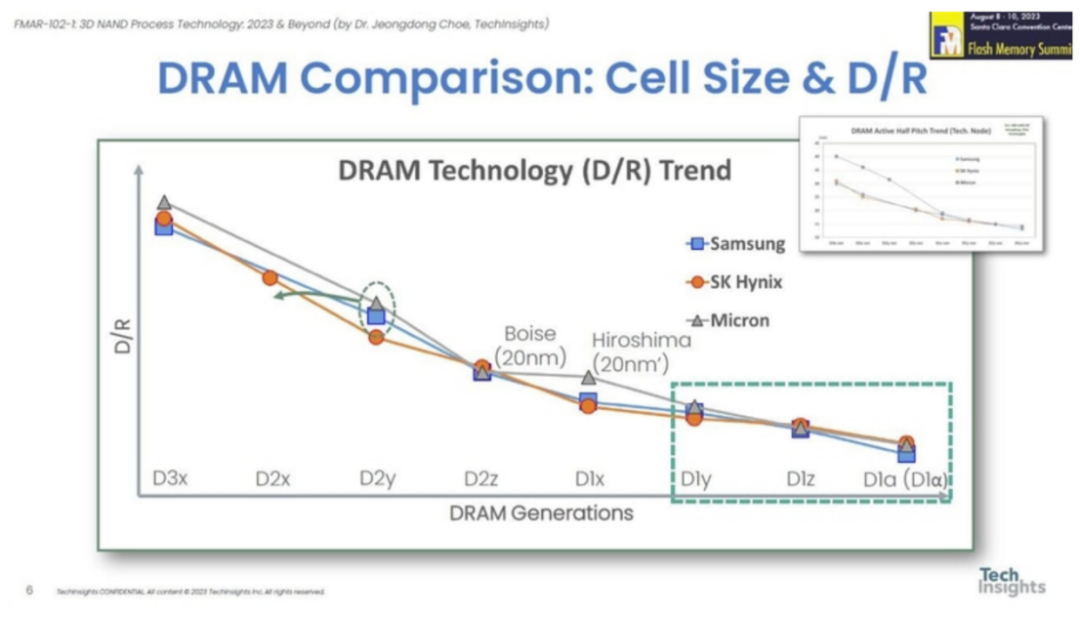

DRAM的“威廉希尔官方网站 负载名称”与逻辑不同,但更接近其实际尺寸。DRAM威廉希尔官方网站 节点名称通常使用符号而不是具体数字来表示。威廉希尔官方网站 节点用符号表示,例如 30nm 代的“D3z”和 20nm 代的“D2x”。

D2x估计在28nm左右,D2y估计在25nm左右,D2z估计在22nm左右。虽然各DRAM厂商威廉希尔官方网站 节点符号对应的数值略有差异,但并无大的差异。

主要 DRAM 威廉希尔官方网站 节点名称与设计规则 (D/R) 之间的关系。可以看出,主要DRAM制造商的

威廉希尔官方网站 节点名称与实际设计规则之间几乎没有差异。来源:TechInsights

威廉希尔官方网站 节点名称对应的维度存在于存储单元阵列的有源区域(单元选择晶体管区域)。有源区域规则排列,排列的一半间距代表威廉希尔官方网站 节点名称。换句话说,在 D1x 代(也称为 18nm 代或 1Xnm 代)DRAM 硅芯片中,单元晶体管以约 36nm 的间距布置。

根据半导体芯片分析服务公司TechInsights发布的预估,2018年12月,三大DRAM公司的D1x代(1Xnm代,半间距)最小尺寸分别为三星电子18nm、SK海力士17.5nm、美光为17.5nm,威廉希尔官方网站 为19nm。几乎没有区别。

DRAM芯片的基本架构

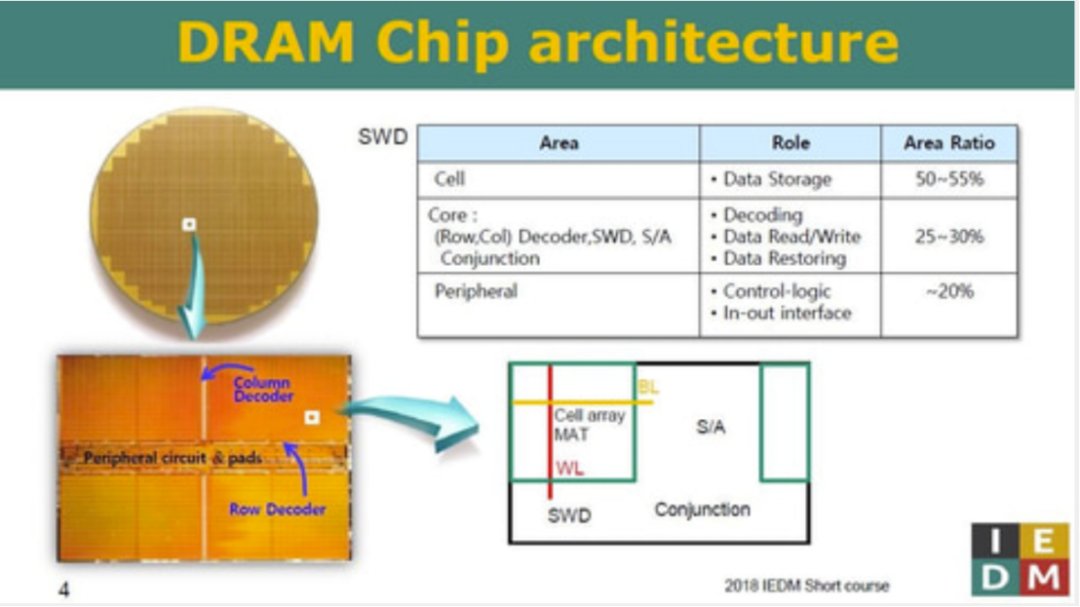

在DRAM制造过程中,许多DRAM芯片被制造在硅晶圆上。从硅晶圆上切下来的单个DRAM芯片被分为存储单元阵列(通常由偶数个子阵列组成)和外围电路(外围)区域。

存储单元阵列,即DRAM的存储区域,逻辑上形状像一个二维矩阵。由多行和多列组成的矩阵的交集(方格)是一个存储单元,行号和列号是指定存储单元(棋盘的方格)的地址。

这里,行号被称为“行地址”并且列号被称为“列地址”。存储单元阵列区域分为“存储单元”和“核心”。存储单元是存储信号的区域,由1个晶体管(MOS FET)和1个电容器(单元电容器)组成。核心是从存储单元阵列中选择目标存储单元并读取或写入数据的电路。“字线解码器”选择单元晶体管的栅极(字线),“位线解码器”选择源极(位线),以及放大用于读取和读取的信号的“读出放大器(S/A)”。写入数据、各部分的互连(布线)等。

外围电路(peripheral)由控制电路和输入输出电路组成。控制电路根据从外部输入的命令和地址来操作DRAM内部的电路。输入/输出电路负责输入(写入)和输出(读取)数据。

解释 DRAM 基本架构的图。来源:三星

左上是硅片照片(实际直径估计为300毫米)。左下角是 DRAM 硅芯片的照片。外围电路、输入/输出焊盘和行解码器位于硅芯片中心的左侧和右侧,列解码器位于中心的上方和下方,存储单元阵列(“子阵列”)位于硅芯片的硅芯片中心的上方和下方。剩余的顶部、底部、左侧和右侧(方形部分)。)被布置。该图的右下角表示存储单元阵列(子阵列)的基本结构。将一个存储单元放置在红色字线 (WL) 和黄色位线 (BL) 的交叉点处。字线的末端连接到子字线驱动器(SWD),并且位线的末端连接到读出放大器(S/A)。该图的右上方显示了每个部分与硅芯片面积的比率。存储单元占50%-55%,核心(解码器、驱动器、读出放大器、互连)占25%-30%,外围设备(控制电路和输入/输出电路)占20%左右。

通过在电容器中存储电荷来存储逻辑值

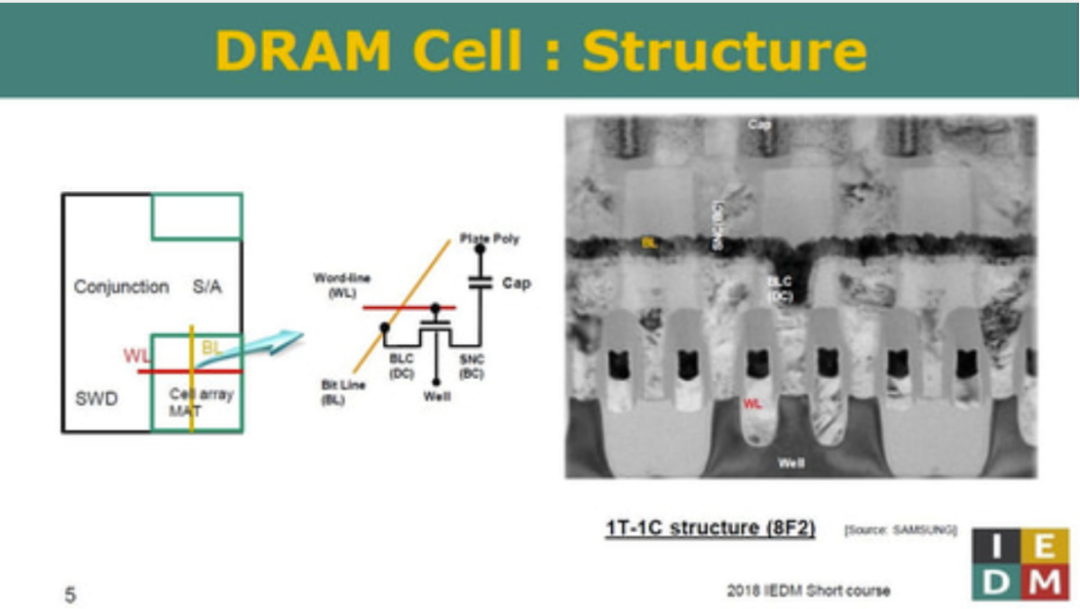

一个 DRAM 存储单元由一个晶体管(缩写为“T”)和一个电容器(缩写为“C”)组成。它在半导体存储器威廉希尔官方网站 界通常被称为“1T1C 单元”。晶体管充当选择开关。也称为“选择晶体管”。在读或写操作中,位于由字线译码器和位线译码器选择的字线和位线交叉处的“选择晶体管”被导通。

存储单元电容器(功能与电子元件的电容器相同)存储信号电荷。也称为“单元电容器”。如果电容器存储一定量的电荷,则存储单元的逻辑值为“高”(或1)。相反,如果仅存储少于一定量的电荷,则存储单元的逻辑值将为“低(或0)”。

DRAM 存储单元电路的示例(左)和使用电子显微镜观察到的存储单元的截面图像(右)。

在左边的电路图中,选择晶体管(通常是n沟道MOSFET)的栅极是字线(红色:WL),源极是位线(黄色:WL)。选择晶体管的漏极通过单元电容器连接到板电极。在右侧的截面观察图中,红色标记为“WL”的部分是选择晶体管(字线)的栅极,BLC是位线触点,SNC是存储节点触点。SNC 上方连接有一个电容器(图中的“Cap”)。SNC 字母左侧的黄色字母“BL”表示位线。

DRAM存储单元的基本操作和刷新

当向 DRAM 写入数据时,解码器打开指定地址处的选择晶体管,输入缓冲器接收外部数据,然后通过读出放大器将其转换为电流,对单元电容器进行充电。

充电后,随着时间的推移,由于电容器放电,写入的数据(电荷)会丢失。因此,有必要定期重写数据。该操作称为“刷新”。2000 年之前,DRAM 由外部内存控制器在适当的时间刷新。最近,很多产品内部都实现了自动刷新操作。

读取数据时,选择晶体管导通,单元电容器中的电荷作为电流通过位线。位线电流被读出放大器(S/A)放大为电压。电压信号通过输出缓冲器发送到外部。

在读取操作期间要记住的一件事是,单元电容器上的电荷会因读取操作而丢失。因此,读出放大器立即恢复(新写入)读取的数据。

2000年代,DRAM存储容量扩张步伐迅速放缓。

2000年之前,DRAM存储容量迅速扩张,尤其是在20世纪70年代和80年代。半导体存储器行业称之为“三年翻两番”,三年内将存储容量提高四倍的下一代DRAM商业化已成为半标准做法。尽管主流用户已经从大型机(1970年代)到工作站(1980年代)再到个人电脑(PC)(1990年代),但情况依然如故:他们期望DRAM制造商在三年内将开发速度翻两番。

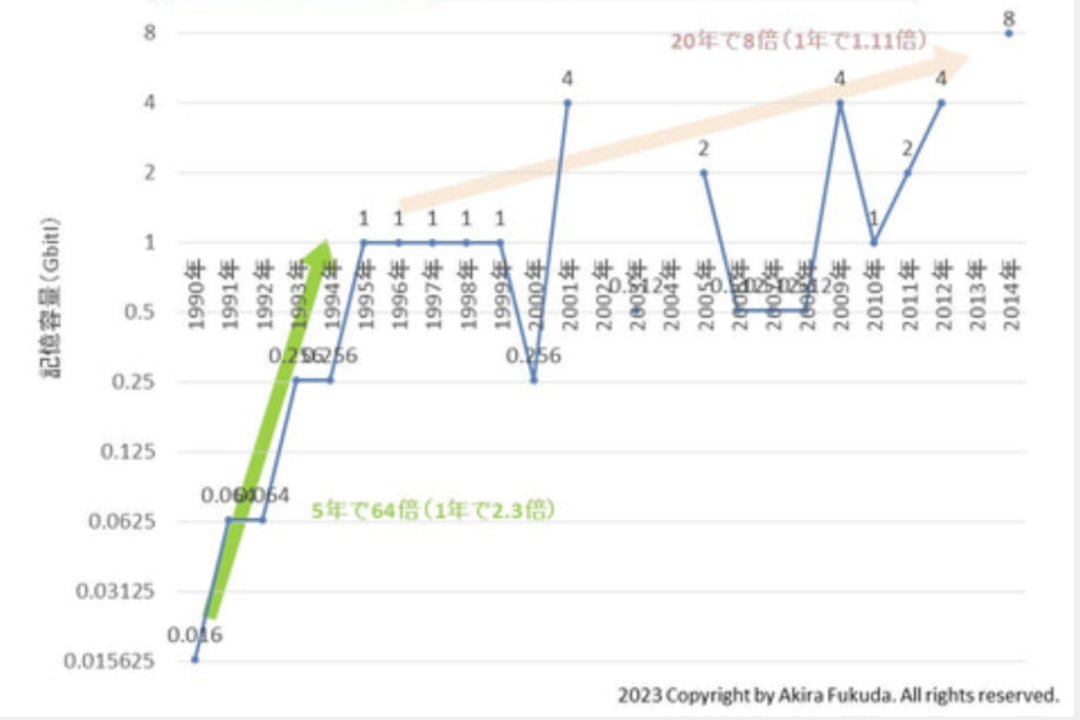

这里我们将从国际会议 ISSCC(每年 2 月举行)上介绍的硅芯片概述开始,了解 DRAM 的发展状况。首先是最大存储容量。20世纪90年代前半期,产能增长速度远远超过“3年4倍(1年1.59倍)”。它从1990年的16Mbit迅速扩展到1995年的1Gbit。“5年64次(1年2.3次)”是一个令人难以置信的快节奏。

然而,1995年后,存储容量扩张的步伐突然放缓。直到 1999 年,最大容量仍保持在 1Gbit。之后在256Mbit、512Mbit、1Gbit、2Gbit、4Gbit之间来回切换。向下一代 4Gbit 的过渡是缓慢的。随着2014年和2016年8Gbit硅芯片的发布,我们现在可以清楚地说,容量的增加比1Gbit一代已经进步了约1.5代。事实上,产能继续以 DRAM 发展史上从未见过的速度扩张,20 年内增长了 8 倍(1 年内增长了 1.11 倍)。

DRAM 最大存储容量(每个硅芯片)的变化(1990-2014 年)。可以看出,从1996年到2012年,增产并没有太大进展(每年扩张1.11倍)。

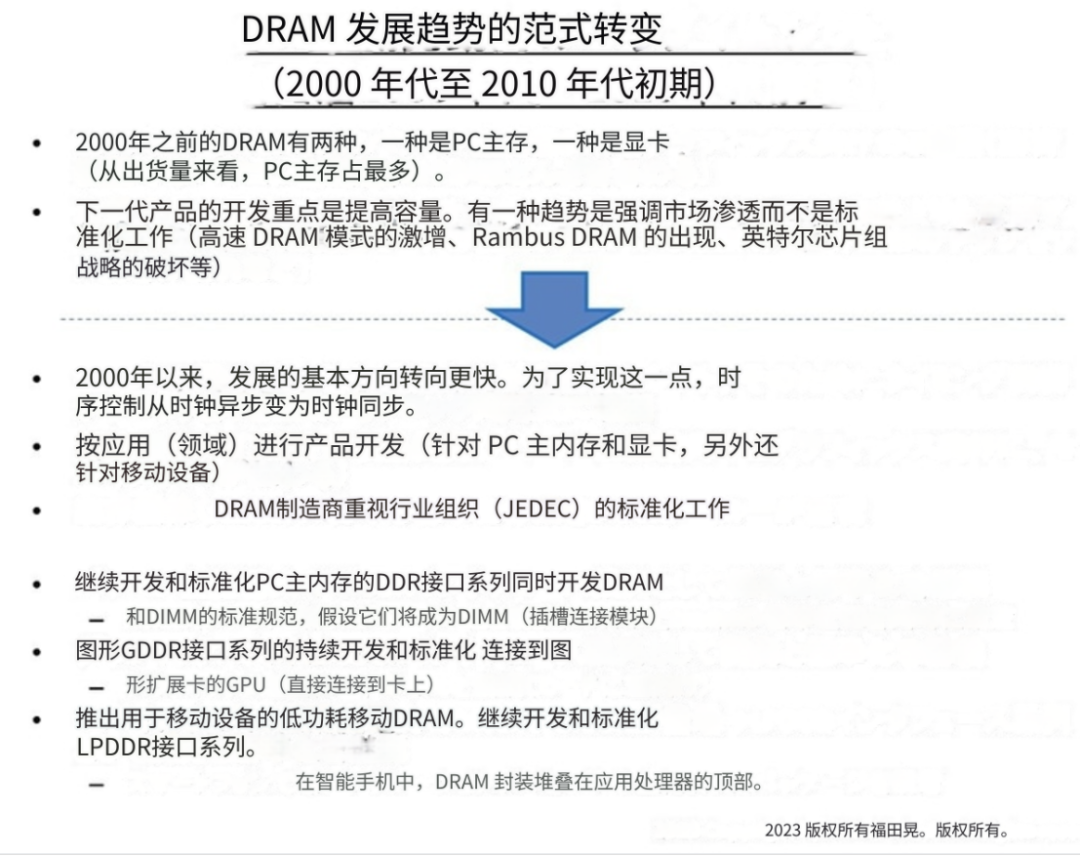

DRAM开发的范式转变

从20世纪90年代末到2010年代初的20年间,DRAM的发展发生了什么?总的来说,可以说开发方向发生了很大变化。DRAM开发的方向从大容量,走向高速化。

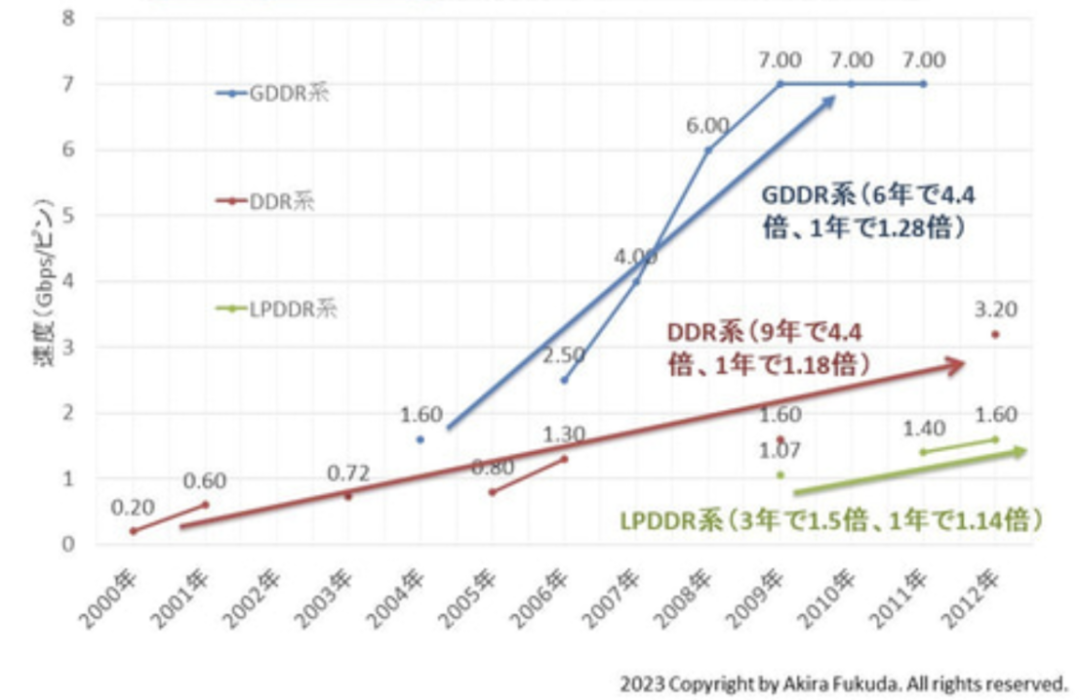

DRAM数据传输速度的推移。

为了高速化,在动作定时控制中采用时钟同步式。最初,为了与传统的DRAM(无时钟异步式DRAM)区别,被称为同步DRAM(SDRAM)。现在,如果简单地记述DRAM,则意味着同步式(或者不知道是同步式还是异步式)。严格来说,DDR、LPDDR、GDDR等DRAM的表述为“SDRAM”是正确的,在产品目录和学会论文等中也有“SDRAM”的表述。

SDRAM的下一代标准规格是出于高速化的强烈意识而制定的。最初的SDRAM以与时钟相同的速度输入输出数据。此时的时钟频率为133MHz.SDRAM的下一代产品成为能够以时钟速度的2倍输入输出数据的规格。这就是所谓的“双数据速率(DDR)SDRAM”。时钟频率提高到200MHz,数据的输入输出速度是时钟的2倍,即400MT/s/输入输出引脚(这里T(transfer)是传输次数的意思)。一次传输中发送接收1比特等于bit/秒)。

DDR系列的SDRAM之后,每代数据的输入输出速度都会提高一倍。在国际学会ISSCC上发表的DDR类SDRAM的数据传输速度在2003年至2012年的9年间提高了4.4倍。

图形DRAM也采用DDR,积极推进高速化。这就是“GDDR(图形DDR)SGRAM(同步图形RAM)”。GDDR类SGRAM的高速化正在迅速推进。在国际学会ISSCC上发表的GDDR系SGRAM的数据传输速度在2004年至2010年的6年间增加了4.4倍。年增长率为1.28倍。

随着移动电话终端和智能手机等的普及,开发了低功耗版SDRAM。最初被称为“移动DRAM”,但后来以“LP(Low Power)DDR SDRAM”的名称进行开发和标准化。2009年,国际学会ISSCC首次公开了LPDDR系的试制硅芯片。由海力士半导体(Hynix Semiconductor)开发的1Gbit芯片,数据传输速度为1.066Gbps/pin。到2012年,LPDDR系统的数据传输速度提高了1.5倍(年速率为1.14倍)。

DRAM开发动向的范式转变。

通过引入时钟同步式设计来实现高速化、不同用途的产品开发,以及考虑不同领域的安装形态(封装和模块)的标准规格的制定等是2000年代以后的DRAM开发策略。大容量化的主要部分将由NAND闪存承担。2005年,根据ISSCC,NAND闪存的存储密度超过了DRAM的存储密度。可以说,这是“大容量为NAND闪存,高速为DRAM”的角色分担越来越强的时代。

-

芯片

+关注

关注

455文章

50732浏览量

423258 -

DRAM

+关注

关注

40文章

2311浏览量

183449 -

半导体制造

+关注

关注

8文章

399浏览量

24067

原文标题:DRAM的范式转变历程

文章出处:【微信号:ICViews,微信公众号:半导体产业纵横】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

DRAM的基本构造与工作原理

东软引领医院智慧服务新范式

DRAM与NAND闪存价格大幅下跌

SRAM和DRAM有什么区别

DRAM存储器的基本单元

DRAM的分类、特点及威廉希尔官方网站 指标

NAND闪存的发展历程

DRAM内存操作与时序解析

DRAM的范式转变历程

DRAM的范式转变历程

评论